#### **TWENTY-FOURTH ANNUAL**

# <u>tentve</u>

ConX

DoubleTree by Hilton Mesa, Arizona March 5-8, 2023

# With Thanks to Our Sponsors!

# With Thanks to Our Sponsors!

## **COPYRIGHT NOTICE**

The presentation(s) / poster(s) in this publication comprise the Proceedings of the TestConX 2023 workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the TestConX 2023 workshop. This version of the presentation or poster may differ from the version that was distributed at or prior to the TestConX 2023 workshop.

The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors. There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation / poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX", the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.

High Speed & High Frequency

# Transmission Line of RF, Serdes I/O Test Hardware Signal Path

#### Noel Del Rio NXP Semiconductor

Mesa, Arizona • March 5–8, 2023

1

High Speed & High Frequency

### TestConX 2023

#### Agenda:

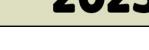

- Signal Path Segments

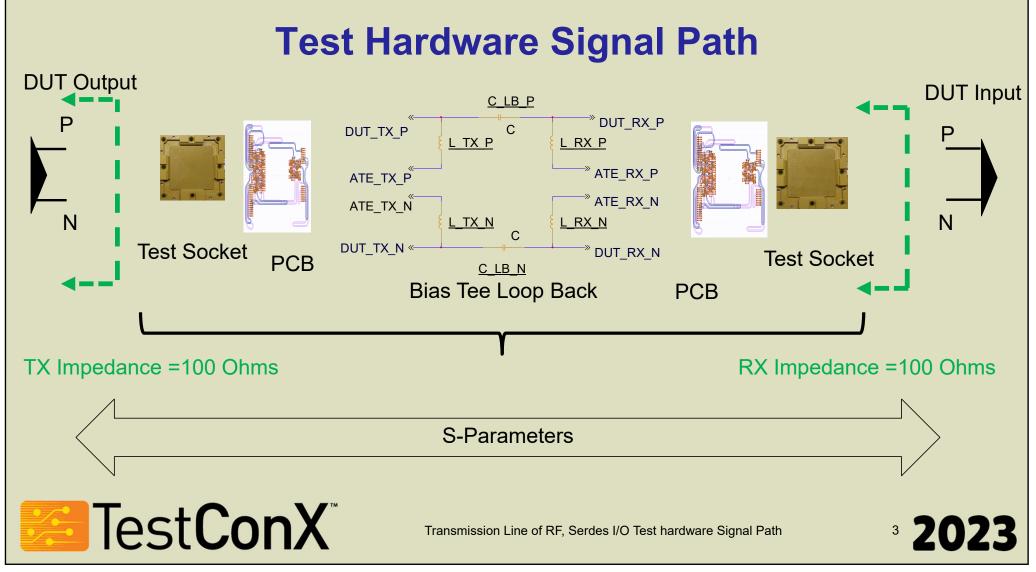

- Serdes Receiver Data Eye Mask

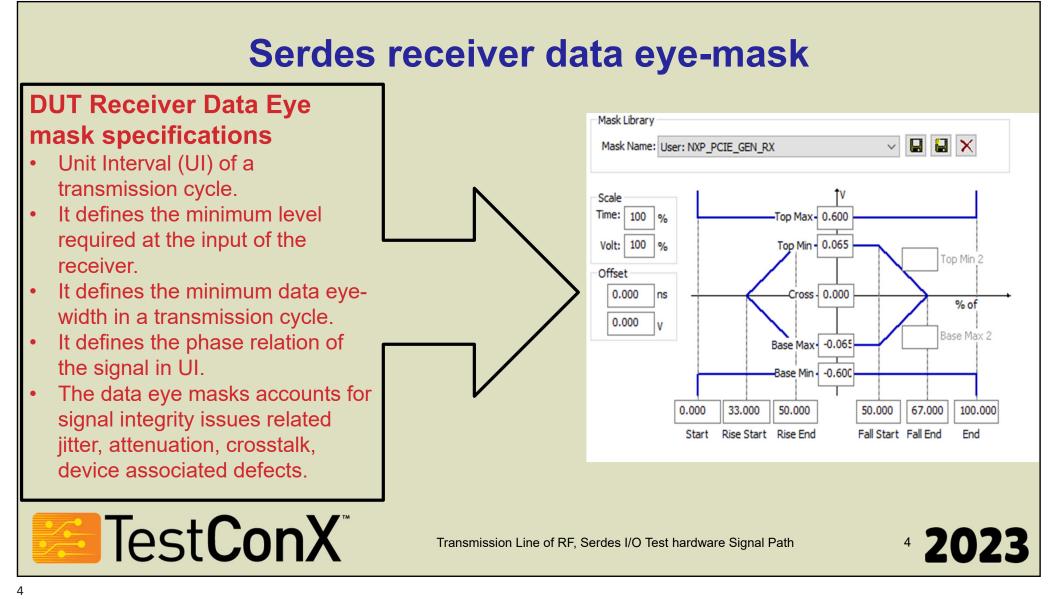

- LC Loop Back

- RC Loop Back

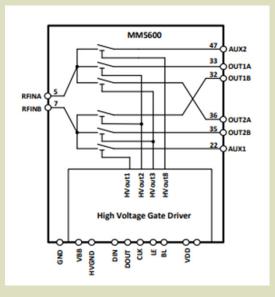

- RF Differential Switch

- Test Socket or Interposer

- PCB and related structures

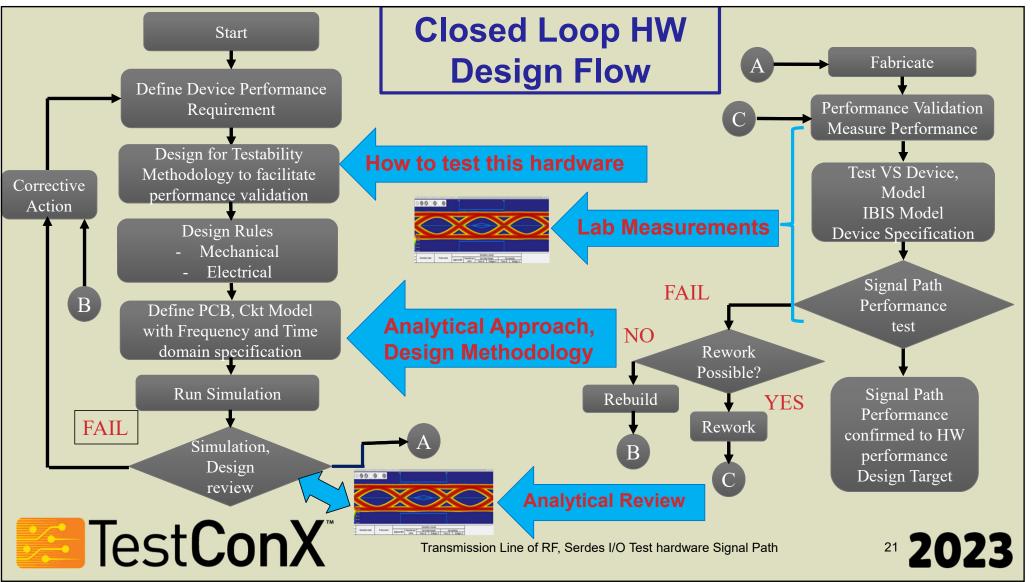

- Closed Loop hardware design flow

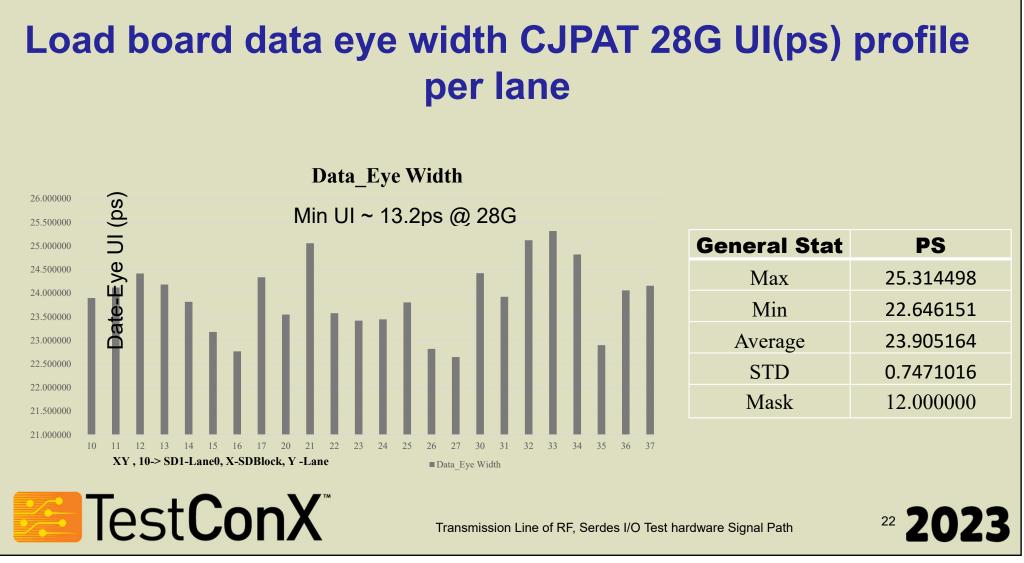

- Test hardware performance measurement results

- Conclusion

Transmission Line of RF, Serdes I/O Test hardware Signal Path

#### TestConX 2023

High Speed & High Frequency

TestConX 2023

High Speed & High Frequency

TestConX Workshop

www.testconx.org

March 5-8, 2023

High Speed & High Frequency

#### TestConX 2023

Session 2 Presentation 2

High Speed & High Frequency

6

High Speed & High Frequency

7

High Speed & High Frequency

High Speed & High Frequency

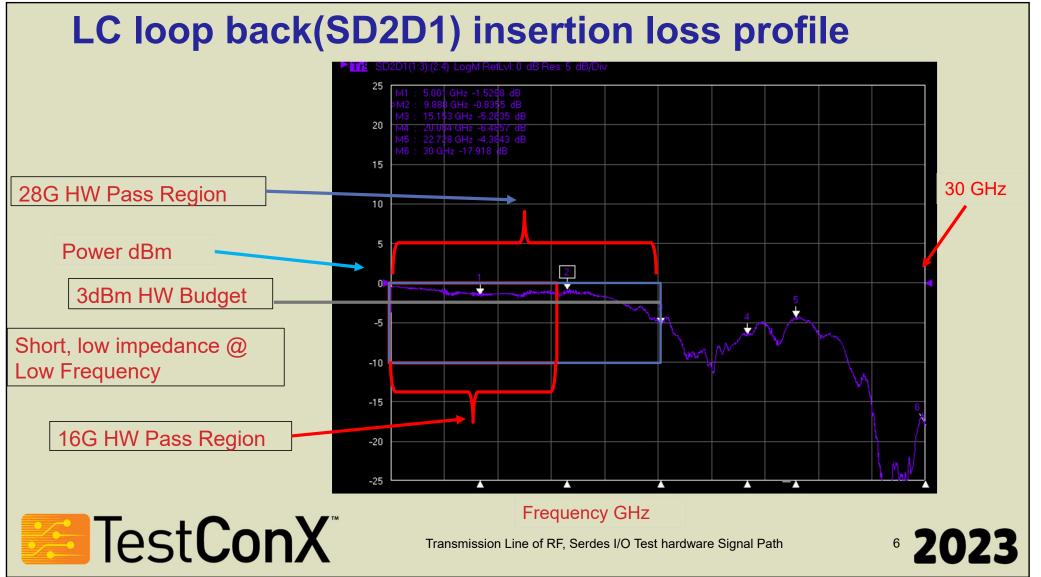

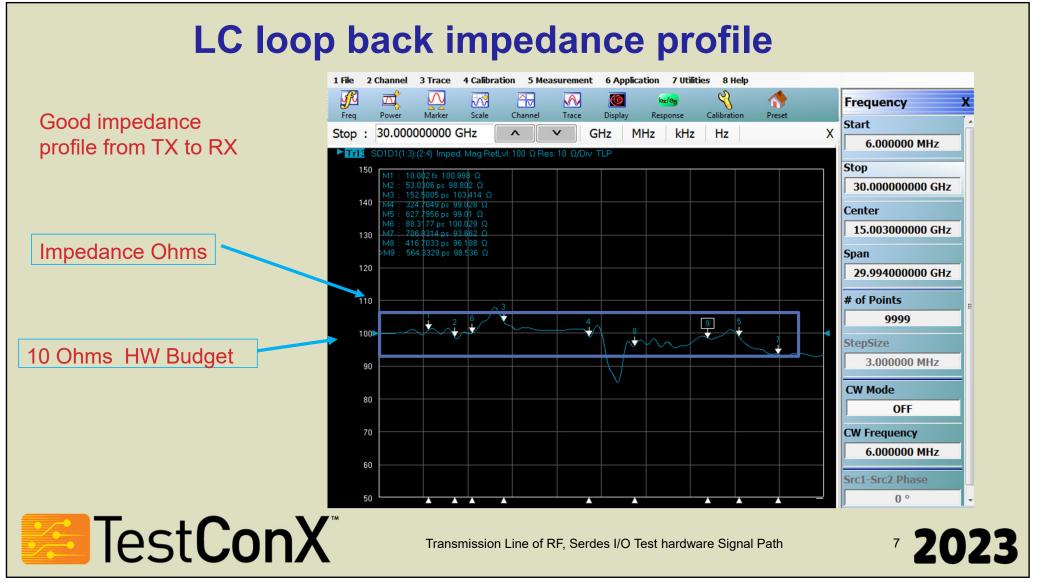

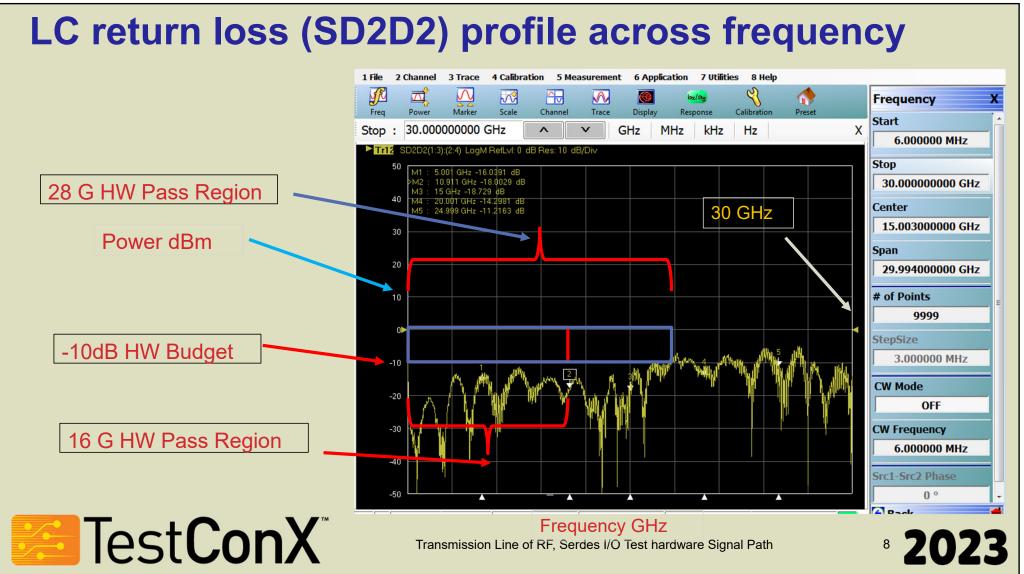

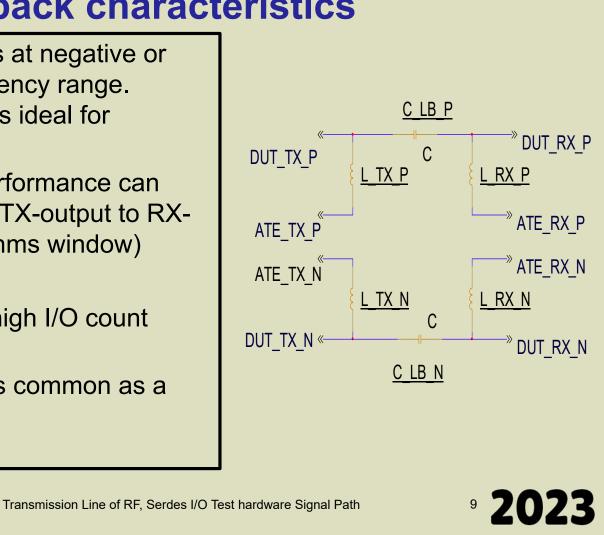

#### **LC loop back characteristics**

- Insertion Loss (S21, D2D1) starts at negative or very low power level at low frequency range. Inductive short at low frequency is ideal for parametric type testing

- Validated inductor broadband performance can contain impedance-change from TX-output to RXinput to required range(e.g. 10 ohms window)

- High reliability loop back circuit.

Test**ConX**

- Next to RC in small footprint for high I/O count devices (e.g. 64 Serdes lanes)

- Coil variability and non-linearity is common as a function of frequency

High Speed & High Frequency

10

TestConX 2023

High Speed & High Frequency

High Speed & High Frequency

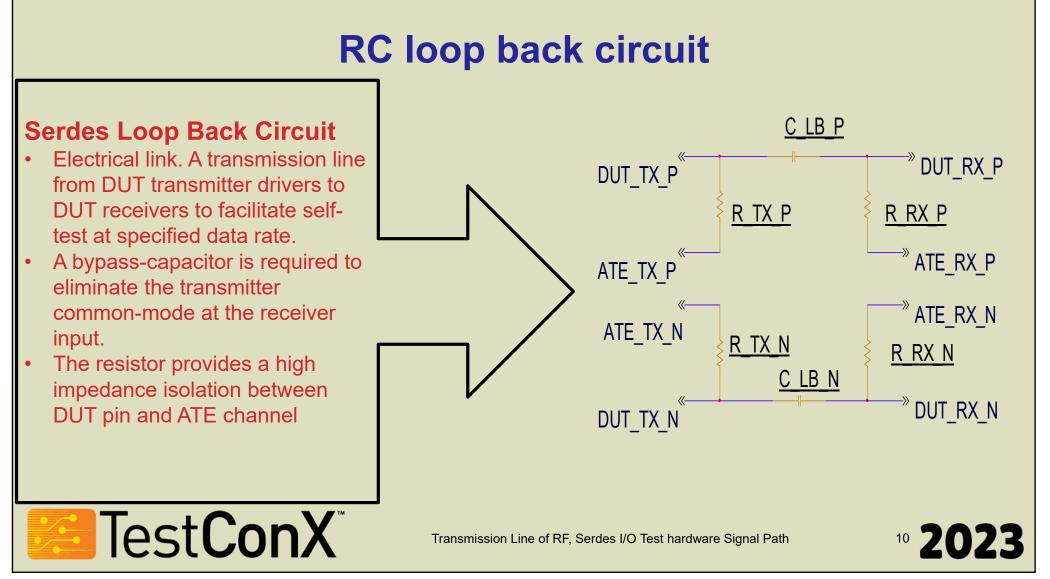

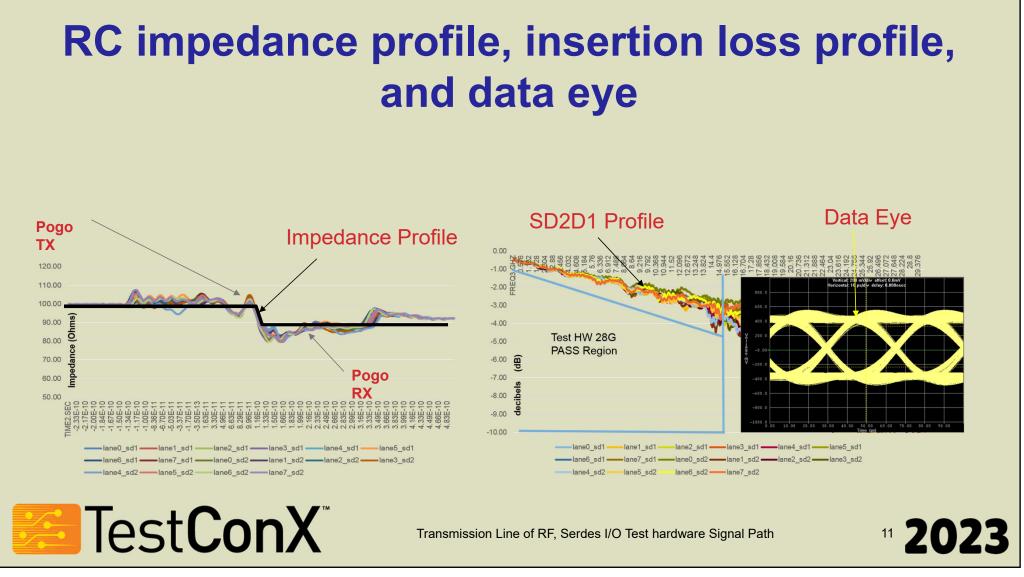

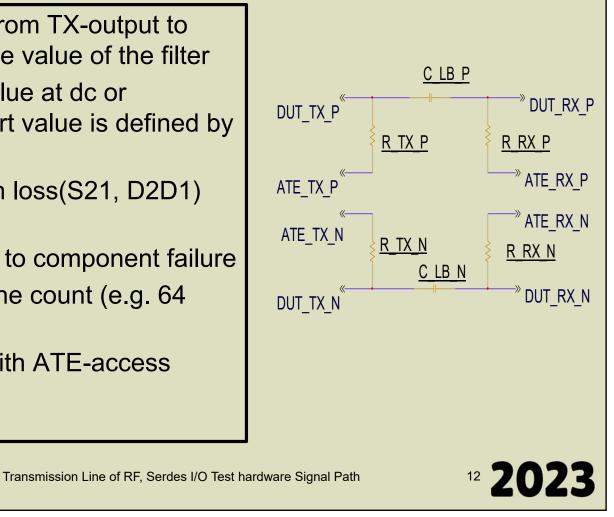

#### **RC loop back characteristics**

- Step function impedance profile from TX-output to RX-input defined by the resistance value of the filter

- Insertion loss starts are preset value at dc or frequency zero. Insertion loss start value is defined by the resistance of the filter

- Excellent linearity for the insertion loss(S21, D2D1) curve

- High reliability and less exposure to component failure

- Small footprint for high Serdes lane count (e.g. 64 lanes)

- Parametric test is a challenged with ATE-access limited by the series resistance

Test**ConX**

12

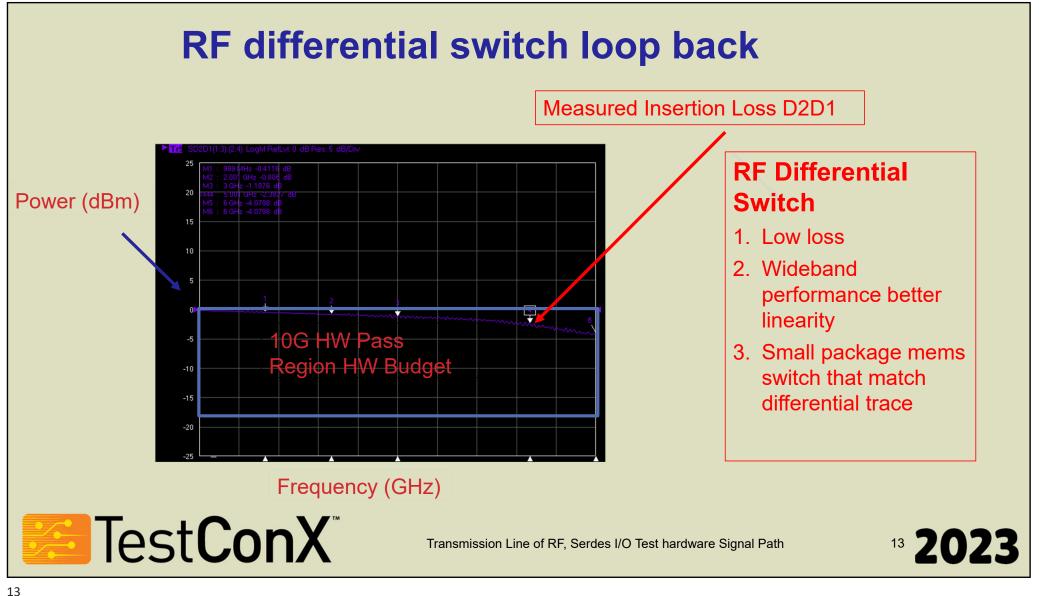

#### **RF switch loop back characteristics**

- Can support functional and parametric test with less constraints

- Broadband performance is dictated by switch specification

- Good Linearity for the insertion loss (S21, D2D1) curve

- RF switch life as declared by vendor

- MEMS RF switch small package footprint is ideal for match differential pair routing that don't require change on trace spacing

Transmission Line of RF, Serdes I/O Test hardware Signal Path

**TestConX 2023**

www.testconx.org

2023

Presentation 2 Session 2

High Speed & High Frequency

#### TestConX 2023

**Test socket or interposer**

#### **Test Socket**

- Electrical connection between the DUT, ATE, and associated resources to facilitate testing.

- A very short transmission line from sub millimeter to less than 4 mm for high data rate application

- The signal path segment that degrades as a function of insertion cycle

- Come in different types like pogo, membrane, coax as a function of application

Transmission Line of RF, Serdes I/O Test hardware Signal Path

15

www.testconx.org

<sup>15</sup> **2023**

High Speed & High Frequency

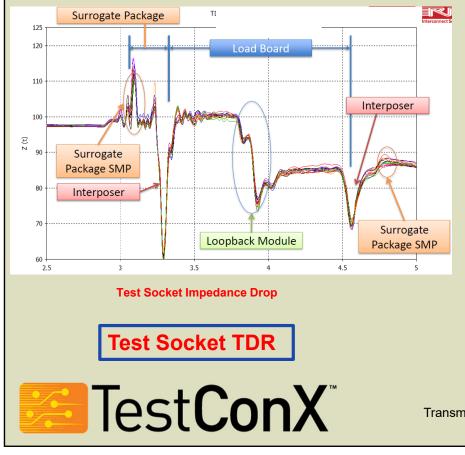

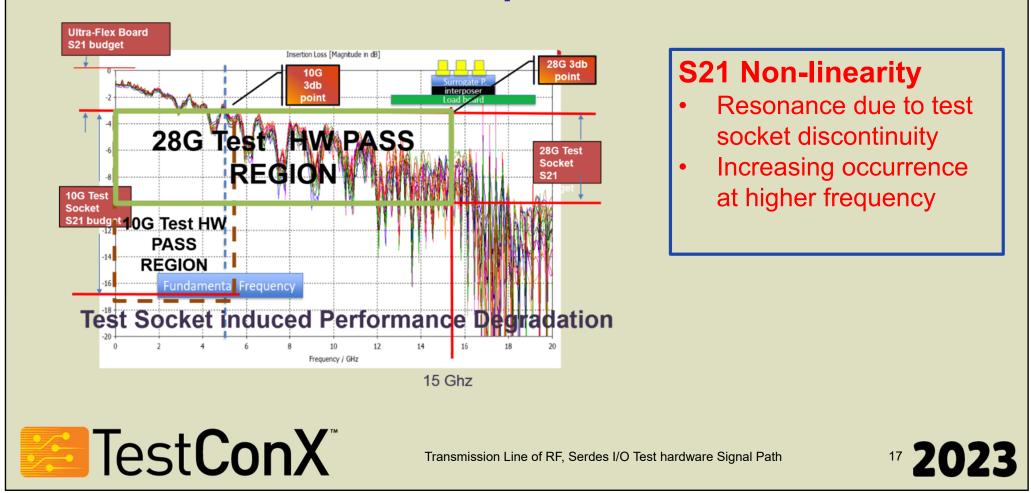

#### Test Socket discontinuity or impedance non- compliance

#### **Test socket discontinuity**

- Measured differential impedance approaching 60 ohms

- It is important to measure test socket compliance to impedance requirements

- Simulation results are not assurance of real-world compliance to specifications.

High Speed & High Frequency

#### Test Socket discontinuity or impedance non- compliance

#### TestConX 2023

High Speed & High Frequency

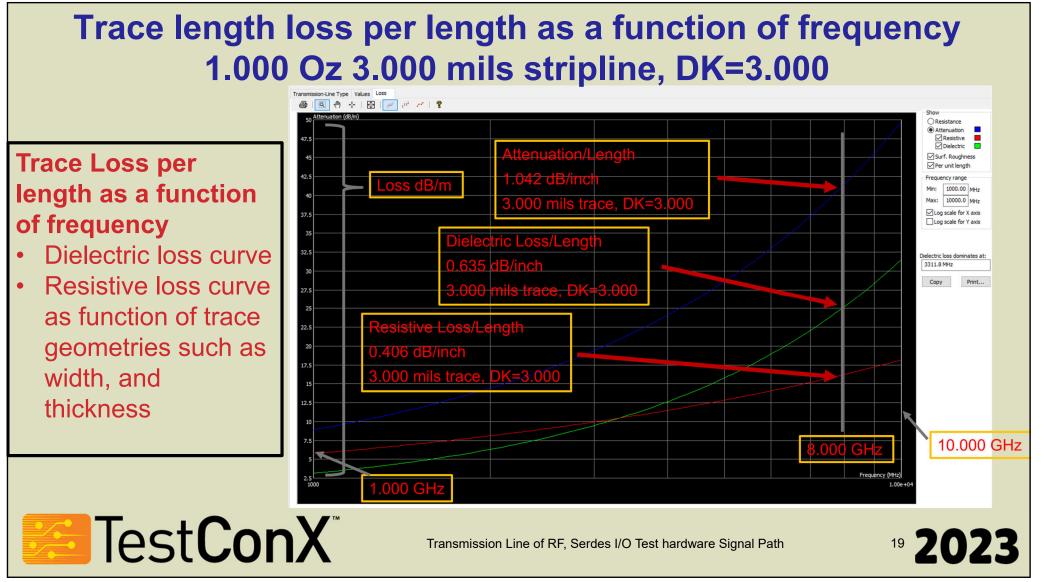

#### PCB(layout, trace, via, pad, dielectric)

#### **PCB**

- Electrical link of the different segment of the signal path

- Physical geometries have profound impact on transmission line performance in frequency and time domain

- PCB Interconnects such as vias, pads are the common source of discontinuity

- Dielectric constant and physical geometries of the structure dominates the signal loss along the signal path

Test**ConX**®

<sup>18</sup> **2023** Transmission Line of RF, Serdes I/O Test hardware Signal Path

#### TestConX 2023

High Speed & High Frequency

High Speed & High Frequency

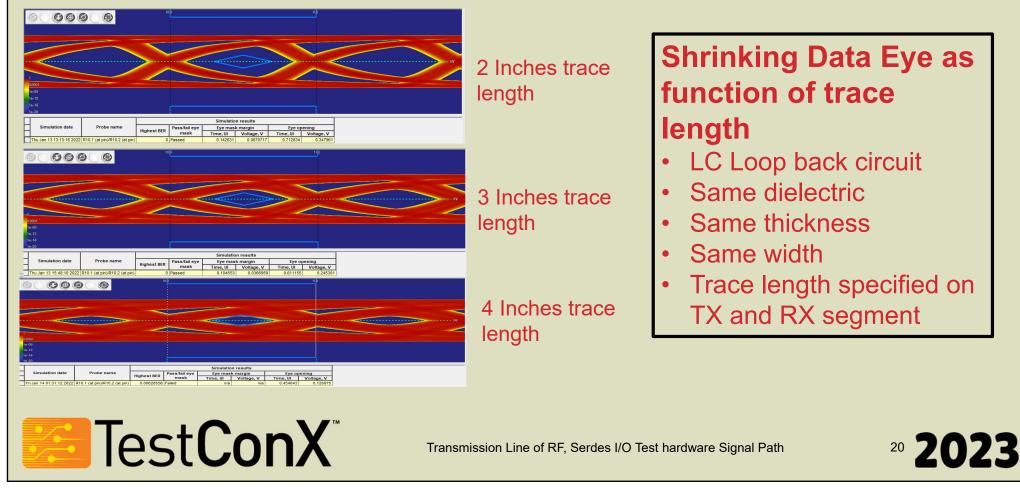

## Transmission line loss using pattern prbs-31 @ 25G Load board Trace length loss at 2,3,4 inches

High Speed & High Frequency

#### TestConX 2023

21

Session 2 Presentation 2

High Speed & High Frequency

High Speed & High Frequency

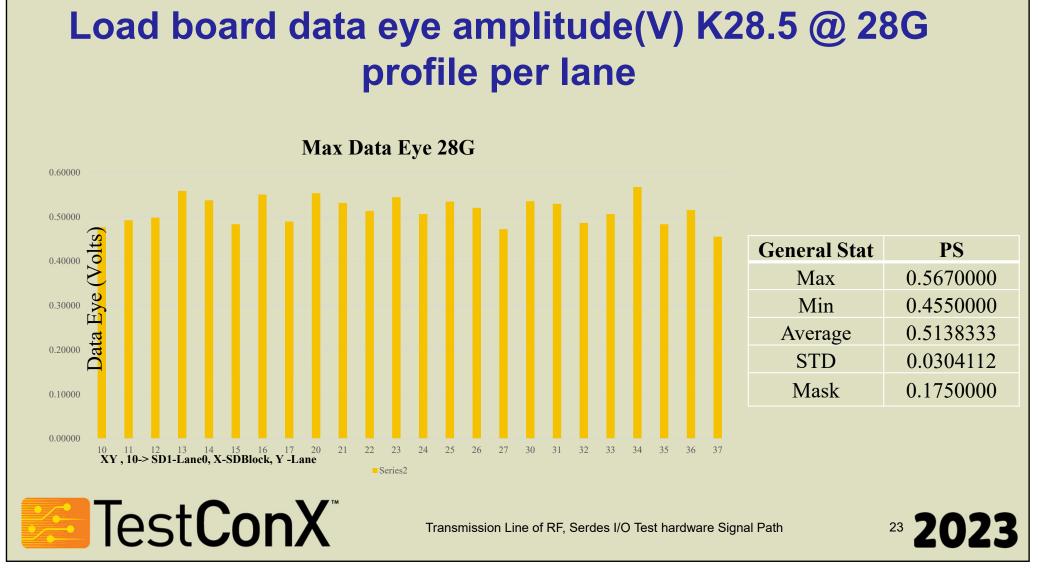

23

High Speed & High Frequency

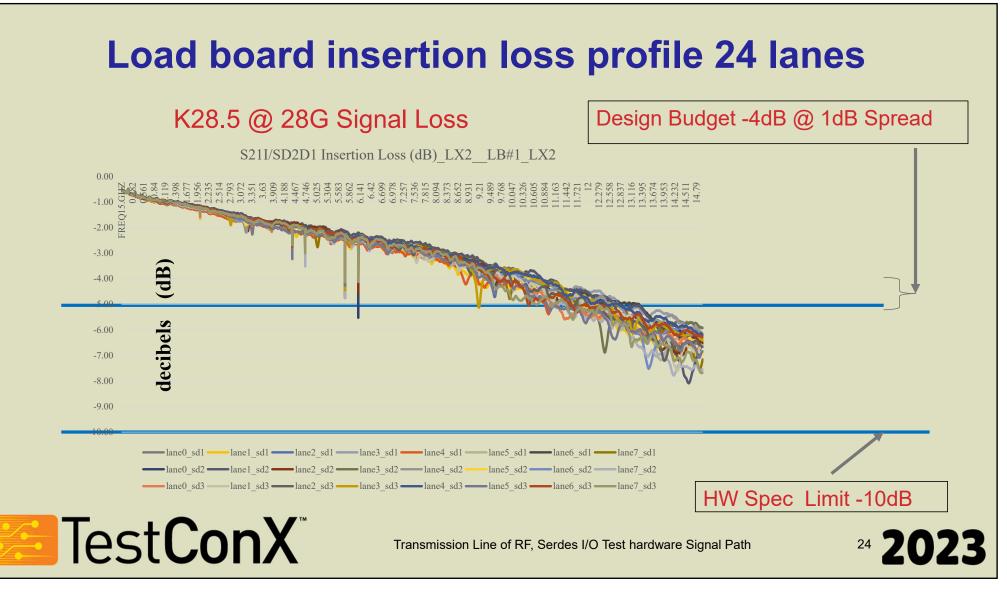

24

#### Conclusion

- 1. Analytical approach to test hardware design provides for objective assessment of the complete signal path. That is on frequency domain, and time domain.

- 2. Closed-Loop test hardware design ensures device signal path capability to meet device performance requirements

- 3. It is an objective process with defined performance target and validated for real-world compliance(Measured).

- 4. Cost effective hardware design and deployment process