#### With Thanks to Our Sponsors!

### With Thanks to Our Sponsors!

**Distinguished**

Industry Partners

#### **COPYRIGHT NOTICE**

The presentation(s) / poster(s) in this publication comprise the Proceedings of the TestConX 2023 workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the TestConX 2023 workshop. This version of the presentation or poster may differ from the version that was distributed at or prior to the TestConX 2023 workshop.

The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors. There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation / poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX", the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.

www.testconx.org

# An Integrated Approach to Testing Analog Sub-Systems in Large Digital "Cheap" SoCs

Thecla Chomicz

NXP Semiconductors

#### **Contents**

- Introduction

- What, Where and How to Test

- Analyze Isolate Access Observe

- Examples of Increasing Analog Coverage

- Debug Modes

- Design for All Types of Test

#### A look back... (device count = 1)

Science & Society Picture Library/SSPL

Nokia Corporation / AT&T Archives

John Bardeen, left, William Shockley, middle (sitting), and Walter Brattain

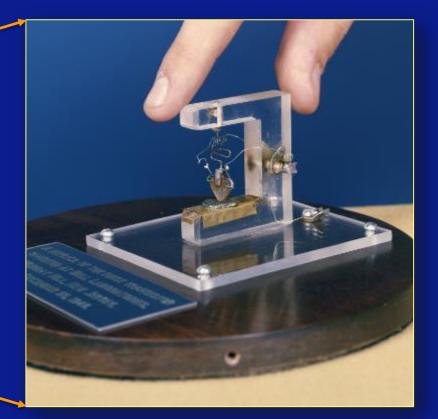

#### **High Speed Serial Evolution**

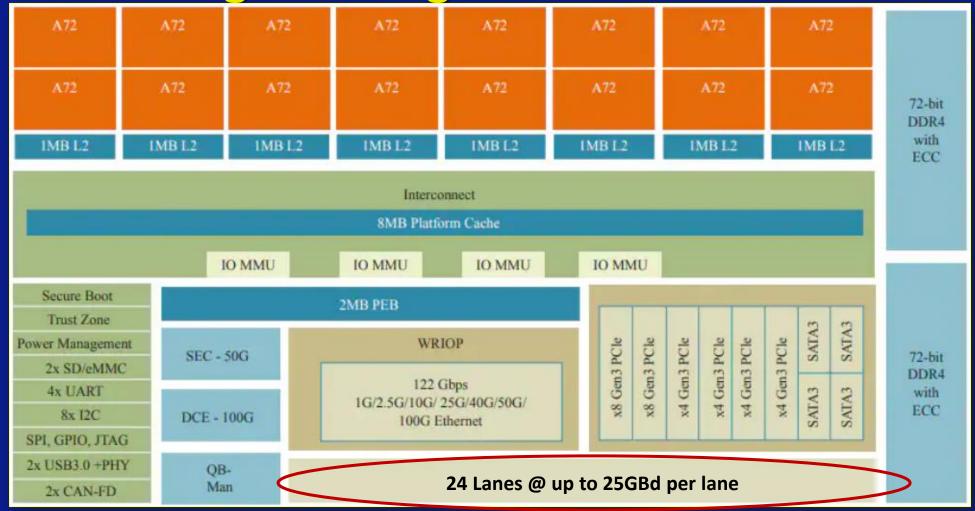

#### Large Analog Block in LX2160

https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/layerscape-processors/layerscape-lx2160a-lx2120a-lx2080a-processors:LX2160A

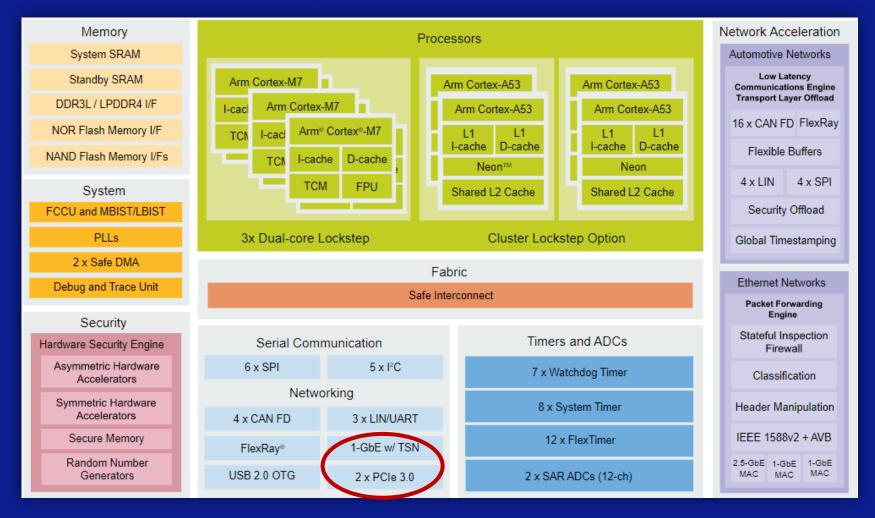

#### **Analog Blocks in S32G2**

https://www.nxp.com/products/processors-and-microcontrollers/s32-automotive-platform/s32g-vehicle-network-processors/s32g2-processors-for-vehicle-networking:S32G2

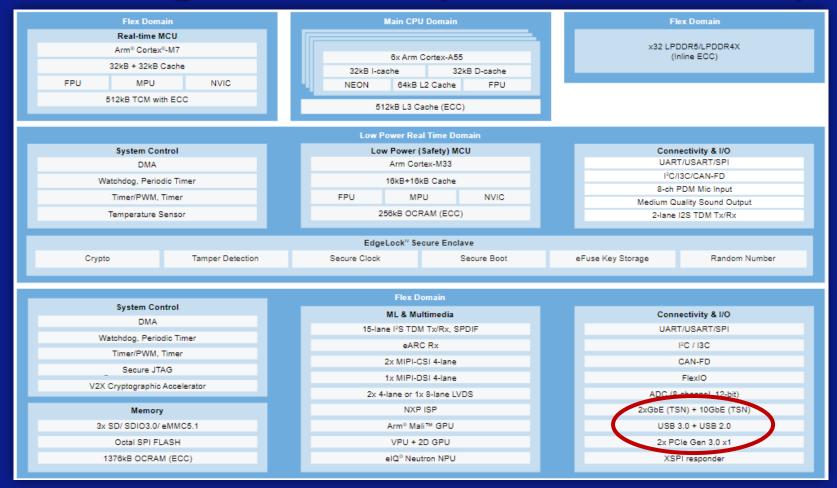

#### **Analog in I.MX95 (Pre-Production)**

https://www.nxp.com/products/processors-and-microcontrollers/arm-processors/i-mx-applications-processors/i-mx-9-processors/i-mx-9-processor-familyhigh-performance-safety-enabled-platform-with-eiq-neutron-npu:iMX95

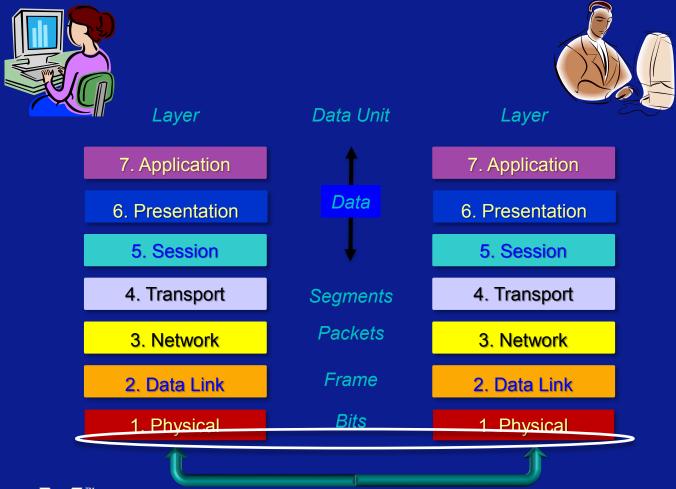

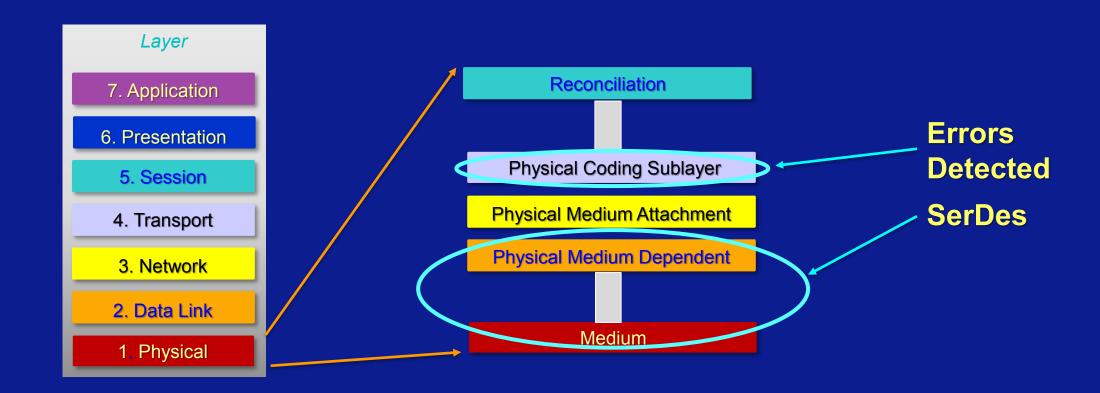

#### Open System Interconnect (OSI) 7-Layer Reference Model

#### A Closer Look

#### **Starter Test Criteria**

- Correct by Design

- Test to Specification

- Test Quickly for Manufacturing Anomalies

- Provide for Debug

## Test Expectations Refined (you can't sell if you can't get it off the Tester)

- Design to Protocol and SoC specifications using the FULL range of manufacturing tolerances and test conditions

- Characterize for Compliance in Lab

- Production Test for Basic Functionality and Manufacturing Anomalies

- Signal Integrity

- Stress Testing

- Probe

- Multi-Site Testing

- > PROVE IT'S NOT THE ANALOG!!!

#### **Understanding the Test Environment**

- Manufacturing Tolerances

- Testing with Large Digital Testers

- Fixed Voltage

- Fixed Clock

- Deterministic Results

- Load Board, Pogo Pins, Socket, Signal Integrity....

- Probe vs. Final Test

- Multi-site Testing

- <u>\_</u>\$\$\$**→**\$

Every additional second on the tester is just taping dollars to the top of the package as it goes out the door.

#### **HOW**

ANALYZE AND ARCHITECT

ISOLATE

ACCESS

OBSERVE

#### **Example**

#### Example (cont.)

#### Wrap the Analog

- Every Analog Design Team should include Digital Design Specialists in:

- ✓ RTL Design

- √ Verification

- ✓ DFT

- ✓ System Software

Digital Registers

#### **Architecting for Test**

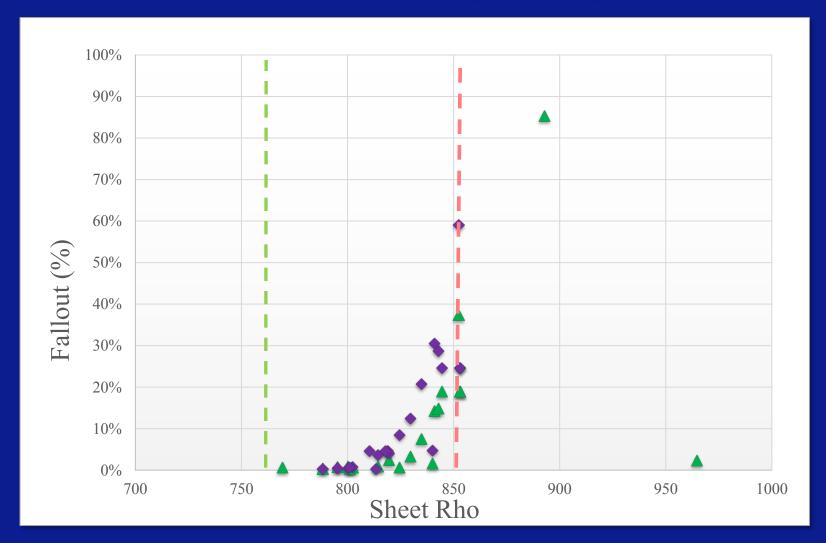

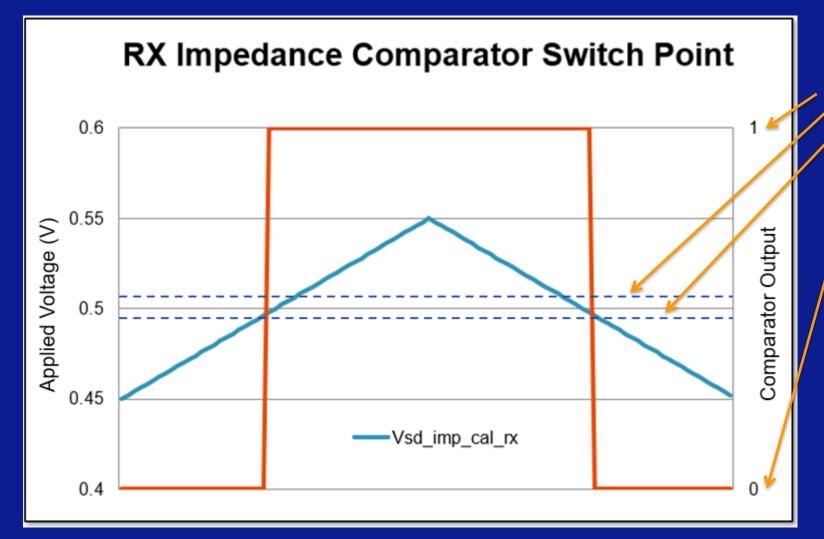

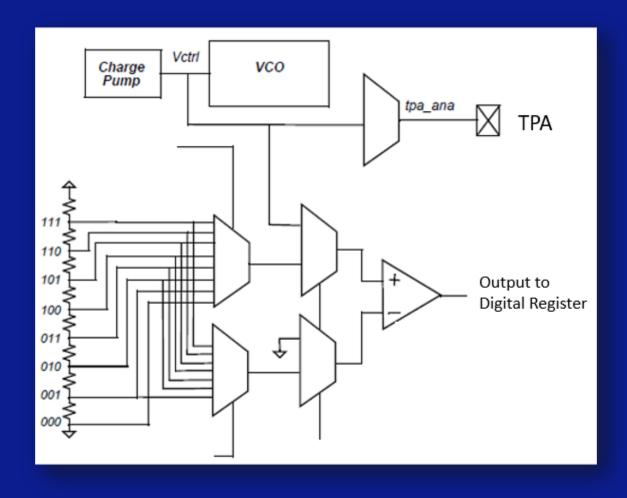

#### Manufacturing Test for Comparators/Resistors

**Manufacturing Test Points**

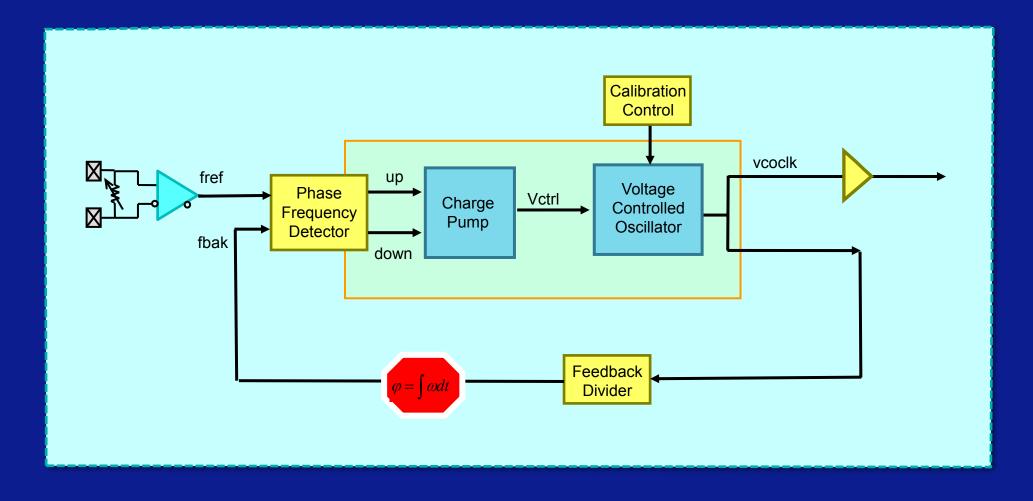

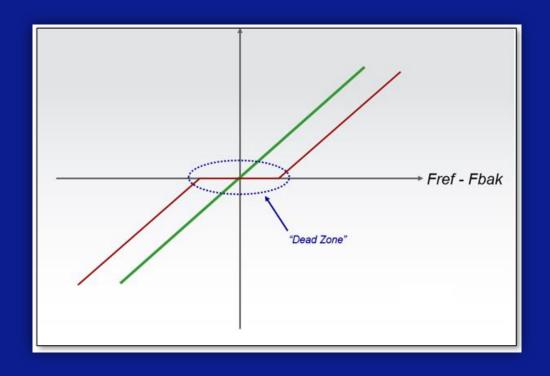

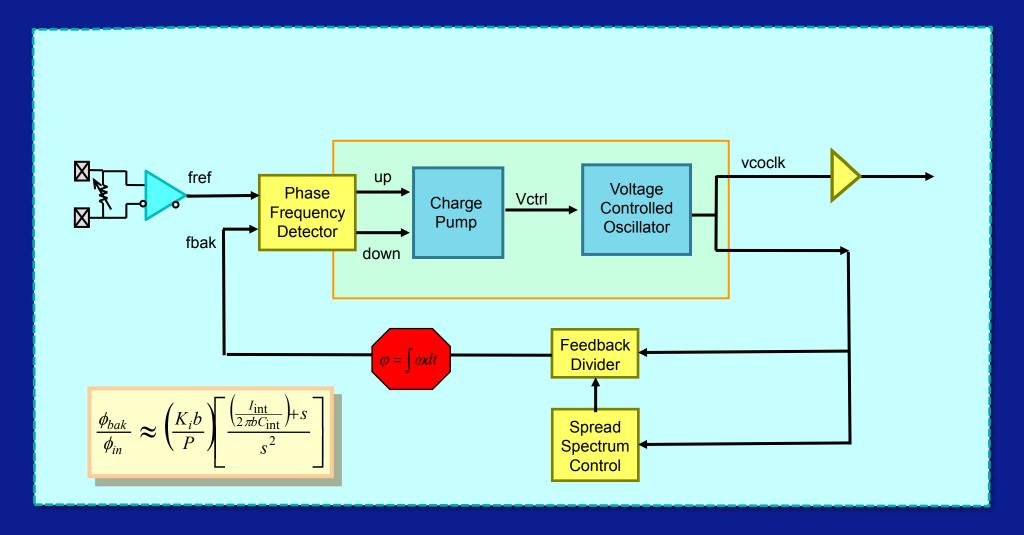

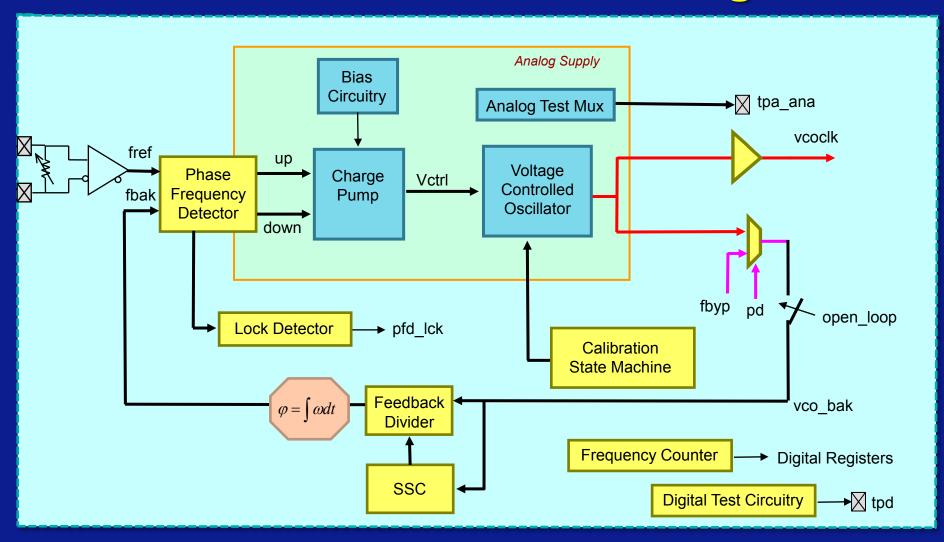

#### **PLL Testing**

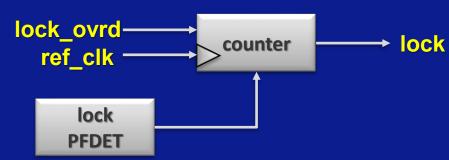

#### LOCK DETECTION

#### **Frequency Counting**

| Step        | Command | Instruction              | Offset                | Register Bits[0:15]              | Register Bits[16:31]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------|---------|--------------------------|-----------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | :commnt | Force                    | sd_rx/_b              | '1'/'0' for simulation: Both '0' | at tester.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 2           | :commnt | Include                  | Include to end of     | 5 4 5 - M - 1 6 2                | PLL Output Fre                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| <del></del> |         |                          |                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 5           | :trans  | Write                    | SRDS(x)TCR0           | 0000 0000 0000 1011              | 0000 0000 0000 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|             |         |                          |                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 6           | :trans  | Read                     | SRDS(x)TCR0           | Lxxx xxxx xxxL HLHH              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| °           | uans    | Read                     | SRDS(x)TCRU           | LXXX XXXX XXXL HLHH              | X000X X00XX X00XX X0XXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|             |         |                          |                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|             |         |                          | l                     | I                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 10          | :trans  | Read                     | SRDS(x)PLL(n)CR0      | XXXX XXXX XXXX XXXX              | XXLL LLLH XXXX XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

|             |         |                          |                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 11          | :commnt | Wait                     | 2600 Cycles           |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 12          | :trans  | Read                     | SRDS(x)PLL(n)SR2      | XXXX XXHL LLHH LLHL              | XXXX XXXX XXXX XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| is          | :commnt | Stop here for Production |                       |                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 14          | :trans  | Write                    | SKUS(X)PLL(n)CR0      | N001 0001 0000 0000              | 0000 0011 0000 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 15          | :trans  | Read                     | SRDS(x)PLL(n)CR0      | XXXXX XXXXX XXXXX XXXXX          | XXXL LLHH XXXX XXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 16          | :trans  | Read                     | SRDS(x)PLL(n)SR2      | xxxx xxxx xxNN NNNN              | XXXX XXXXX XXXXX XXXXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 17          | :commnt |                          | Calculate             | PLL Frequency                    | A STATE OF THE STATE OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 18          | :commnt | Capture                  | pll(n)_freq_cnt[15:0] | Limit Table 10.3.8.2_1           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| ίΰ          | :commnt | logic_chkr               | Verify                | PLL Frequency                    | A STATE OF THE STA |  |  |  |

| 20          | :trans  | Write                    | SKUS(X)PLL(III)CKU    | NUUT 0001 0000 0000              | 0000 0010 0000 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| Ref Freq<br>(MHz) | Clknet<br>Freq<br>(GHz) | Gate<br>Window | GATE_<br>TIME<br>(μs) | Freq_Cntr[17:6]<br>(production<br>test) | Freq_Cntr[5:0]<br>(characterization<br>test) |

|-------------------|-------------------------|----------------|-----------------------|-----------------------------------------|----------------------------------------------|

| 100               | 5                       | 6725           | 67.250                | 0101_0010_0001                          | 01_1111                                      |

| 125               | 5                       | 6800           | 54.400                | 0100_0010_0110                          | 10_0000                                      |

| 156.25            | 5                       | 6900           | 44.160                | 0011_0101_1110                          | 10_0000                                      |

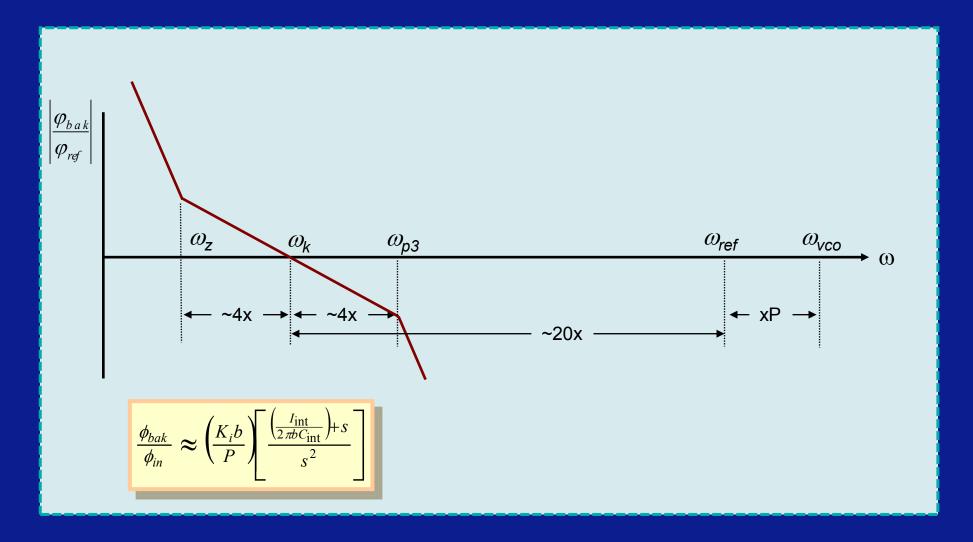

#### **A Low Noise PLL**

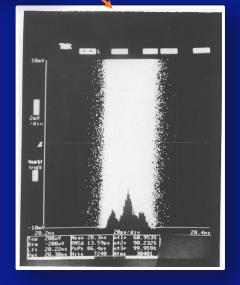

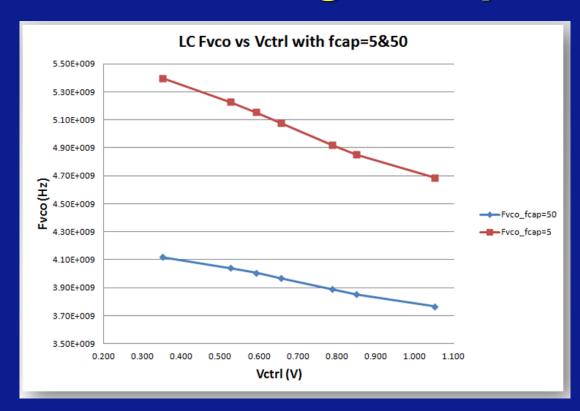

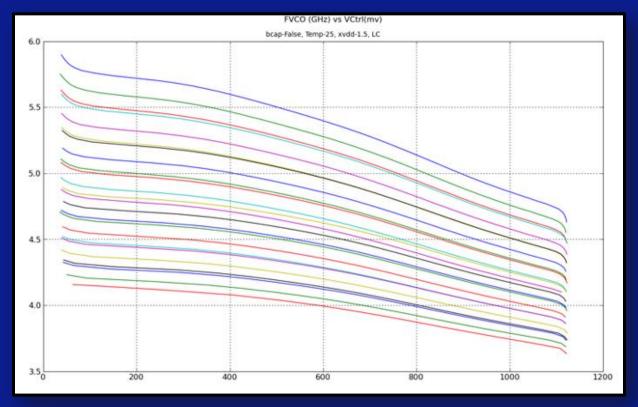

#### VCO Range of Operation Simulation vs Silicon

Simulation

Set Fcap

Sweep Fref to Change Fvco

Measure Vctrl

Lab Measurement

#### **PLL Testing**

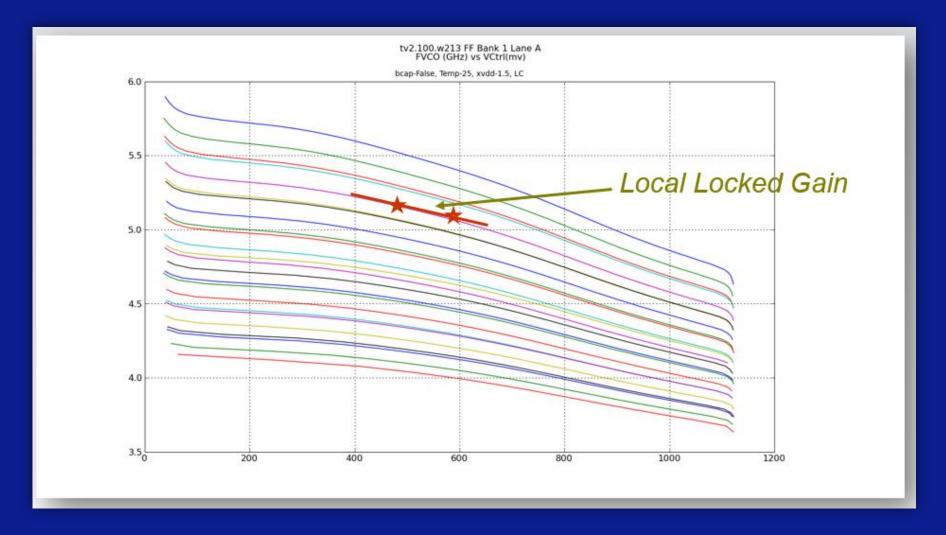

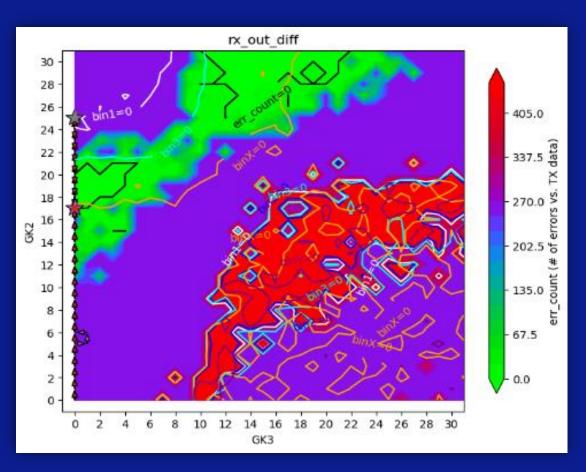

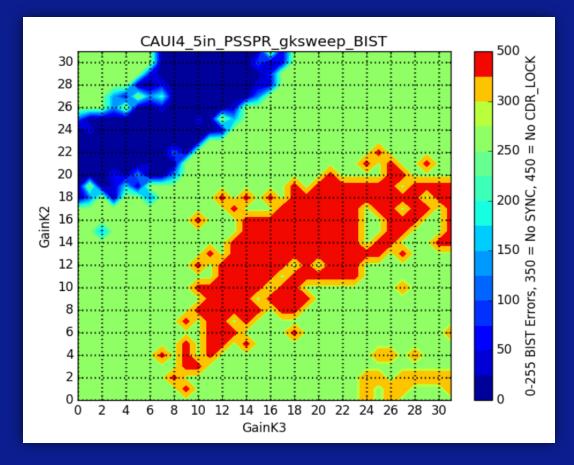

#### **Localized Gain Tests on the Tester**

#### **PLL Testing**

- Lock Observation

- Lock Override

- Bypass

- Frequency Counter

- Fmin/Fmax/Recover

- Calibration Overrides

- Calibration Status

- Open Loop

- Control Voltage

- Gain Tests

- Voltage Regulators

- Current Bias

- Digital Logic Testing

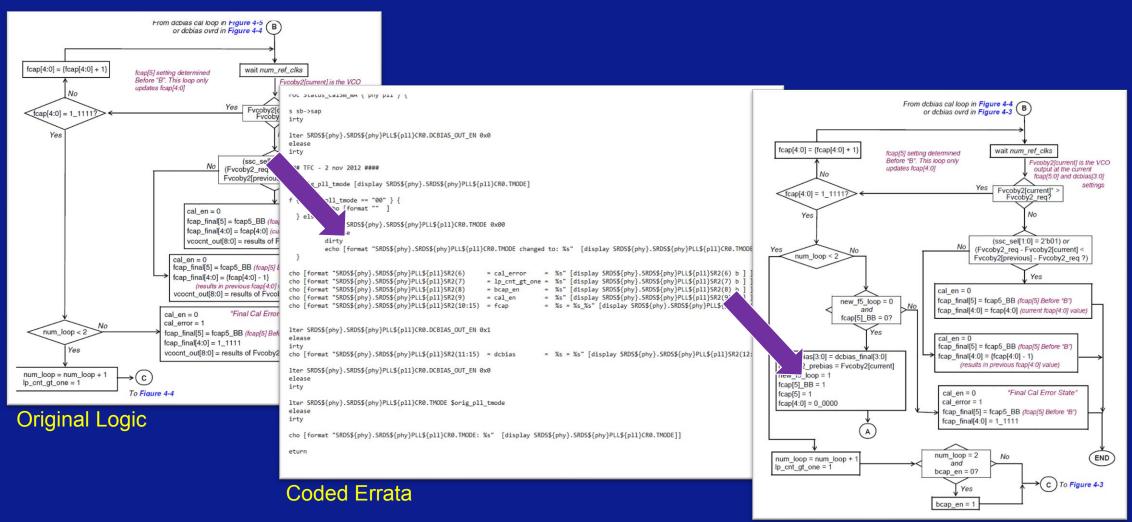

#### **Calibration Status and Overrides**

**Revised Logic**

#### **Converting To Digital Result**

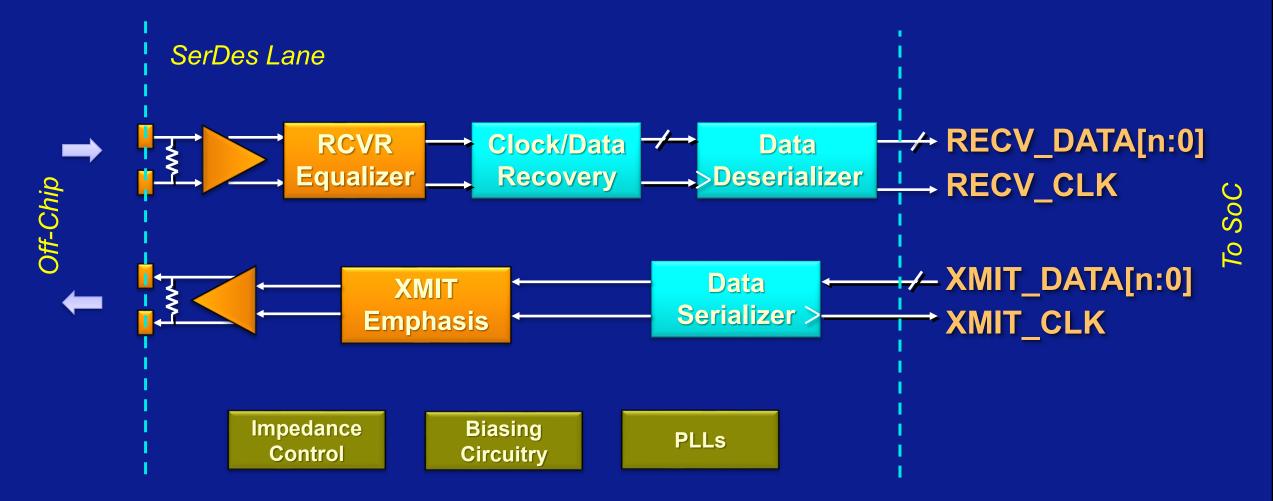

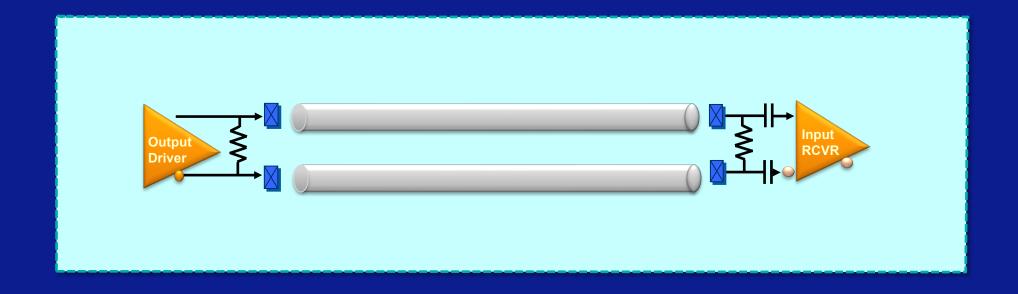

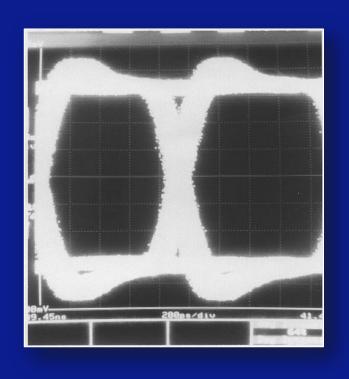

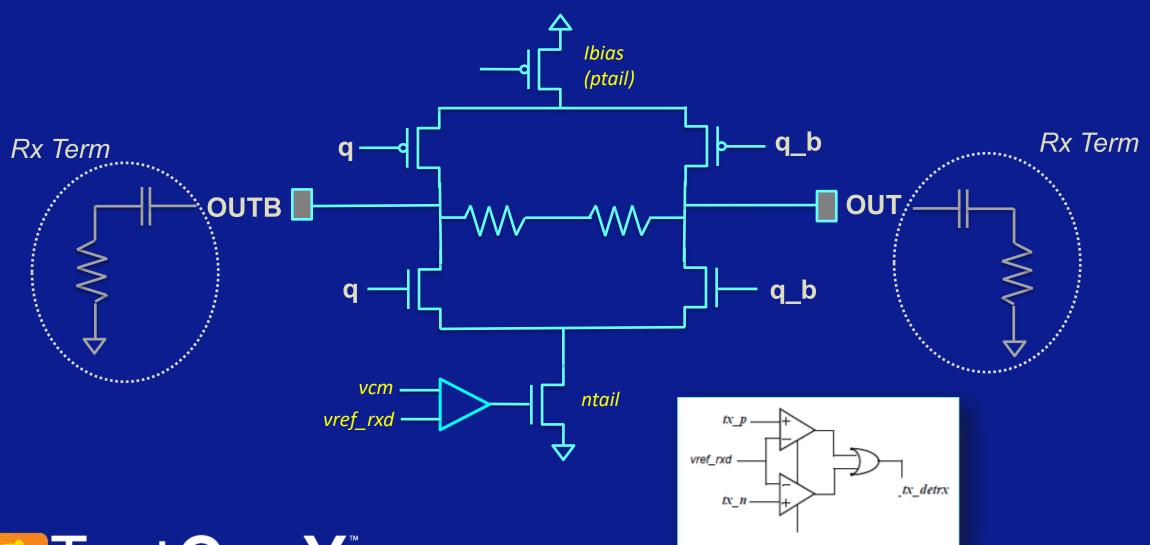

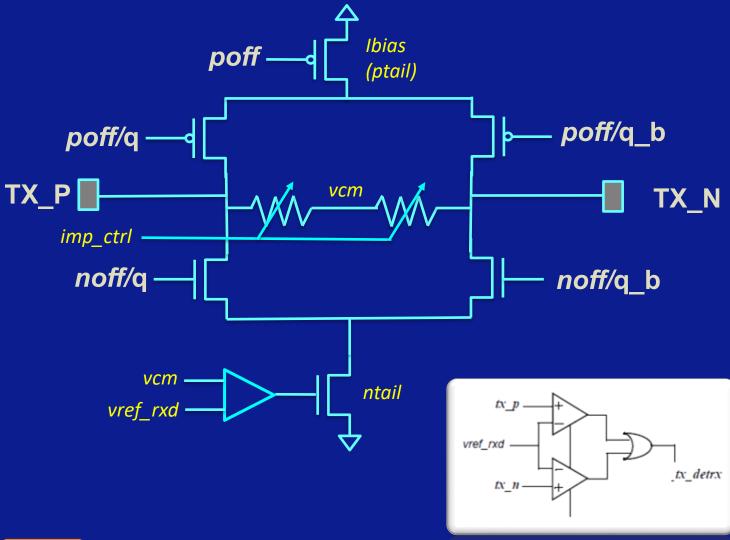

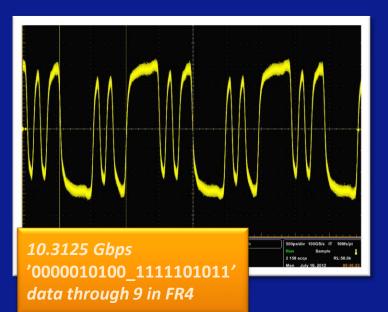

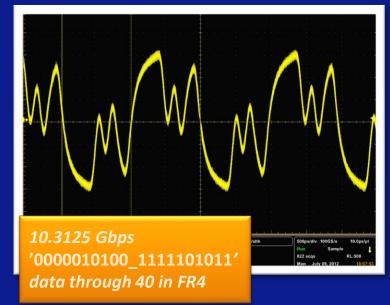

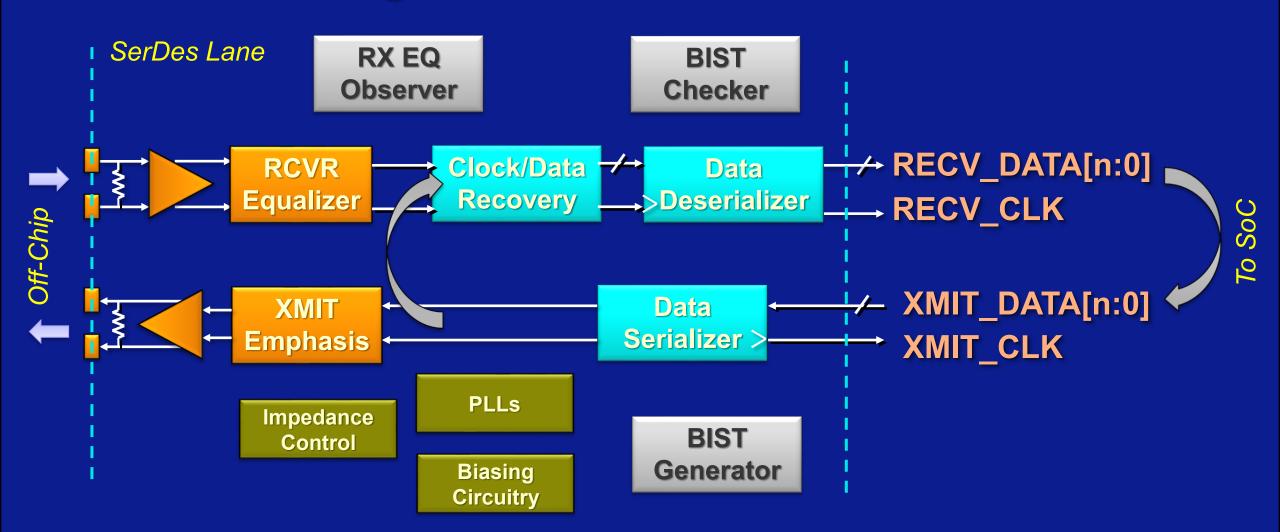

#### High Speed I/O

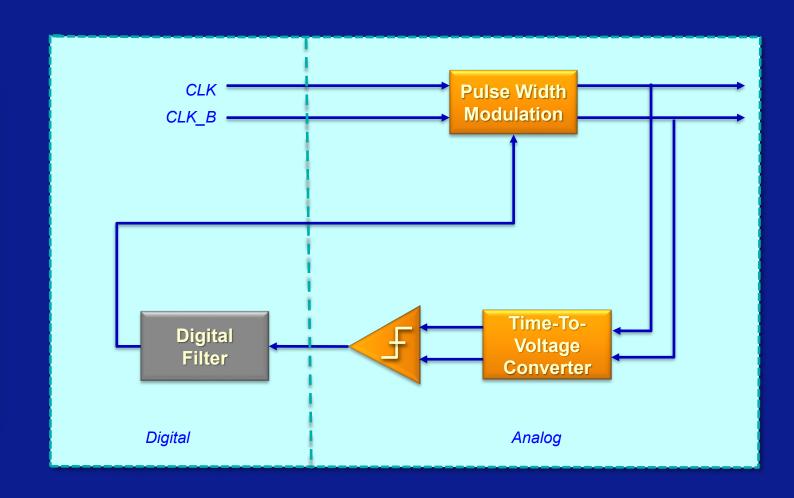

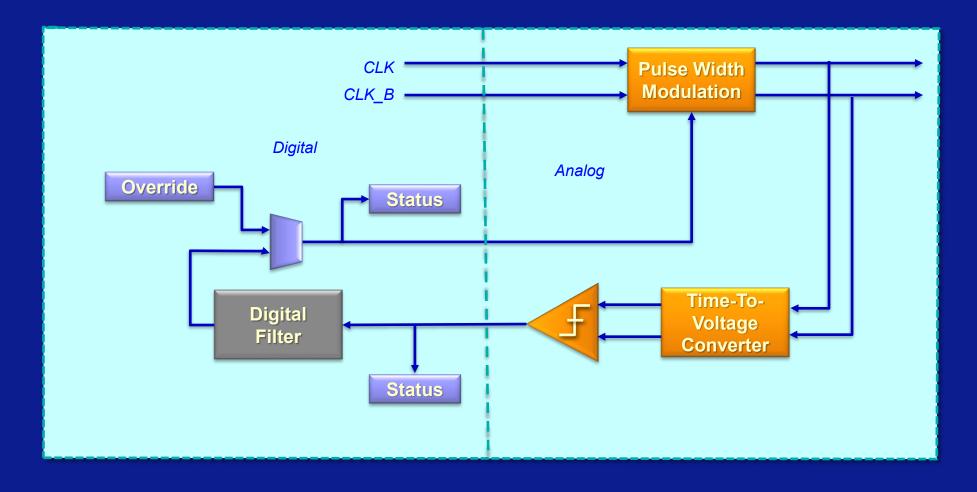

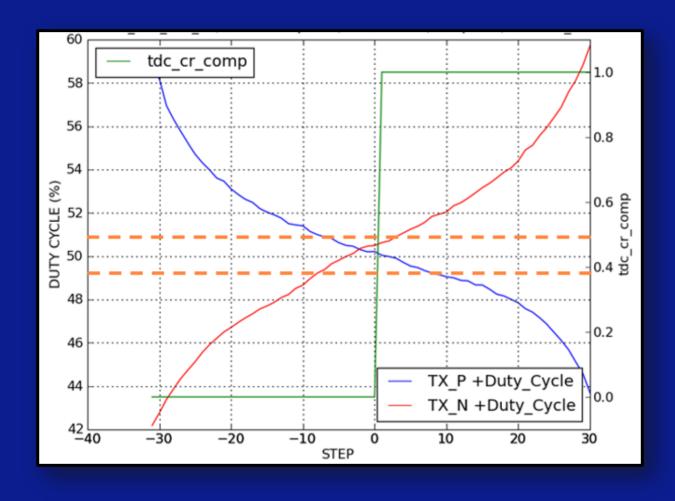

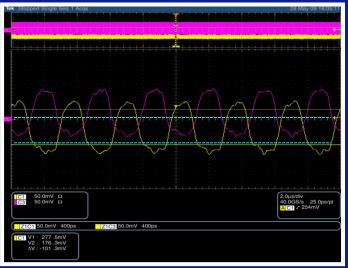

#### **Duty Cycle Correction**

#### **Duty Cycle Correction**

#### **Duty Cycle Correction Testing**

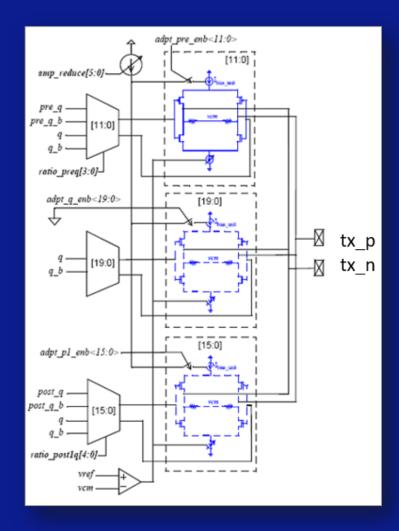

# **Transmitter Example**

#### **Transmitter Tests**

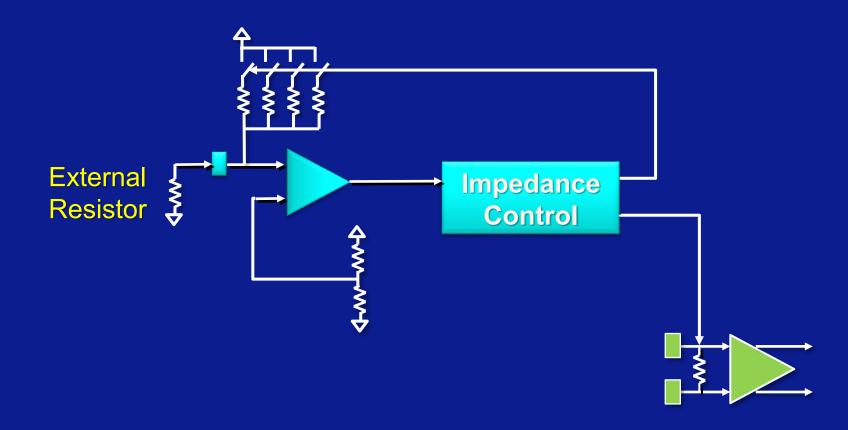

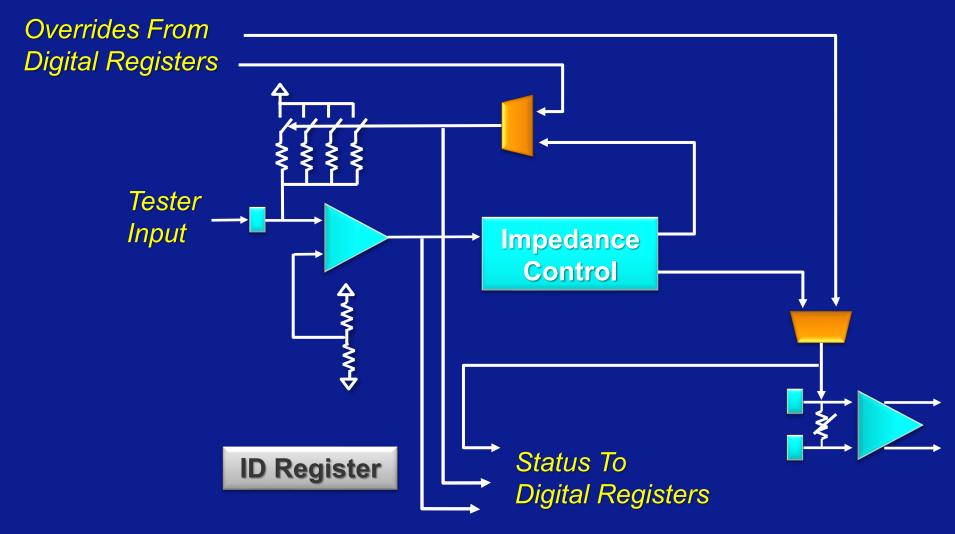

- Output Impedance Measurements

- DC Output Amplitudes and Ratios

- RX Detect Comparator Threshold

- Output Voltage Self Test

- Common Mode

| Test_Ctrl[1:0] | Comparator<br>Threshold |  |  |  |

|----------------|-------------------------|--|--|--|

| 2'b00          | n/a                     |  |  |  |

| 2'b01          | Vref_1                  |  |  |  |

| 2'b10          | Vref_2                  |  |  |  |

| 2'b11          | Vref_3                  |  |  |  |

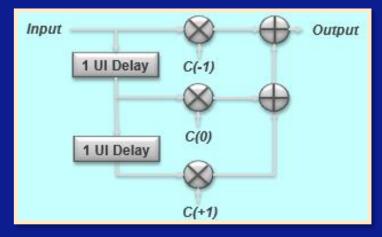

# **Adapting Functions for Test**

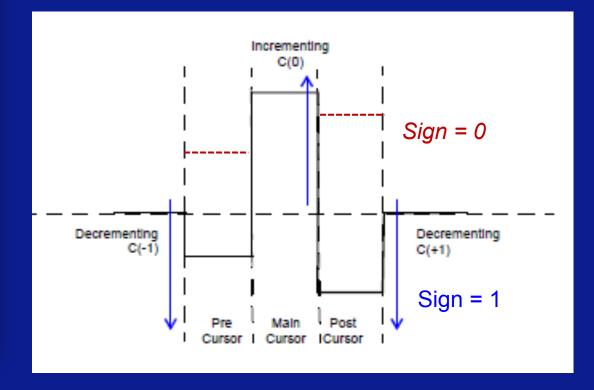

Ref: IEEE802.3<sup>TM</sup> Clause 72

## **Transmitter Equalization Testing**

App Note: NXP AN5119

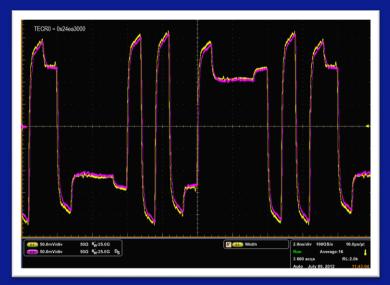

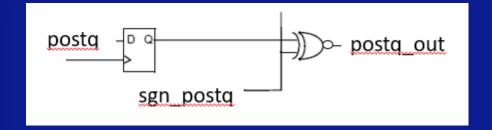

# **Transmitter At-Speed Cursor Tests**

Sign = 1

Sign = 0

Sign bit broken

Stuck

Weighting

MSB

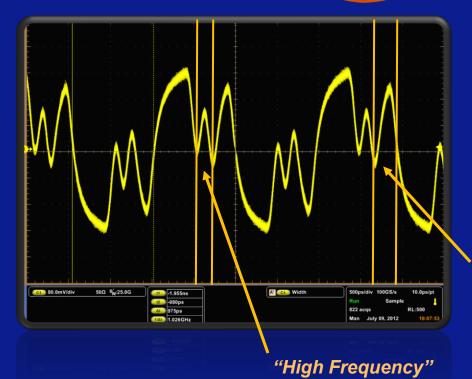

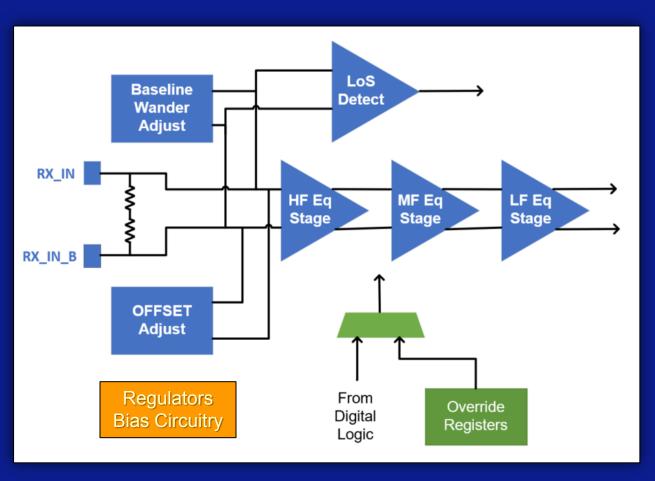

## **Receive Equalization**

- CTLE: Continuous Time Linear Equalization

- DFE: Decision Feedback Equalization

"Mid Frequency"

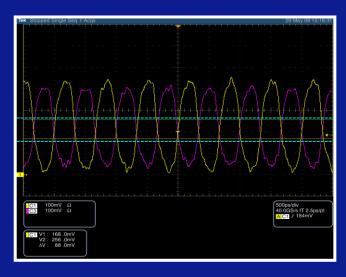

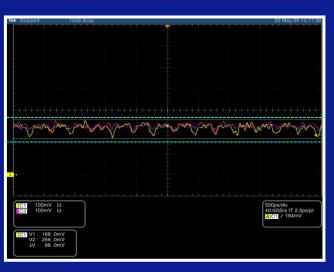

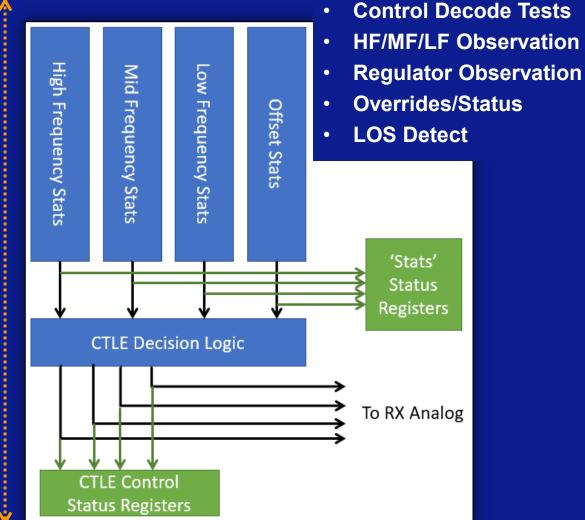

## **Receiver CTLE Testing**

## Things that Became "Standard"

# How to get what you need from Design

How to prove it's not the Analog

How to get Test to go Away

## **Detecting if Things Go Wrong**

#### **Isolation**

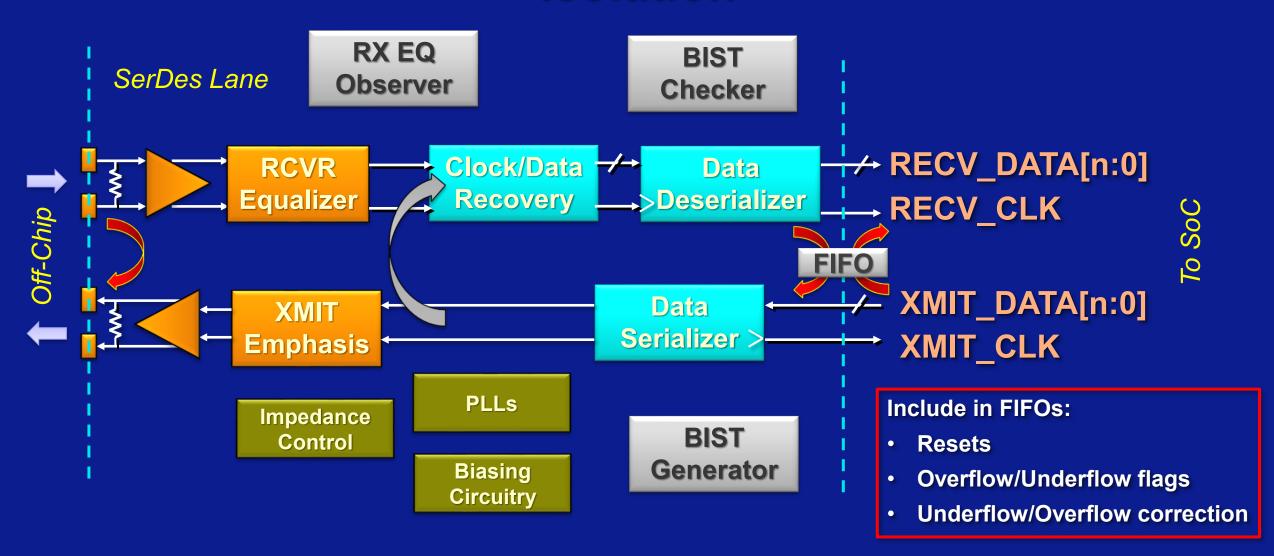

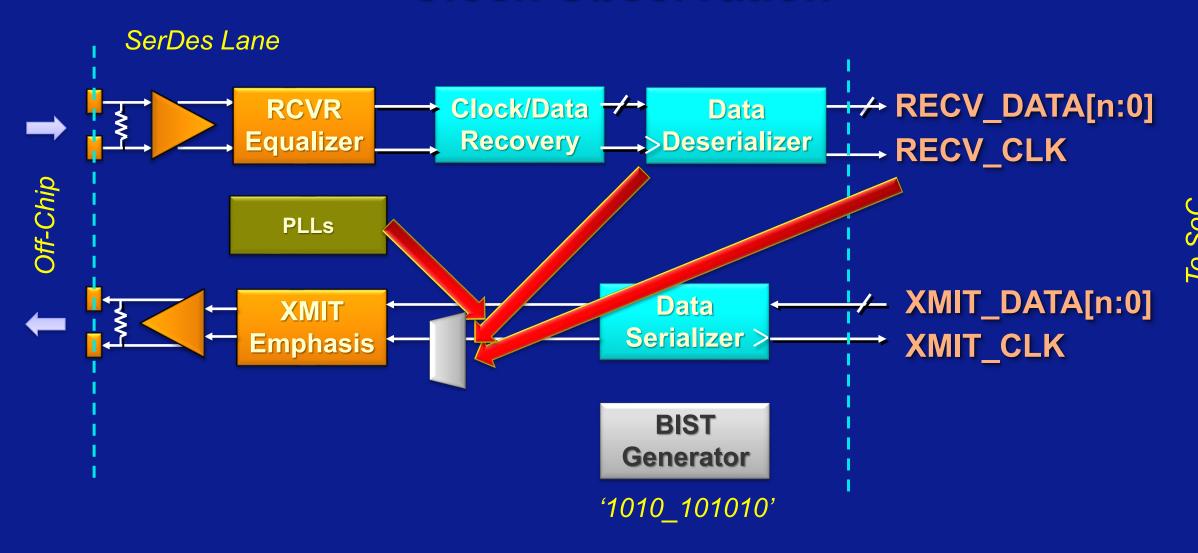

### **Multi-purpose FIFOs**

RX\_DATA[n:0]

From SoC To SoC

RECV\_DATA[n:0]

FIFO OBS\_RX\_DATA[n:0]

#### **Include in FIFOs:**

- Resets

- Overflow/Underflow flags

- Underflow/Overflow correction

#### Capturing K28.5 (10bit interface):

|                  |            | <u> </u>                                                                                                      |                                                                     |

|------------------|------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Unload<br>Number | RX_DATA(39 | :0)                                                                                                           |                                                                     |

| 1                | 0000 0000  | 0000 0000 0000 0000                                                                                           | 0 0000 00 <mark>00 0110 1011</mark>                                 |

| 2                | 0000 0000  | 000000000000000000000000000000000000000                                                                       | 0 0000 00 <mark>11 1001 0100</mark>                                 |

| 3                | 0000 0000  | _0000_0000_0000_0000                                                                                          | 0000 <sup>0</sup> 0 <mark>00<sup>0</sup>0110<sup>1</sup>1011</mark> |

| 4                | 0000_0000  | _0000_0000_0000_0000                                                                                          |                                                                     |

| 5                | 0000_0000  | _0000_0000_0000_0000                                                                                          |                                                                     |

| 6                | 0000_0000  |                                                                                                               |                                                                     |

| 7                | 0000_0000  |                                                                                                               |                                                                     |

| 8                | 0000_0000  | 0000_0000_0000_0000                                                                                           | 0 0000_0011_1001_0100                                               |

|                  |            | Unload RX_DATA(39 Number  1 0000_0000 2 0000_0000 3 0000_0000 4 0000_0000 5 0000_0000 6 0000_0000 7 0000_0000 | Unload RX_DATA(39:0) Number  1                                      |

#### Capturing K28.5 (20bit interface):

```

(Handy Scripts) 108 % Read Parallel Data 1 h 8 snap

Data taken with snapshot and data unload

RX DATA (39:0)

Unload

Number

0000 0000 0000 0010 1000 0011 0101 1111

0000 0000

0000 0000 0000 0010

0000 0000

0000 0000 0000 0010 1000 0011 0101 1111

0000 0000 0000 0010

1000 0011 0101 1111

0000 0000 0000 0010 1000 0011 0101 1111

0000 0000

0000 0000 0000 0010

1000 0011 0101 1111

0000 0000 0000 0010 1000 0011 0101 1111

0000 0000

```

#### **Clock Observation**

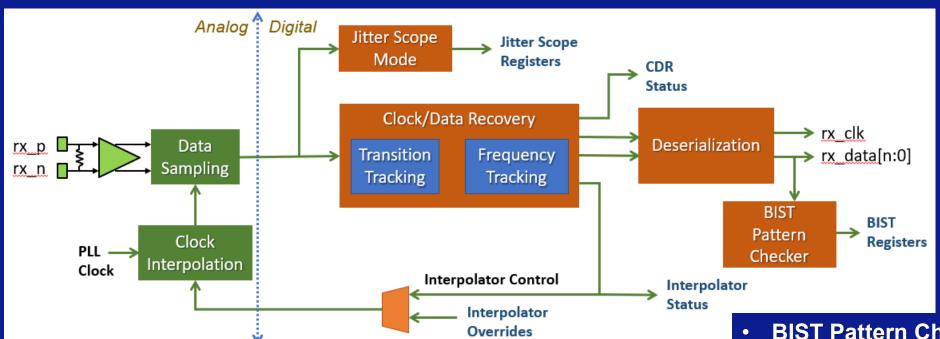

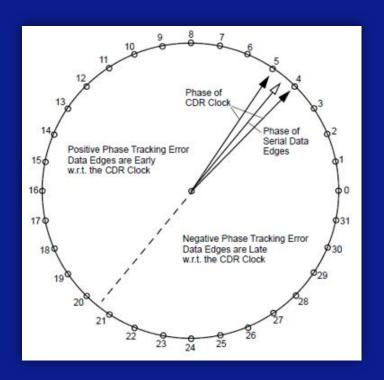

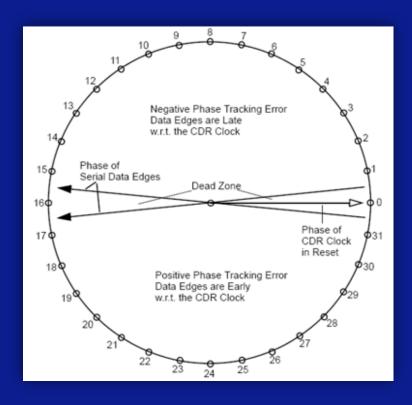

#### RX Clock/Data Recovery

- BIST Pattern Checker (NXP AN5119)

- Internal Eye Monitor (NXP AN5119)

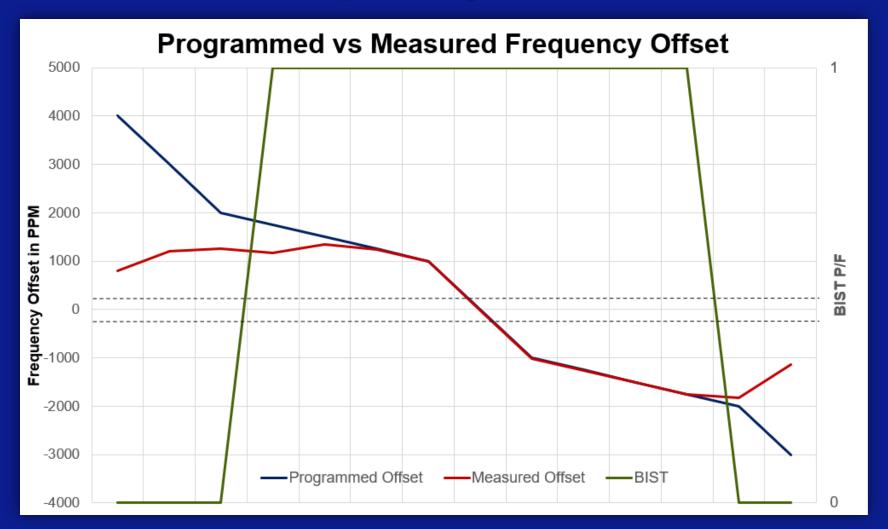

- Frequency Offset Status

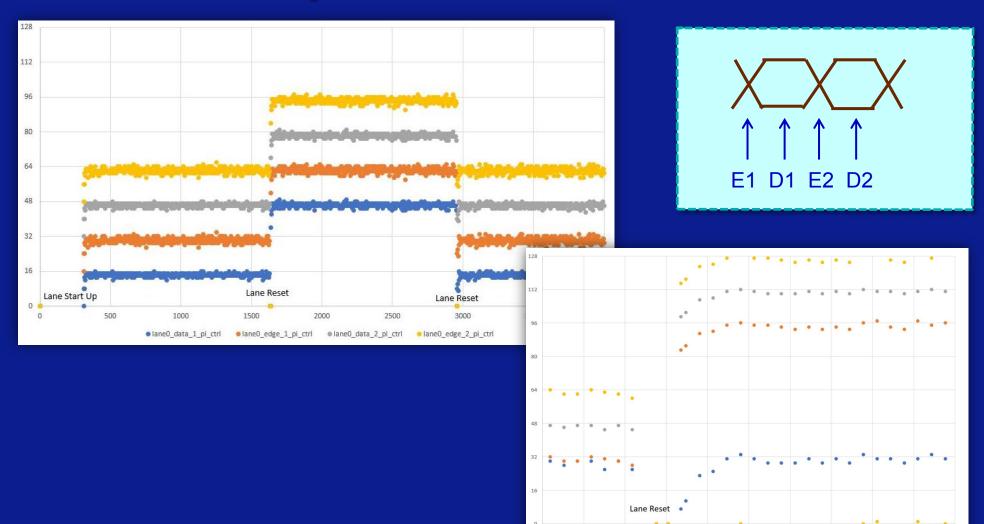

- Interpolator Status/Overrides

- CDR Stall Detector

- False Lock Watchdog

# **Frequency Offset**

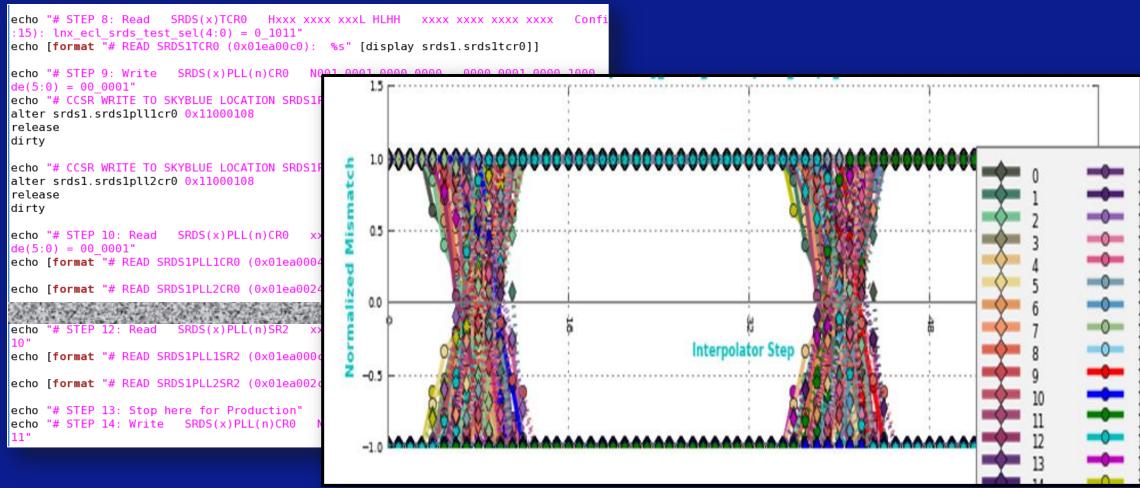

## **Interpolator Observation**

Interpolator Position

## Every Loop Needs an 'Unstick' Plan

- Tester is 'clean' environment

- Suppose startup position ends up 180deg out from initial state

- Correct by overriding and releasing interpolator position

- Implement a watchdog timer

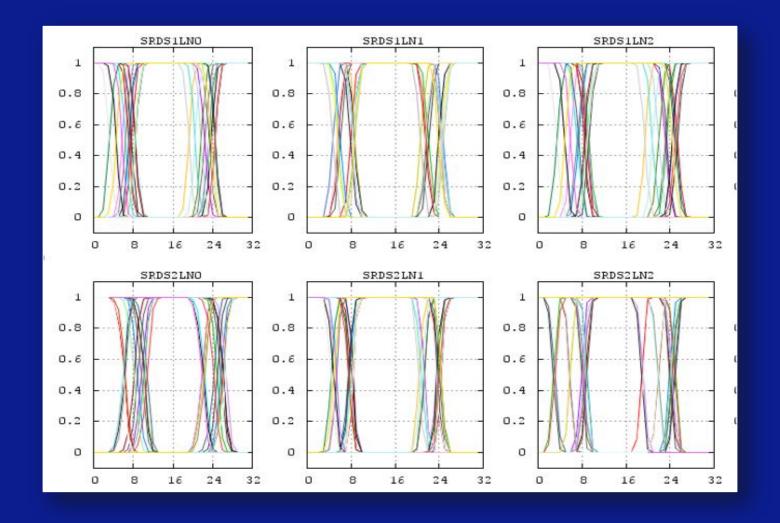

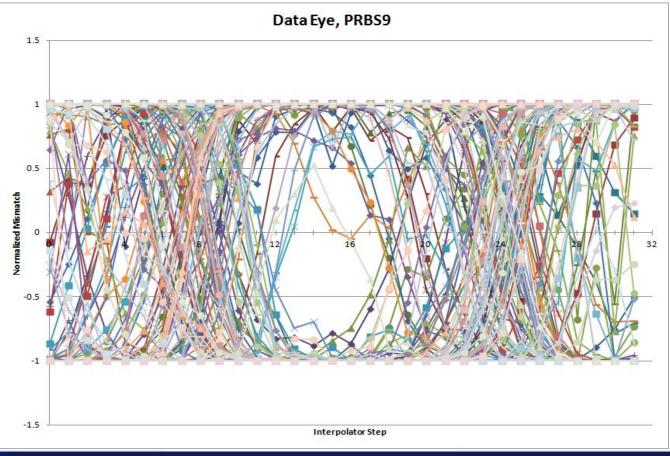

## **RX Equalization Design Confirmation**

Simulation – 6.75in channel

Silicon - 5in channel

## "Over The Wall" Design for Test

#### **How Not to Write a Test Guide**

| 7.2 | Transmitter Impedance Control Testing                                                                                                                                                                            |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                                                  |

|     |                                                                                                                                                                                                                  |

| 3.  | With the equivalent 100 ohm calibration resistor removed, measure $V_{SD\_IMP\_CAL\_TX}$ . Adjust the tester supply until $V_{SD\_IMP\_CAL\_TX}$ equals the desired power supply test condition. This value will |

|     | tester supply until V <sub>SD_IMP_CAL_TX</sub> equals the desired power supply test condition. This value will be used throughout the remainder of the tests.                                                    |

|     |                                                                                                                                                                                                                  |

|     |                                                                                                                                                                                                                  |

### **Understanding the Test Environment**

- ELIF

- Manufacturing Tolerances

- Testing with Digital Testers

- All conditions known at the START of the test

- Fixed Voltage

- Fixed Clock

- Deterministic 1's and 0's

- Load Board, Pogo Pins, Socket....SIGNAL INTEGRITY!!!

- Fully defined stress test modes

### **Fully Defined Stress Test Modes**

- Voltages applied during Stress Testing

- Clock Frequencies used during Stress Testing

- Device Control Method

- Multi-Site? IDDQ Limitations?

- Suggest:

- Simplified Access: Stress\_En[3:0]

- Internal Biasing

- Internal Control of Activity Levels

- Internal Regulators Bypassed as Needed

- Simplified Status: Stress\_Result[3:0]

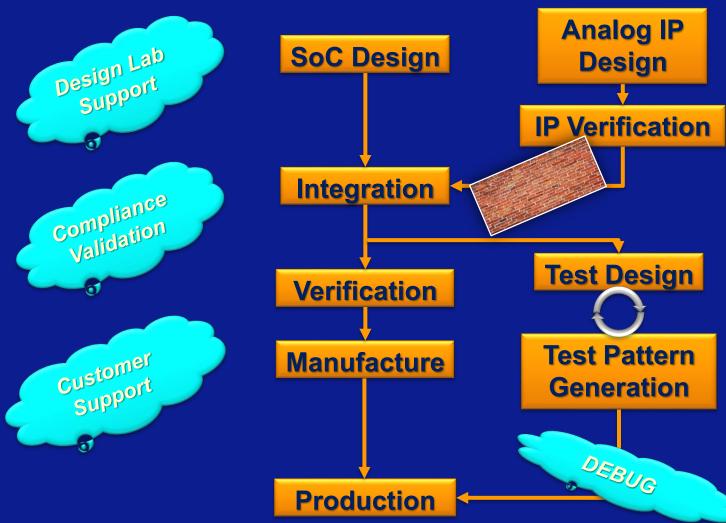

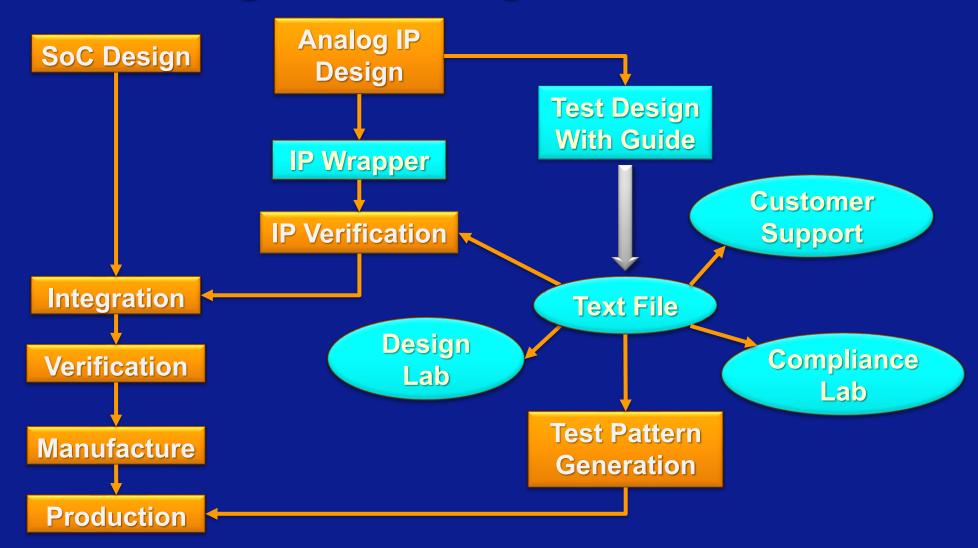

## **Integrated Design for Test**

#### **Human Readable Format**

|    | Step     | Command | Instruction   | Offset                | Register Bits[0:15]             | Register Bits[16:31]                     | Notes                       |

|----|----------|---------|---------------|-----------------------|---------------------------------|------------------------------------------|-----------------------------|

|    | 1        | :commnt | Force         | sd_rx/_b              | '1'/'0' for simulation: Both '0 | at tester.                               |                             |

|    | 2        | :commnt | Include       |                       | <b>《</b> 上海》                    | <b>人。第二次的对象是</b>                         | 好多之所上 在 一种 一种 一种 一种 一种      |

|    |          |         |               |                       |                                 | **** **** ****                           | CONTRACTOR SERVICES         |

|    | 5        | :trans  | Write         | SRDS(x)TCR0           | 0000 0000 0000 1011             | 0000 0000 0000 0000                      |                             |

|    | 6        | :trans  | Read          | SRDS(x)TCR0           | LXXX XXXX XXXL HLHH             | X000X X000X X000X X000X                  |                             |

|    | 10       | :trans  | Read          | SRDS(x)PLL(n)CR0      | XXXX XXXX XXXX XXXX             | XXLL LLLH XXXX XXXX                      |                             |

|    | 11       | :commnt | Wait          | 2600 Cycles           |                                 |                                          | Concerns of the Concerns of |

|    | 12       | .trans  | Read          | SRDS(x)PLL(n)SR2      | XXXX XXHL LLHH LLHL             | XXXX XXXX XXXX XXXX                      |                             |

|    | 13       | :commnt | Stop here for |                       |                                 |                                          |                             |

|    | 14       | trans   | Write         | SRDS(x)PLL(n)CR0      | N001 0001 0000 0000             | 0000 0011 0000 1000                      | A SHELL WAS TO SHELL WAS    |

|    | 15       | :trans  | Read          | SRDS(x)PLL(n)CR0      | XXXXX XXXXX XXXXX XXXXX         | xxxL LLHH xxxx xxxx                      |                             |

|    | 16       | :trans  | Read          | SRDS(x)PLL(n)SR2      | XXXX XXXX XXNN NNNN             | XXXXX XXXXX XXXXX                        |                             |

| 4  | 17       | :commnt |               | Calculate             | Frequency                       | 20 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - |                             |

|    | 18       | :commnt | Capture       | nll(n) freq cnt[15:0] | Limit Table 10.3.8.2_1          | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1    | COLUMN CONTRACTOR OF COMME  |

| \$ | 19<br>20 | :commnt | logic_chkr    | Verify Locked         | PLL NOON DOOD                   | Tonha nata nana taoh                     |                             |

#### **Text File**

|      |                      |                  |             |      |        |        |       |     |      | 7     |       | 100    |            |        |           |           |   |

|------|----------------------|------------------|-------------|------|--------|--------|-------|-----|------|-------|-------|--------|------------|--------|-----------|-----------|---|

| Step | Command              | Instruct         | tion Offset | Regi | ster l | Bits[6 | 0:15] | R   | egis | ter E | Bits[ | 16:31] | No         | otes   |           |           |   |

|      | : commnt<br>: commnt | Force<br>Include |             |      |        |        |       |     |      |       |       | · ·    |            | . 7    | 1 2 7 5 7 |           |   |

|      | :trans               | Write            | SRDS(x)TCR0 | 0000 | 0000   | 0000   | 0000  | 0   | 000  | 0000  | 0000  | 0000   | P          | rogram | Initializ | ze Testin | g |

|      |                      |                  |             | 2    |        | 7,1    |       |     |      | 7,    | 10 M  |        | A STATE OF | 7,     |           |           |   |

|      | :trans               | Read             | SRDS(x)TCR0 | Lxxx | XXXX   | xxxL   | LLLL  | Х   | XXX  | XXXX  | XXXX  | XXXX   | C          | onfirm | Initializ | ze Testin | g |

|      |                      |                  |             |      | 21.0   | · Z    |       |     |      |       | 7     |        |            |        |           |           |   |

|      | :trans               | Write            | SRDS(x)TCR0 | 0000 | 0000   | 0000   | 1011  | 0   | 000  | 0000  | 0000  | 0000   | Р          | rogram | for PLL t | testing   |   |

|      |                      |                  |             |      |        |        | 7,7   |     |      |       | 7.    |        |            |        | 7,7       |           |   |

|      | :trans               | Read             | SRDS(x)TCR0 | Lxxx | XXXX   | xxxL   | HLHH  | Х   | XXX  | XXXX  | XXXX  | XXXX   | C          | onfirm | PLL testi | ing       |   |

|      |                      |                  |             |      | 1      |        | Z.    |     |      |       | 7,    | 10 M   |            |        | Z         |           |   |

|      | :trans               | Write            | SRDS(x)TCR0 | 1000 | 0000   | 0000   | 1011  | 0   | 000  | 0000  | 0000  | 0000   | Р          | rogram | for PLL t | testing   |   |

|      |                      |                  |             |      |        |        | 7     | 100 |      | 21.5  | 7,    |        |            | 210    | $X_{p}$   |           |   |

|      | :trans               | Read             | SRDS(x)TCR0 | Hxxx | XXXX   | xxxL   | HLHH  | Х   | XXX  | XXXX  | XXXX  | XXXX   | C          | onfirm | PLL testi | ing       |   |

|      |                      |                  |             |      | 3      |        | Y, ,  |     |      |       | 5 Z,  |        |            |        | 7,12      |           |   |

#### **To Tester**

#### **RTL Stimulus**

```

// COMMENT: SUB-STEP 36: Write SRDS(x)TCALCR

0000 1000 0000 0000

// COMMENT: SUB-STEP 37: Read SRDS(x)TCALCR

`Read(SRDS1TCALCR, xxxx,Hxxx,xxxx,xxxx,xxxx,xxxx,

// CLOCK:

'Wait(40, Cycles);

// COMMENT: SUB-STEP 39: Read

SRDS(x)PLL(n)CF

Read(SRDS1PLL1CR0, xxxx,xxxx,Hxxx,xxxx,xxxx,xx

`Read(SRDS1PLL2CR0, xxxx,xxxx,Hxxx,xxxx,xxxx,xx

// COMMENT: SUB-STEP 40: logic chkr

```

# TCL Files for Design/Compliance Lab

### **Python For The Validation Lab**

```

for snap step in range(num snaps):

alter lynx reg( dut = dut name, phy num=phy num, lane = lane num, reg name = 'GCR1',

bit field = 'REQ CDR SNP', new val = 0x1)

lynx reg name, cdr lck = fetch lynx reg(dut=dut name,phy num=phy

reg name="TCSR3",bit fie

lynx reg name, pm dis = fetch lynx reg(dut=dut name,phy num=phy

reg name="TTLCRO",bit fi

lynx reg name, poll snap done = poll lynx reg(dut=dut name,phy n

reg name="RECR1", bit fie

if cdr lck == 0x0:

raise ValueError("ValueError: CDR did not lock. Please check

if poll snap done == False:

raise ValueError("ValueError: Snapshot did not complete")

new ts = time.time()

delta time = (\text{new ts - old ts})*1000

lynx_reg, tsout = fetch_lynx_reg( dut = dut_name, phy_num = phy_

bit field = 'TSOUT' )

tsout bin = bin(eval(tsout))[2:].zfill(21)

tsout signed dec = twos comp2dec(tsout bin)

freq offset ppm = ((-1.0))*tsout signed dec*Kph*Kfr/512)*1000000

sum freq offset = sum freq offset + freq offset ppm

if print status == 1:

if snap step == 0:

delta time = 0

print Green + '{0:10.3f} {1:^8s} {2:^6s} {3:20s}

.format(delta time,cdr lck, pm dis, tsout bin, tsout signed

```

#### **Even More From The Tester**

```

III ₹ccs

Terminal

atx.pete.rc

Status lynx t42...

◆ Tue Jul 2, 4:53 PM

CCS: atx.pcccs UT A TAP:etap:null Port:40019 Console:50019

File Edit Interp Prefs History

# READ SRDS1LN4TCSR3 (0xfe0ea93c)

# READ SRDS1LNSTCSR3 (Oxfe0ea97c)

1640000P

# READ SRDS1LN6TCSR3 (OxfeOea9bc)

# READ SRDS1LN7TCSR3 (0xfe0ea9fc):

0826000F

# STEP 20: Wait MNONN Cycles Wait desired time

# STEP 21: after 1

# STEP 22: Read SRDS(x)LN(a)TCSR3

2000: Hood 2000: HEBR LLLL LLLL 2000: 2000: Confirm:

(a) bist_err_cnt(7:0) = 8'b0000 0000

# READ SEDSILNOTOSR3 (Oxfe0ea83c):

# READ SRDS1LN1TCSR3 (Oxfe0ea87c):

1640000F

# READ SRDS1LN2TCSR3 (0xfe0ea8bc)

# READ SRDS1LN3TCSR3 (OxfeOea8fc)

16400001

# READ SRDS1LN4TCSR3 (0xfe0ea93c)

# READ SRDS1LNSTCSR3 (Oxfe0ea97c)

# READ SRDS1LNGTCSR3 (OxfeOea9bc)

# READ SRDS1LN7TCSR3 (0xfe0ea9fc)

(bin) 186 % Status_Block_TCSR3 1

SRDS1 SRDS1LNOTOSR3 - 1A4E010F

SRDS1 SRDS1LN1TCSR3 - 164C000F

SRDS1 SRDS1LN2TCSR3 = 164C000F

SRDS1 SRDS1LN3TCSR3 = 164C000F

SRDS1.SRDS1LN4TCSR3 = 164C000F

SRDS1_SRDS1LNSTCSR3 = 164C000F

SRDS1 SRDS1LN6TCSR3 = 164C000F

SRDS1 SRDS1LN7TCSR3 = 164C000F

RDS1 SRDS1GRO - 01810000

SRDS1 SRDS10R0(4:15) = SRDS1 SRDS1GRO LID =

SRDS1 SRDS10R0(17) - SRDS1 SRDS10R0 DDR_SEL -

End Status SRDS1 SRDS10R0

```

#### **Customer Tools**

Select pattern

length

### **During That Inevitable Debug...**

- 1. Check your power supplies

- 2. Check your clocks

- a. Frequency?

- b. Spread Spectrum?

- 3. Are you still in reset?

- 4. Check the programmed configuration

- 5. Repeat steps 1-4 at least twice

- 6. Check your PLLs

- 7. Do you have data? Does it make sense?

- 8. Back up to simpler test/setup

- Document steps 1-8 in something other than email

### In Summary....

- Be sure ALL disciplines understand ALL Test Environments

- Make the Analog look "Digital"

- Configurations in one group of registers

- Status in another group of registers

- Power Downs and Resets in a third group of registers

- Make Test Description Modular, Scriptable and Portable

- Provide for Debug Hooks

- IEEE 1687<sup>™</sup> 2014: IEEE Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device, November 2014

#### Conclusion

|                                           | First Generation                                                                                                                  | Second Generation                                         | Third Generation                                                              |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| IP test control                           | Non-standard                                                                                                                      | Standard PHY wrapper, fully register based                | Standard PHY wrapper, fully register based, improved internal test capability |  |  |

| Test Documentation                        | Verbal, difficult translation to SoC<br>svc reg transactions, multiple test<br>guides and limits per process node<br>and fab site | Tabular, scalable, unified test guide and limits          | Tabular, scalable, unified test guide and limits, standard setups             |  |  |

| Test Documentation to RTL<br>Verification | Non-Existent                                                                                                                      | Manual                                                    | Fully Automated from Test  Documentation                                      |  |  |

| Test pattern development                  | Manual – slow, error-prone<br>(months)                                                                                            | Automated – fairly fast, accurate,<br>simulated           | Automated – very fast, accurate, scripted (week)                              |  |  |

| Tester code development                   | Manual, SoC-specific                                                                                                              | Automated, SoC-generic                                    | Automated, SoC-generic                                                        |  |  |

| Tester CZ development                     | Manual, SoC-specific                                                                                                              | Separate, significant development effort                  | Integrated, minimal development effort                                        |  |  |

| Tester CZ capability                      | Good                                                                                                                              | Better                                                    | Best, Tx Eq, Jitter Scope Mode                                                |  |  |

| Lab Validation capability                 | Manual, SoC-specific                                                                                                              | Standard Test Guide Based                                 | Standard Test Guide Based,<br>More Labs On-Line                               |  |  |

| Data analysis                             | ASCII datalogs, manual summaries, lengthy analysis                                                                                | Semi - automated summaries, quicker analysis              | STDF, automated summaries, fast analysis                                      |  |  |

| Test issue resolution                     | Poor tester-to-lab correlation, slow, iterative                                                                                   | Excellent tester-to-lab correlation, fast, few iterations | Excellent tester-to-lab correlation, fast, few iterations                     |  |  |

| Propagating changes                       | Lengthy for both pattern development and bring-up                                                                                 | Reasonably fast                                           | Acceptably Quick                                                              |  |  |

### Acknowledgements

- SerDes Design Team

- SerDes IP Wrapper Team

- Test and Product Development Teams

- Validation and Compliance Lab Teams

- Software Teams

- Applications Teams

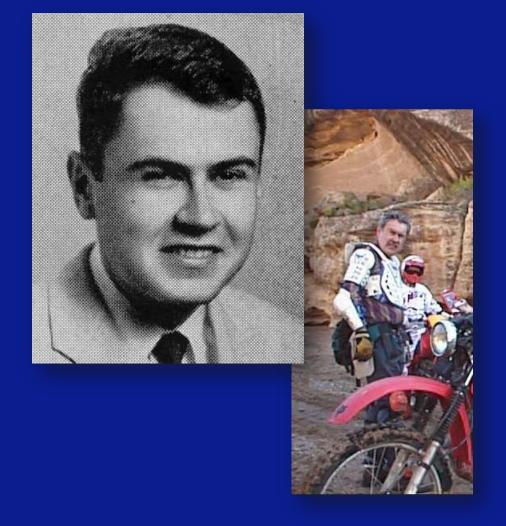

#### **Dedication**

Richard (Dick) Adlhoch Nov 1939 – Dec 2022

#### References

- 1. https://www.digikey.com/es/maker/blogs/2018/71st-anniversary-of-the-transistor

- 2. Common Public Radio Interface Specification 4.2, September 2010

- 3. Fibre Channel Methodologies for Jitter and Signal Quality Specification MJSQ, T11.2 / Project 1316-DT/ Rev 14.1, June 5, 2005

- 4. IEEE 1149.6™: IEEE Standard for Boundary Scan Testing of Advanced Digital Networks Std IEEE 1149.6, 2003 and 2015

- 5. IEEE 1687<sup>TM</sup> 2014: IEEE Standard for Access and Control of Instrumentation Embedded within a Semiconductor Device, November 2014

- 6. IEEE 802.3z<sup>TM</sup> 1998, June 1998

- 7. IEEE 802.3ae<sup>TM</sup> 2002, August 2002

- 8. IEEE Std 802.3ap<sup>TM</sup> 2007, May 2007

- 9. IEEE Std 802.3ba<sup>™</sup> 2010, June 2010

- 10. IEEE Std 802.3bj<sup>TM</sup> 2014, June 2014

- 11. IEEE Std 802.3<sup>TM</sup> 2022, May 2022

- 12. OIF-CEI-03.1: Common Electrical I/O (CEI) Electrical and Jitter Interoperability agreements for 6G+ bps, 11G+ bps and 25G+ bps I/O, February 18, 2014

- 13. PCI-Express™ Base Specification 2.0, December 2006

- 14. PCI-Express™ Base Specification 3.0, November 2010

- 15. PCI-Express™ Base Specification 4.0 v1.0, September 2017

- 16. RapidIO™ Interconnect Specification Part 6: 1x/4x LP-Serial Physical Layer Specification 1.3, June 2005

- 17. Serial ATA<sup>TM</sup> Revision 2.6, February 2007

- 18. Serial ATA<sup>TM</sup> Revision 3.0, June 2009

- 19. Serial ATA™ Revision 3.2, 2013