# Drive More Than Two Pin Levels With DPU-16

**Evan Chen & Kristine Chen Teradyne SEG, China ADC**

**TERADYNE**

#### **TestConX China 2022**

Robots, Machine Learning, & More

#### **Contents**

- Background and Requirements

- ETS-88 and DPU-16

- Two Methods to Drive 3 Pin Levels

- Drive More Than 3 Levels

- Q&A

Drive More Than Two Pin Levels With DPU-16

2022

### **Background and Requirements**

- With the fast development of semiconductor technology in the world, there's a tendency to reduce the device size and redundant pin count.

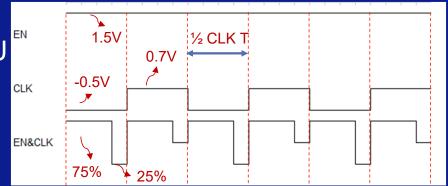

- A device pin combines EN pin and CLK pin to limit the pin count in scan chain structure.

- The combined signal drives three levels in total, normally we use DPU to drive high/low, that is 2 levels

- 0-75% of each period is EN signal,

75%-100% is CLK signal

Drive More Than Two Pin Levels With DPU-16

2022

#### **Introduction of ETS-88**

- ETS-88 is a mixed signal automated testing environment, testing a wide variety of devices including: simple analog, high precision, high voltage, high current / power, automotive etc.

- Eagle test system offers high throughput, low cost for Single site, Multi-site and Index Parallel Applications

Drive More Than Two Pin Levels With DPU-16

2022

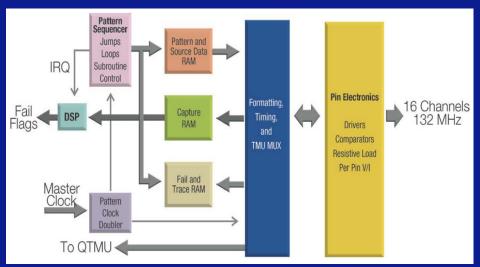

#### **Introduction of DPU-16 board**

- DPU-16 is a commonly used instrument for digital tests

- It provides 16 full-featured digital I/O channels

- Supporting vector rates up to 132 MHz(DDR mode)

DPU-16 Block Diagram

Drive More Than Two Pin Levels With DPU-16

2022

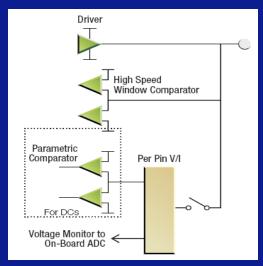

#### **Pin Electronics**

- Independent programmable drive and receive levels per pin

- Drive pin state: 0, 1, T, Z

- Receive pin state: H, L, X, V, M

Pin Electronics Diagram

Drive More Than Two Pin Levels With DPU-16

2022

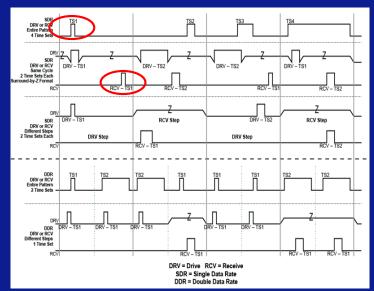

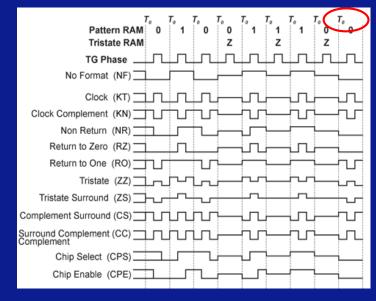

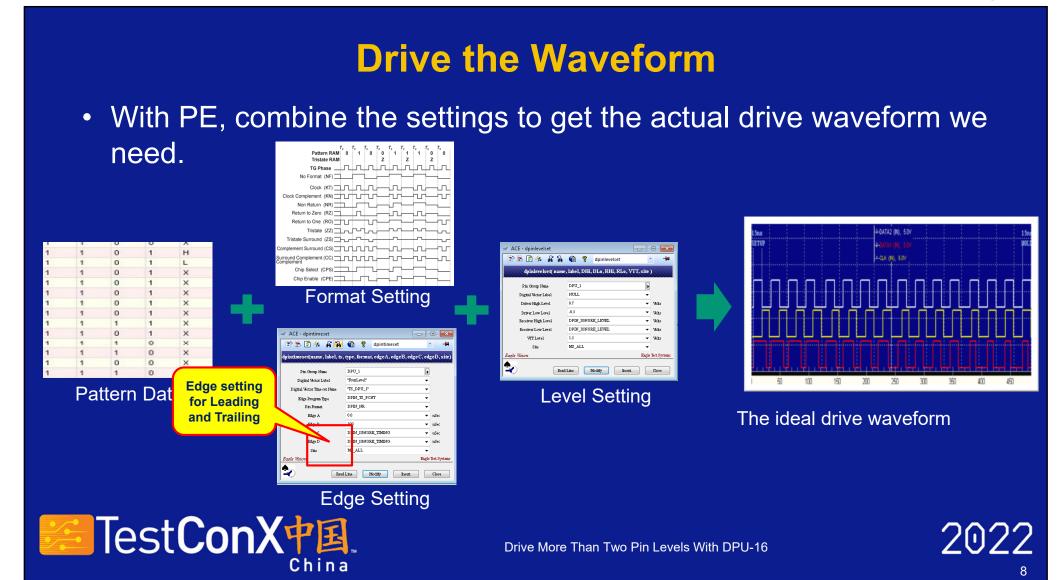

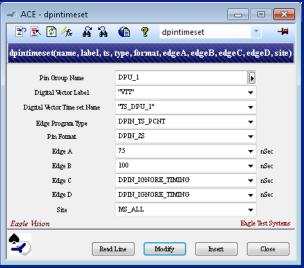

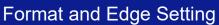

# **Data Format and Edge setting**

- Data format: specify the level change within a period

- Edge set: specify when to have the level change

Timeset Application for DPU-16 Pin Modes

TO:Period Clock, generate the timing reference

**DPU-16 Digital Data Formats**

Drive More Than Two Pin Levels With DPU-16

2022

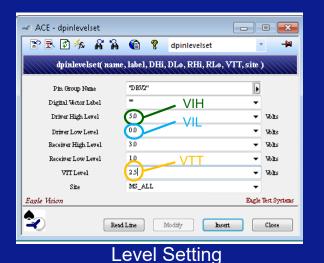

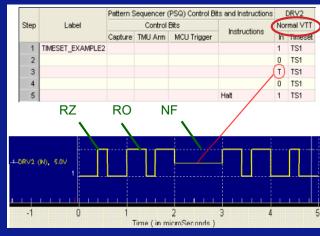

# VTT Drive Mode(the 3<sup>rd</sup> Level)

- Three drive levels: drive high, drive low, VTT level

- VTT level is 50 Ω output impedance, -1.0 to +7.0 V

- Restrict: format is not available on VTT level

TestConX中国

Define Pin as VTT type

VTT Mode Setting in Pattern

Drive More Than Two Pin Levels With DPU-16

2022

)

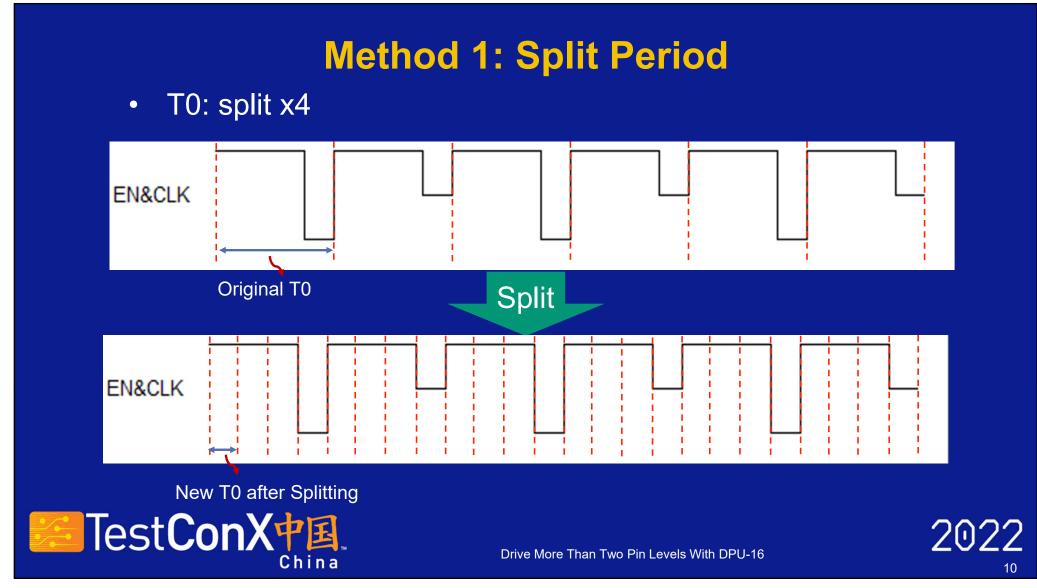

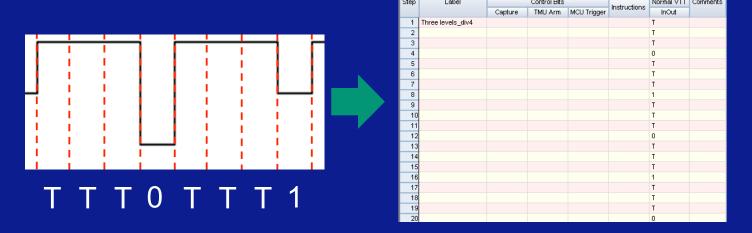

# **Method 1: Split Period**

Pattern to describe the waveform

• Restrict: Need more store memory. Need to translate the pattern data.

Is it possible to drive the levels with original T0? Yes!

Drive More Than Two Pin Levels With DPU-16

2022

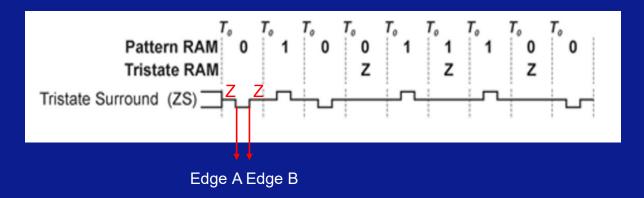

# Method 2: With Format Tristate Surround(ZS)

• The format *Tristate Surround* means the level before edge A and after edge B is set to Z(VTT level).

In our case, we can set the edge A to 75% of the whole period, edge B as the end of a period.

Drive More Than Two Pin Levels With DPU-16

2022

Session 4

# Method 2: With Format Tristate Surround(ZS)

- No need to split T0, save store memory.

- No need to translate the data, easy to create the pattern data.

Pattern Data

Drive More Than Two Pin Levels With DPU-16

2022

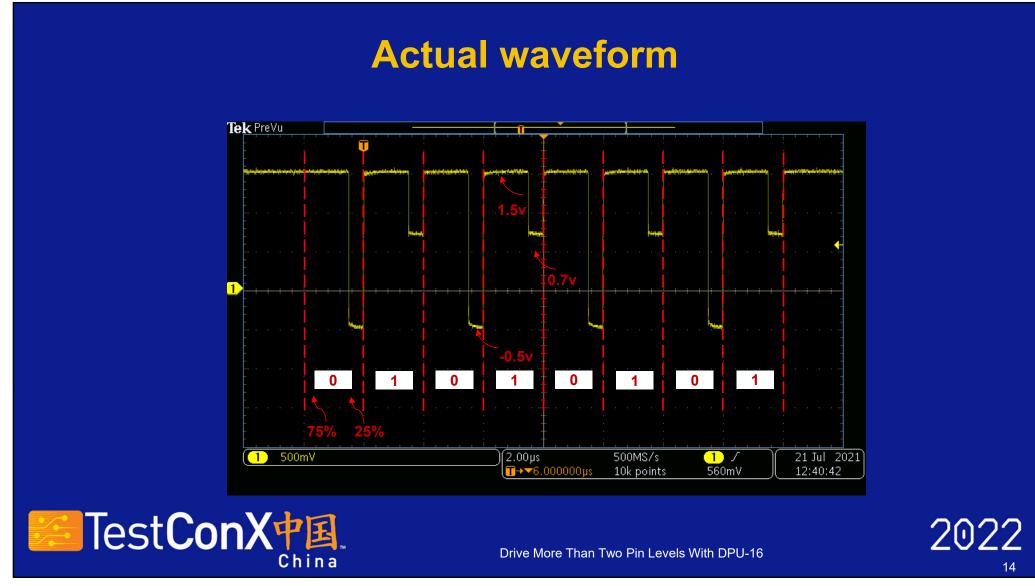

#### **Drive More than 3 Levels**

- One more complexed case:

- One device pin combines pin1 and pin2

- VIL1 and VIH1 on pin1, VIL2 and VIH2 on pin2

- the combined signal drives four levels in total

- One DPU channel can't achieve, take into two DPU channels

Drive More Than Two Pin Levels With DPU-16

2022

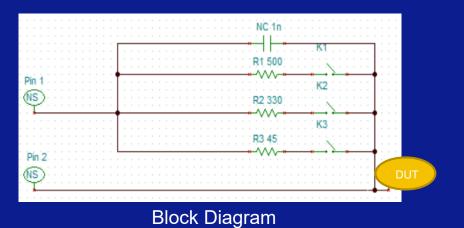

# **Block Diagram**

- Pin1 and Pin2 connect R to device pin

- Pin1 drive VIL1, VIH1 while Pin2 drive Hiz

- Pin2 drive VIL2, VIH2 while Pin1 drive Hiz

Drive More Than Two Pin Levels With DPU-16

2022

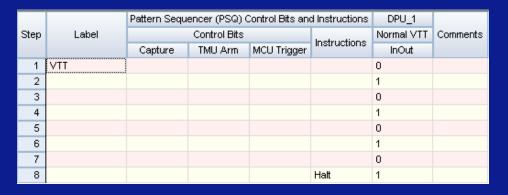

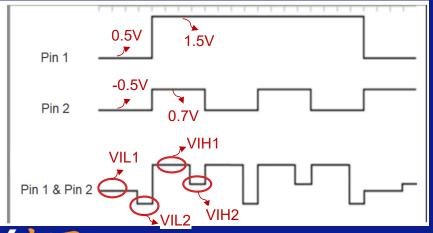

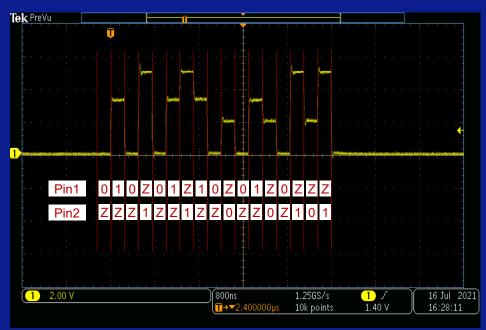

#### **Pattern and Waveform**

One more complex vector data needed

| Step | Label     | Pattern Sequencer (PSQ) Control Bits and Instructi |         |             |              | Pin1   |         | Pin2   |         |          |

|------|-----------|----------------------------------------------------|---------|-------------|--------------|--------|---------|--------|---------|----------|

|      |           | Control Bits                                       |         |             | Instructions | Normal |         | Normal |         | Comments |

|      |           | Capture                                            | TMU Arm | MCU Trigger | Instructions | InOut  | Timeset | In     | Timeset |          |

| 1    | FourLevel |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| 2    |           |                                                    |         |             |              | 1      | TS_Pin1 | Z      | TS_Pin2 | V2       |

| 3    |           |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| 4    |           |                                                    |         |             |              | Z      | TS_Pin1 | 1      | TS_Pin2 | V4       |

| - 5  |           |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| - 6  |           |                                                    |         |             |              | 1      | TS_Pin1 | Z      | TS_Pin2 | V2       |

| - 7  |           |                                                    |         |             |              | Z      | TS_Pin1 | 1      | TS_Pin2 | V4       |

| 8    |           |                                                    |         |             |              | 1      | TS_Pin1 | Z      | TS_Pin2 | V2       |

| 9    |           |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| 10   |           |                                                    |         |             |              | Z      | TS_Pin1 | 0      | TS_Pin2 | V3       |

| 11   |           |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| 12   |           |                                                    |         |             |              | 1      | TS_Pin1 | Z      | TS_Pin2 | V2       |

| 13   |           |                                                    |         |             |              | Z      | TS_Pin1 | 0      | TS_Pin2 | V3       |

| 14   |           |                                                    |         |             |              | 0      | TS_Pin1 | Z      | TS_Pin2 | V1       |

| 15   |           |                                                    |         |             |              | Z      | TS_Pin1 | 1      | TS_Pin2 | V4       |

| 16   |           |                                                    |         |             |              | Z      | TS_Pin1 | 0      | TS_Pin2 | V3       |

| 17   |           |                                                    |         |             |              | Z      | TS_Pin1 | 1      | TS_Pin2 | V4       |

| 18   |           |                                                    |         |             | Halt         | 0      | TS_Pin1 | 0      | TS_Pin2 | V1       |

Pattern to Drive Four Levels

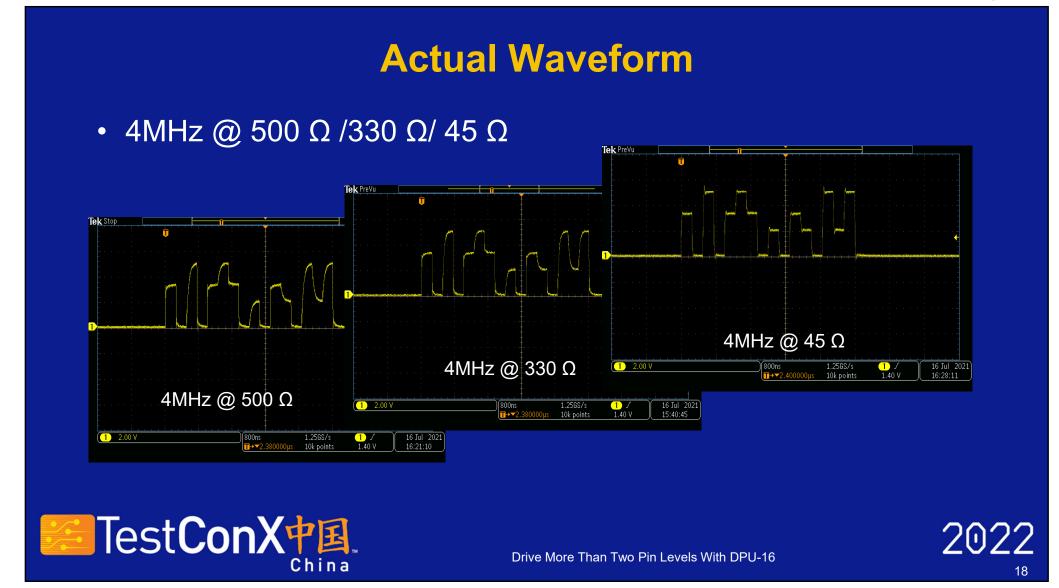

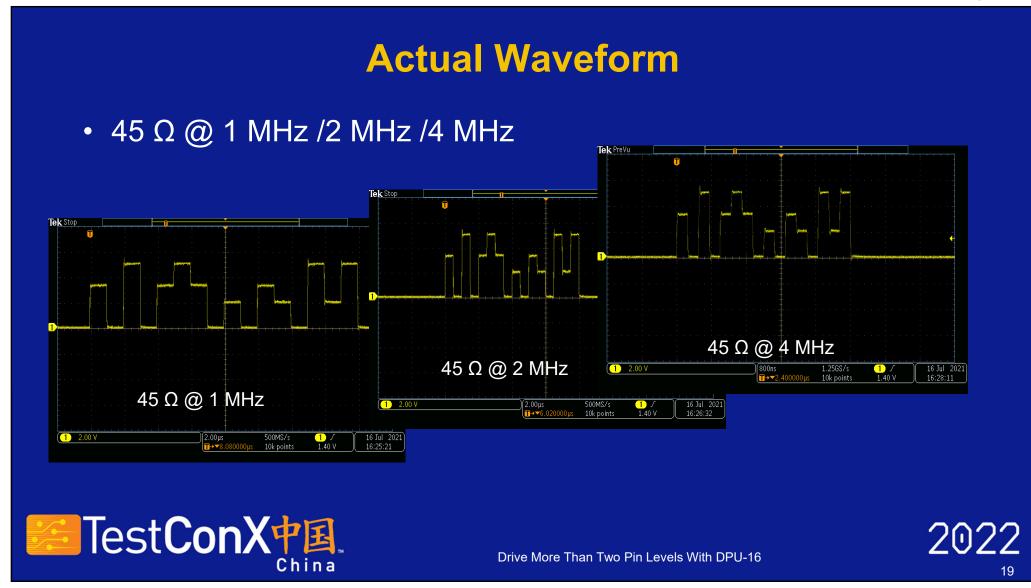

**Actual Waveform**

TestConX中国

Drive More Than Two Pin Levels With DPU-16

2022

/

Robots, Machine Learning, & More

# **Something Need to Add**

- The higher the resistance is, the slower the signal rises/falls

- Resistor select suitable value to fit impedance matching

- Resistor connects to device as close as possible to reduce spikes when high speed signal

2022

Drive More Than Two Pin Levels With DPU-16

# With Thanks to Our Sponsors!

# smiths interconnect

Your Global Partner for Innovative Semiconductor Test Solutions

# Enabling the Next Generation of Technology Through Advanced Test Solutions

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the TestConX China 2022 virtual event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at TestConX China. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

TestConX, TestConX China, the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.