## **TWENTY THIRD ANNUAL**

May 1 - 4, 2022

**TestConX**

DoubleTree by Hilton Mesa, Arizona ACCINE

© 2022 TestConX– Image: f11-photographer / iStock

Signal Integrity

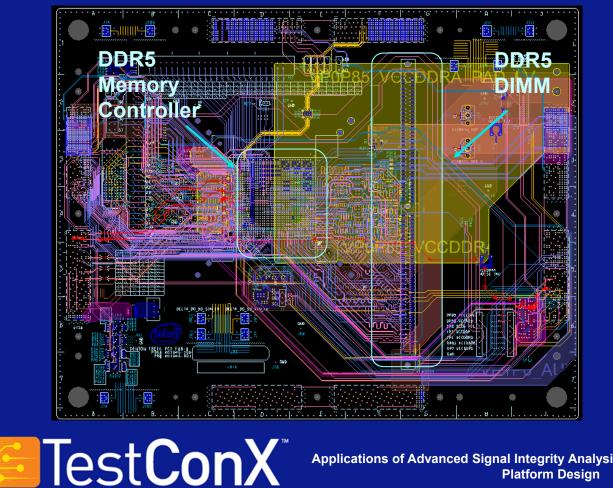

## Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

Xiao-Ming Gao Intel Corporation

Mesa, Arizona • May 1-4, 2022

TestConX Workshop

www.testconx.org

May 1-4, 2022

Signal Integrity

### TestConX 2022

### Agenda

- DDR5 overview

- DDR5 validation platform design challenges

- Advanced signal integrity analysis

- Summary

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

Signal Integrity

### TestConX 2022

### **DDR5** Overview

- High bandwidth with data rate up to 8400 MT/s

- High capacity DIMMs up to 256 GB

- Reduced I/O voltage 1.1 V

- Improved I/O speed by use of DFE and CTLE \*

- Better power performance using on-DIMM power management IC modules

Decision Feedback Equalization and Continuous Time Linear Equalization

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Session 8 Presentation 1

Signal Integrity

### **DDR5 Validation Platform Design Challenges**

- Accelerated rate of standards evolution

- Shortened design and validation cycles

- Reduced link budget and channel margins

- Tremendous routing constraints on platform design

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Signal Integrity

### **Advanced Signal Integrity Analysis**

- Pre-layout DDR5 channel simulation

- 3D EM (Electromagnetic) model extractions of interconnect

- Post-layout simulation flow

- Tabbed-line design for crosstalk reduction

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Session 8 Presentation 1

Signal Integrity

Signal Integrity

### **TestConX 2022**

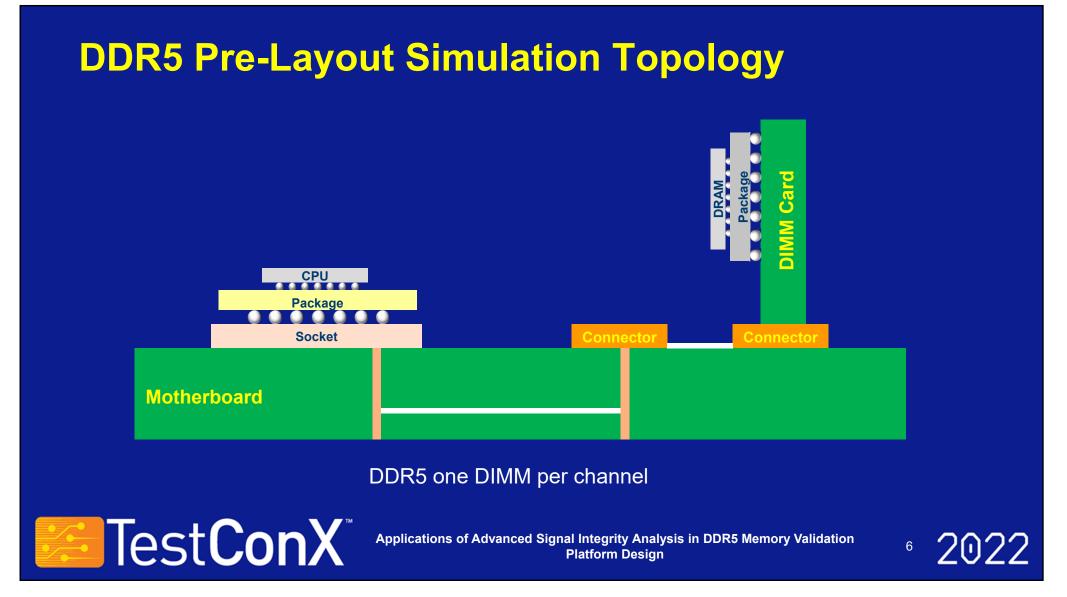

### **Pre-Layout Signal Integrity Analysis**

- Coverage of pre-layout DDR5 simulation

- Define channel topology

- Evaluate platform enablers such as crosstalk reduction and impedance discontinuity optimization

- Analyze silicon and interconnect parameters sensitivity

- Performance optimization

- Identify end-to-end solution space

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

Signal Integrity

### TestConX 2022

### **Simulation Model Assumptions**

- Memory controller buffer models (IBIS-AMI \*)

- CPU and DRAM package models

- Socket

- Motherboard trace and vias

- DIMM connector

- DIMM card

- \* IBIS: Input/output Buffer Information Specification IBIS-AMI: IBIS Algorithmic Modeling Interface.

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### **TestConX 2022**

### **Channel and Silicon Parameter Analysis**

- Interconnect impedance mismatch

- Channel insertion loss, routing length

- Crosstalk impact

- CPU and DRAM equalization optimization

CTLE (Continuous-Time Linear Equalizer)

DFE (Decision Feedback Equalizer)

- Random and deterministic jitter (Rj and Dj)

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

www.testconx.org

Signal Integrity

### TestConX 2022

### **Channel and Silicon Parameters Optimization**

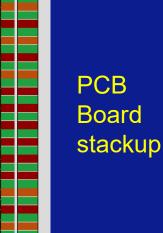

- PCB stackup selection

- Routing layer study

- Channel impedance optimization

- Via type and back drilling

- DDR5 solution space

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

www.testconx.org

Signal Integrity

### **TestConX 2022**

Signal Integrity

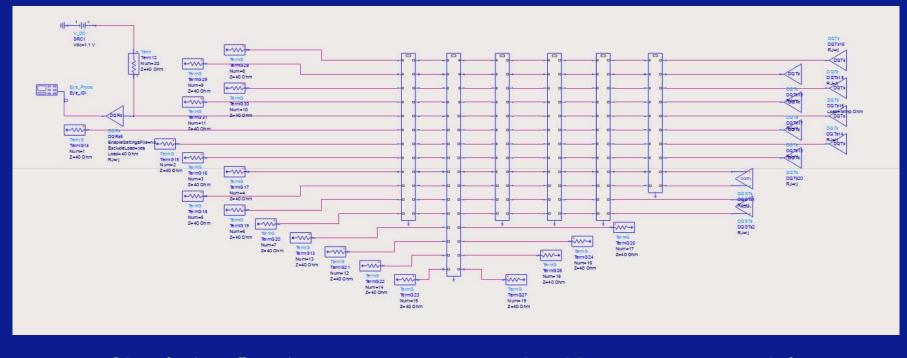

### **DDR5 DQ Read Simulation Flow**

Simulation flow integrates parameterized interconnect models

TestConX<sup>®</sup>

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Signal Integrity

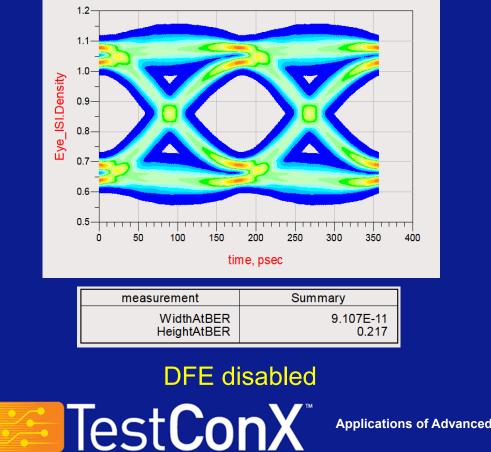

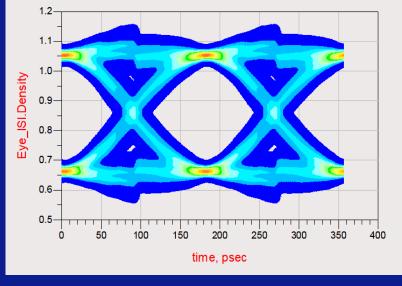

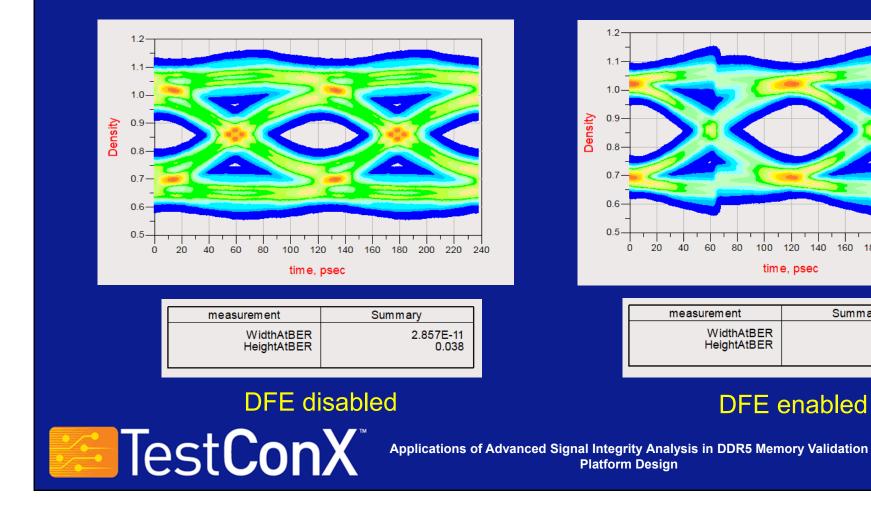

### DDR5 DQ Read Eye Margins at 5600 MT/s

| measurement | Summary   |

|-------------|-----------|

| WidthAtBER  | 1.027E-10 |

| HeightAtBER | 0.275     |

#### **DFE** enabled

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

TestConX Workshop

Signal Integrity

### TestConX 2022

### **DDR5 Post-Layout Simulation**

- PCB stackup and manufacturing technology definition

- Via implementations (through hole, blind, staggered/stacked micro vias) models

- Routing constraints creations

- Component placements, board layout, and routing

- Topology models extraction using 3D EM solvers

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

Signal Integrity

### **TestConX 2022**

Surface TOP Conductor

Dielectric

L02\_GND Plane Dielectric L03 SIG Conduc

Dielectric L04 GND Plane Dielectric

L05\_SIG Conduc Dielectric

L06\_GND Plane Dielectric L07 SIG Condu Dielectric LOS GND Plane Dielectric L09 SIG Conduc

Dielectric 10 L10 GND Plane Dielectric L11\_FWR Plane

Dielectric 12 L12\_FWR Plane Dielectric

13 L13\_FWR Plane Dielectric 14 L14\_PWR Plane Dielectric 15 L15\_GND Plane Dielectric 16 L16\_SIG Conduct Dielectric

L17\_GND Plane Dielectric 18 L18\_SIG Conduc Dielectric L19\_GND Plane Dielectric L20\_SIG Conduc Dielectric

L21\_GND Plane

Surface

Dielectric L22\_SIG Conduc Dielectric L23\_GND Plane Dielectric BOTTOM Con

17

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation **Platform Design**

SB DQ8 15 DQS1 6 ANSYS

Signal Integrity

### TestConX 2022

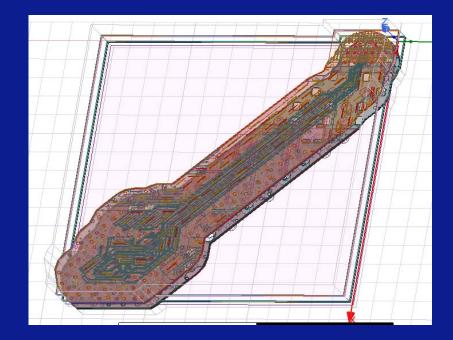

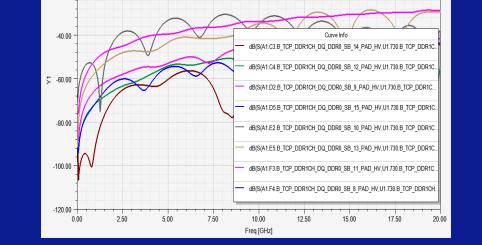

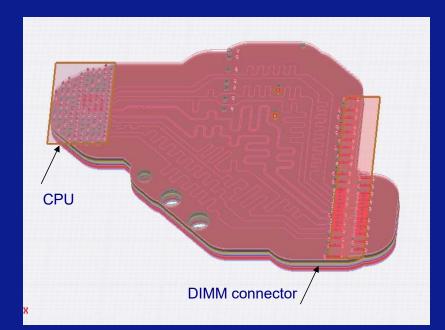

### **3D EM Extraction of DDR5 Package**

CPU Package S Parameter

#### Package 3D model

#### Insertion loss and crosstalk

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

-20.00

TestConX Workshop

www.testconx.org

May 1-4, 2022

Signal Integrity

### TestConX 2022

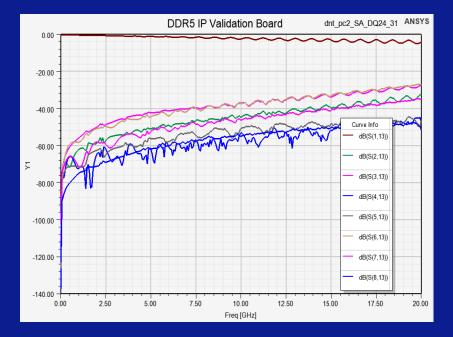

### **3D EM Extraction of DDR5 Board**

### Validation board 3D model

#### Insertion loss and crosstalk

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

TestConX Workshop

www.testconx.org

May 1-4, 2022

### **TestConX 2022**

Signal Integrity

#### **DDR5 Post Layout Simulation Flow** DDR\_PCB DIMM\_Connector DIMM\_Connector DDR\_Package CPU\_Package DDR\_Package DDR\_Package2 ackage Model CAVCTRL emor DQ /lemor Control DQS DMDBI DDR\_Controller DDR\_Controller DDR\_Memory DDR\_Memory1 DDR\_PCB Motherboard **CPU** Package **CPU Buffer** Mother Board **DRAM Package DRAM Buffer DIMM Board** DIMM Connector

### Simulation flow integrates interconnect 3D EM models

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### **TestConX 2022**

Signal Integrity

### DDR5 DQ Read Eye Margins at 8400 MT/s

18

2022

TestConX Workshop

www.testconx.org

180 200

5.298E-11

0.124

Summary

220 240

Signal Integrity

### **TestConX 2022**

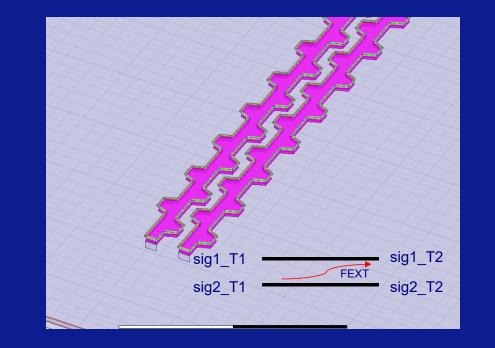

### The Need for Crosstalk Reduction

- High capacity DDR5 platforms such as in data center and high-performance computing

- PCB board routing space is very limited and high-density routings are necessary

- Crosstalk is the bottleneck for DDR5

- Tabbed-line design is a promising enabler

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Signal Integrity

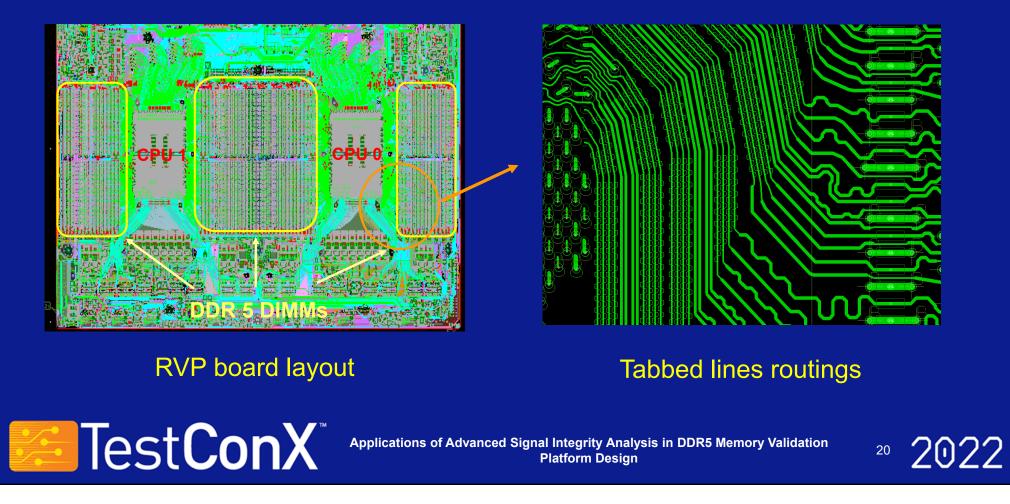

### **DDR5 Reference Validation Platform**

Signal Integrity

### TestConX 2022

### **Tabbed Lines Routings Creation**

CPU pin field tabbed line routing

#### Main region tabbed line routing

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

TestConX Workshop

www.testconx.org

May 1-4, 2022

Signal Integrity

### **TestConX 2022**

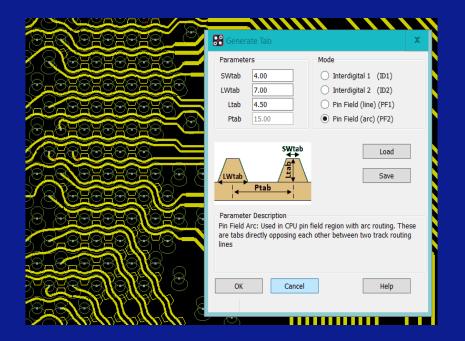

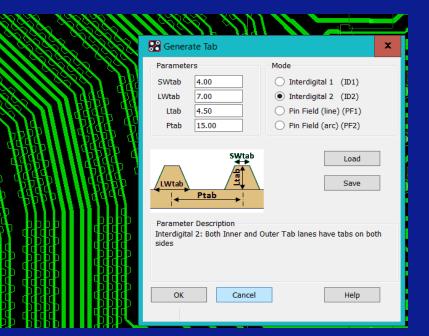

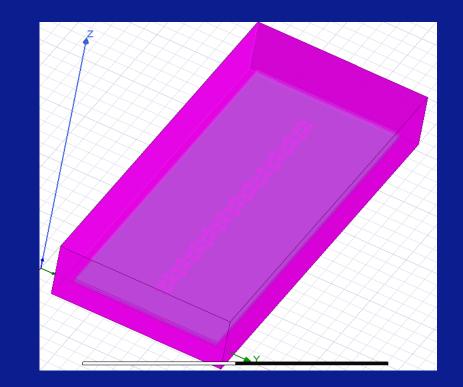

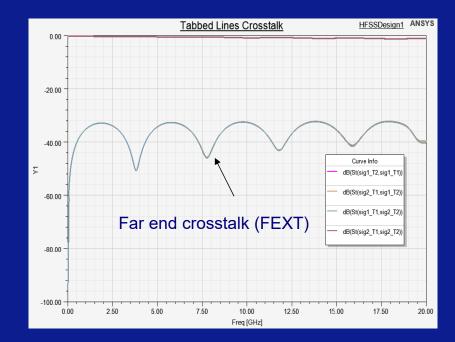

### **Tabbed Lines Crosstalk Optimization**

- Create 3D model

- Use 3D EM solver to generate S parameter

- Optimize following parameters to reduce coupling between two lines

| Parameters |       |       |

|------------|-------|-------|

| SWtab      | 4.00  |       |

| LWtab      | 7.00  |       |

| Ltab       | 4.50  |       |

| Ptab       | 15.00 |       |

|            |       |       |

| LWtab      | Ptab  | SWtab |

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Signal Integrity

### **Optimized Tabbed Lines Crosstalk Performance**

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

Signal Integrity

### **TestConX 2022**

### Summary

- Deployment of new DDR5 memory systems requires rigorous and thorough testing

- Design of DDR5 validation platform is complex and challenging

- Advanced SI analyses guarantee platforms performance can meet design target

- Tabbed-line routings can reduce crosstalk and enable DDR5 in high density memory systems

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### TestConX 2022

Signal Integrity

### References

[1] R Kunze et al., "Crosstalk Mitigation and Impedance Management Using Tabbed Lines," Intel white paper, 2015.

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

### **TestConX 2022**

Signal Integrity

### Acknowledgments

# The author would like to thank Virapandiane Ragavassamy and Kalpit Jha for the discussions

Applications of Advanced Signal Integrity Analysis in DDR5 Memory Validation Platform Design

# With Thanks to Our Sponsors!

## With Thanks to Our Sponsors!

### **COPYRIGHT NOTICE**

The presentation(s) / poster(s) in this publication comprise the Proceedings of the TestConX 2022 workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the TestConX 2022 workshop. This version of the presentation or poster may differ from the version that was distributed at or prior to the TestConX 2022 workshop.

The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors. There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation / poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX", the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.