# 56 Gbps Gigabit Ethernet Ports High Volume Production Wafer Test

Chuong Huynh Multilane Inc.

#### **Abstract**

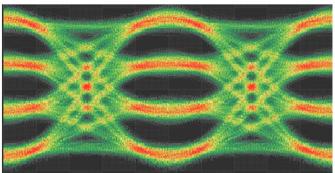

The semiconductor production test industry can benefit from a new class of high-speed external instruments at wafer probe. 400 GbE data center interconnects with 8-lane form factor operates at 28 GBaud PAM4 or 56 Gbps per lane. USB4 operates at 40 Gbps NRZ. PCIeG5 operates at 32 Gbps and PCIeG6 will add PAM4 to PCIeG5. Until now, these types of devices in wafer form could not be fully tested until package test or system level test. By doing high-speed testing earlier in the manufacturing cycle, at-speed wafer level test saves time and cost.

PCIeG5 @ 32 Gbps (NRZ @ 32 Gbps) is tested at BER = 10<sup>-12</sup> Typical eye mask limits are:

|        | ТХ       | RX       |

|--------|----------|----------|

| Width  | 10.9 ps  | 9.375 ps |

| Height | 130 mVpp | 15 mVpp  |

802.3 Ethernet I/O @ 112 Gbps (PAM4 @ 56 GBaud) is tested at BER = 10<sup>-6</sup> Typical eye mask limits are:

|        | TX        | RX        |

|--------|-----------|-----------|

| Width  | ~5 ps     | ~4 ps     |

| Height | ~110 mVpp | <150 mVpp |

#### **Benefits of High-Speed Wafer Test**

- Earlier fault detection saves time & money

- Wafer-level testing may be the only direct I/O testing alternative for die attached inside multichip modules (MCM)

- Wafer parametric data feedback to IC designers and wafer foundries without additional packaging process variability can enable device yield improvement which can directly impact cost of build

#### **Features**

- 56 GBaud PAM4 BERTs & 50 GHz SCOPEs

- → 400/800 GbE, USB4, PCIeG5/6, HDMI

- Test 32 differential lanes in parallel

- → Multisite-ready with GUI-based debug

- 20 cm distance between instruments and device under test (DUT)

- → Minimizes signal path frequency distortion

- Direct docking

- → Further minimizes signal path frequency distortion

- RF Probe technology

- → Field proven methods to probe the wafer I/O pads

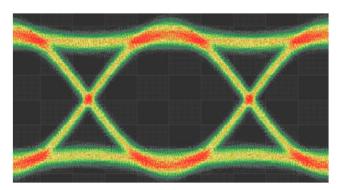

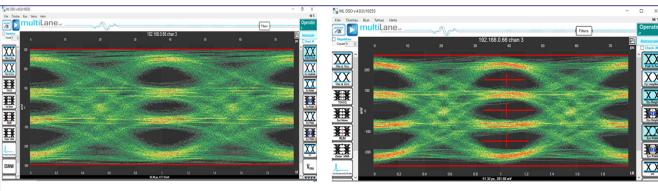

26.5625 GBaud PAM4

(No path distortion correction)

DUT will be rejected

Same PAM4 signal (With path distortion correction)

DUT will PASS

#### 28 GBaud PAM4 real measurements show passing results

- The high-speed signal paths to and from the DUT are compensated by the BERT source and SCOPE measurement instruments

- Results are shown here for 'before' and 'after' signal path compensation

#### **Summary**

We have successfully taken wafer level measurements of 28 GBaud PAM4 signals using an industry standard production tester in a multisite situation to show the viability of production level wafer testing

Source and Measure instruments capable of testing up to 28 GHz Nyquist are allowing IC companies to perform at-speed wafer testing. This helps companies provide better characterization to their IC designers and provide earlier parametric data feedback to the semiconductor foundries. New and expensive MCM packaging techniques may also prevent direct access to these IC's, suggesting another reason why wafer test is desired.

### With Thanks to Our Sponsors!

**Emeritus**

### With Thanks to Our Sponsors!

**Distinguished**

**Industry Partners**

## With Thanks to Our Sponsors!

**Lanyards**

**Tutorial**

**Keynote**

<u>Keycards</u>

**Totebag**

### **COPYRIGHT NOTICE**

The presentation(s) / poster(s) in this publication comprise the Proceedings of the TestConX 2022 workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the TestConX 2022 workshop. This version of the presentation or poster may differ from the version that was distributed at or prior to the TestConX 2022 workshop.

The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors. There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation / poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX", the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.

www.testconx.org