October 27 – 29, 2020 Virtual Event

Archive www.testconx.org

# Next Generation Test Cell / Test Operation

See Tien (Angie) NG Seong Guan (SG) OOI Intel Corporation

### **Contents**

- What is Power Sequencing Test

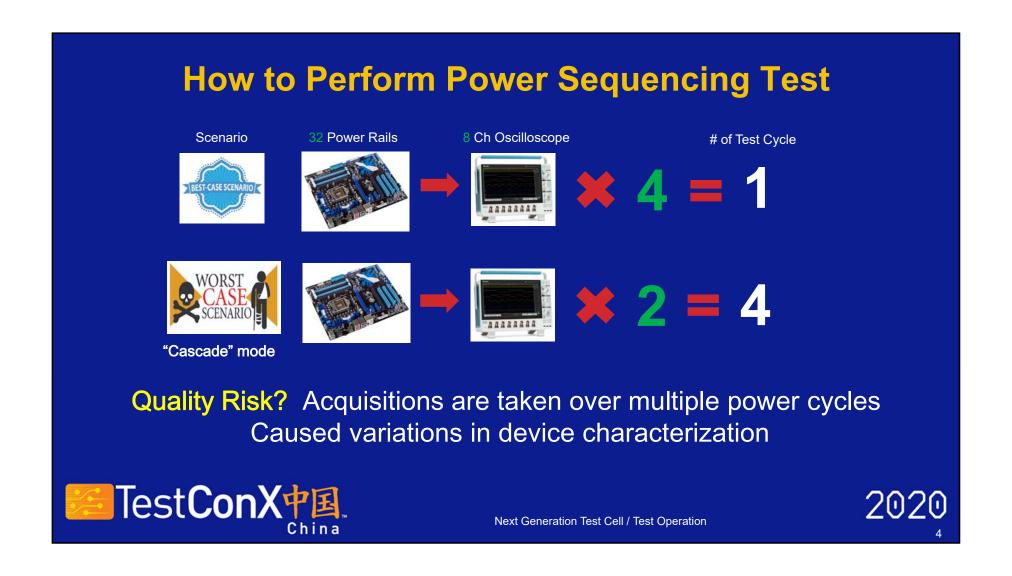

- How to perform Power Sequencing Test

- Cost to perform Power Sequencing Test

- Solution Overview

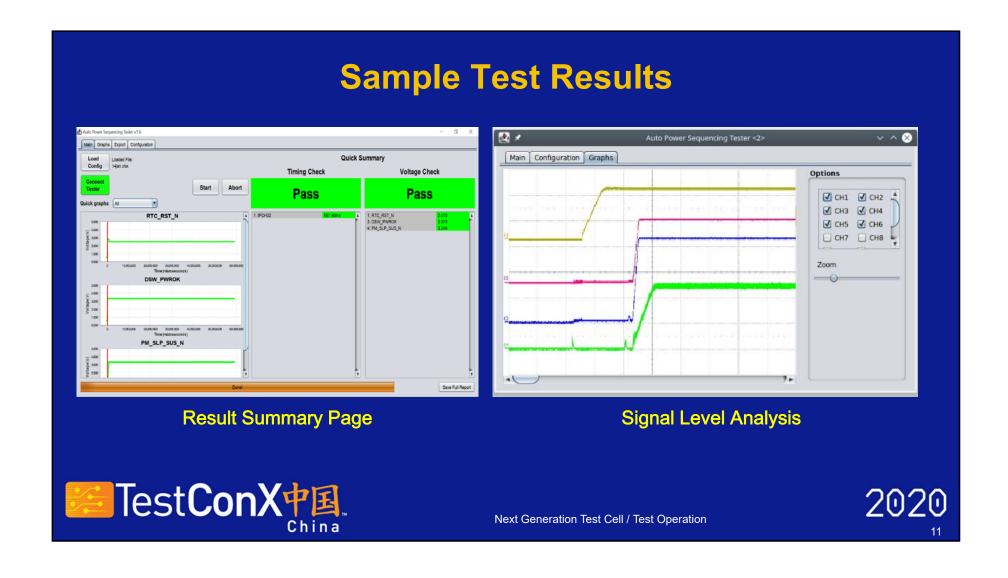

- Sample Test Results

- Summary & Impact of Power Sequencing Tester

- Acknowledgements

Next Generation Test Cell / Test Operation

# **What is Power Sequencing Test?**

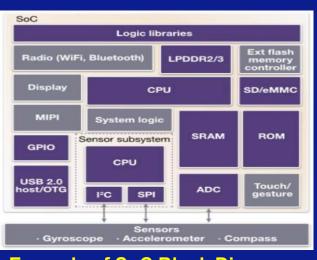

**Example of SoC Block Diagram**

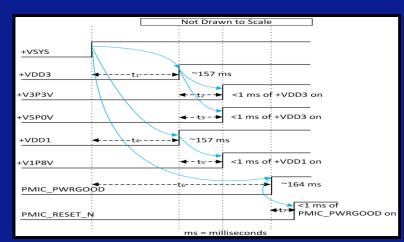

**Power On Timing Sequences**

- Objective: Measure Power-On & Power-Down Timings & Voltages for SoC blocks

- Criticality: Ensure products functionality

Next Generation Test Cell / Test Operation

High frequency / 5G and High Speed Data

# **Cost to Perform Power Sequencing Test**

### **Requirements:**

- Oscilloscopes

- Hours to execute power sequencing test

- Engineer/technician head count support

### **Variations:**

- Manual characterization method by using naked eyes

- · Result accuracy may vary by person/skills

### **Current Limitation:**

- Long execution time

- High cost to perform the test

- Inaccurate test results

- In-depth technical skills required

- Physical touch support required

Next Generation Test Cell / Test Operation

2020

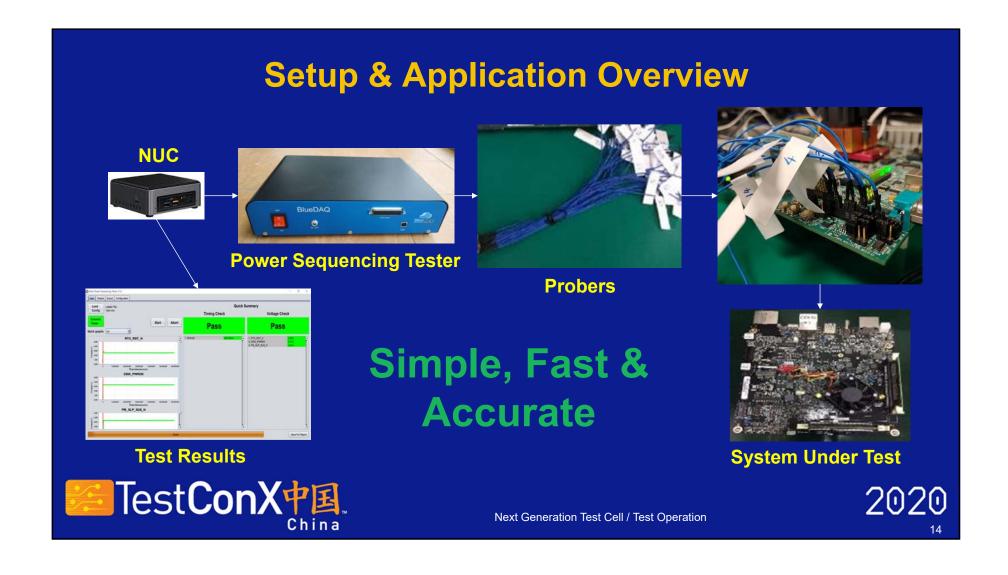

### **Solution Overview**

- Applied Field Programmable Gate Array (FPGA) to construct a customize multichannels oscilloscope to perform Power Sequencing Test.

- All test results are captured and compared to a pre-defined recipe (pass condition) and report out detail summaries

Next Generation Test Cell / Test Operation

# **Hardware Specifications**

- Up to 1MSPS sampling rate per channel

- 36 single ended channels

- 8-bit resolution per channel

- 1Mohm input impedance

- 3 selectable input voltage ranges (0-5V and 0-20V and +/-10V)

- 1-minute data capture bandwidth per channel

- Simultaneous sampling with same clock for all channels

- 1 selectable single channel edge triggering (rising/falling) with adjustable threshold

- User selectable trigger position (as 0-99% of total capture buffer)

**Power Sequencing Tester**

**Probers**

Next Generation Test Cell / Test Operation

2020

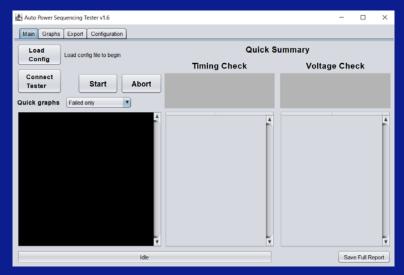

# **Software Specifications**

- load config file, save to config file, arm/disarm (start/stop), generate report, save wave data file

- Individual waveform display for each channel, with vertical/horizontal zoom features

- Detail waveform display tool for advance control/settings

- Selectable time range (max 1-minute)

- User defined pass/fail condition, with profile/recipe settings

- Voltage rule checking features

**Software GUI**

Next Generation Test Cell / Test Operation

2020

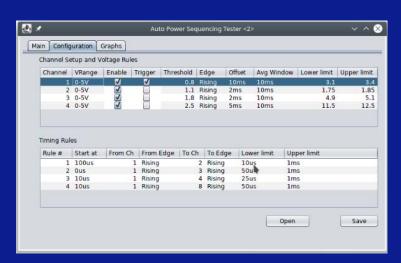

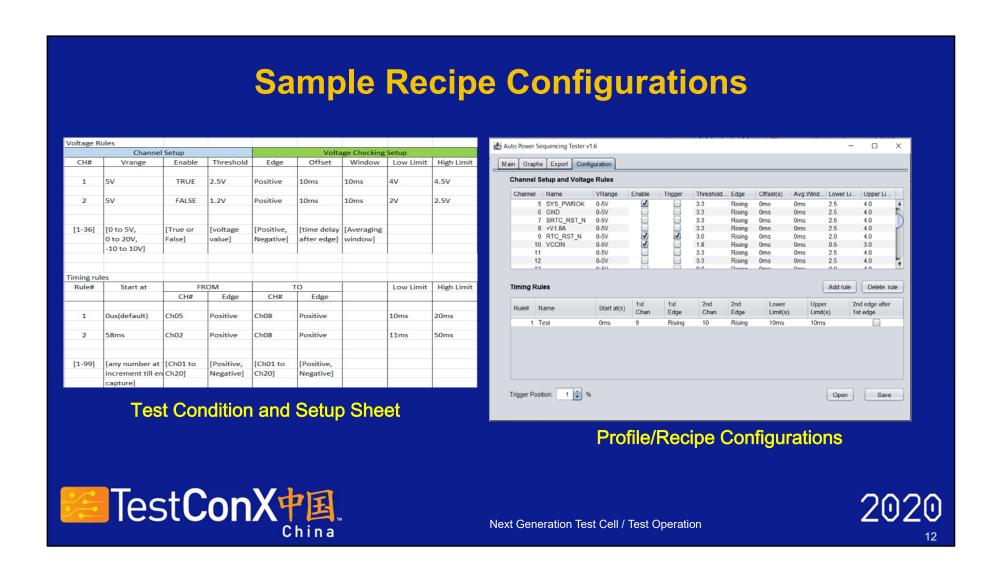

# **Profile/Recipe Settings and Configuration**

- Selectable voltage range for each channel (0-5V, 0-20V, +/-10V)

- Timing checking rules

- Voltage checking rules

- Edge detection for timing check

- User specify triggering channel, edge (rise/fall)

- Voltage threshold and voltage delta selection

- Profile/recipe save features

**Profile/Recipe Configurations**

Next Generation Test Cell / Test Operation

#### **Power Sequencing Tester Report**

Software Version: 1.6

Creation Date: 2020-01-14T14:22:46.7301587+08:00[Asia/Singapore]

Config file: C:\Users\WorkStation 1\Desktop\PST\PST\_v1p4\14jan.xlsx

Overall result: Pass Voltage check result: Pass Timing check result: Pass

#### Voltage checking rules and results

Showing only enabled channels.

| Chan | Name         | Meas. Voltage Range | Channel Enable | Trigger | Threshold | Trigger Edge | Meas. offset time | Avg. window time | Lower Limit | Upper Limit | Measured value | ResultF | ail reason |

|------|--------------|---------------------|----------------|---------|-----------|--------------|-------------------|------------------|-------------|-------------|----------------|---------|------------|

| 1    | RTC_RST_N    | 0-5V                | True           | False   | 1.5V      | Rising       | 10.0000ms         | 10.0000ms        | 2.0V        | 3.0V        | 2.097V         | PASS    |            |

| 3.   | DSW_PWROK    | 0-5V                | True           | True    | 1.5V      | Rising       | 10.0000ms         | 10.0000ms        | 2.5V        | 4.0V        | 3.314V         | PASS    |            |

| 4    | PM_SLP_SUS_N | 0-5V                | True           | False   | 1.5V      | Rising       | 10.0000ms         | 10.0000ms        | 2.5V        | 4.0V        | 3.307V         | PASS    |            |

#### Timing checking rules and results

| Rule # | Name   | Start checking from | From Channel | From Channel Edge | To Channel | To Channel Edge | Lower Limit | Upper Limit | 2nd edge only after 1st edge | Measured value | Result | Fail reason Chart |

|--------|--------|---------------------|--------------|-------------------|------------|-----------------|-------------|-------------|------------------------------|----------------|--------|-------------------|

| 1      | tPCH32 | -1.0000ms           | 3            | Rising            | 4          | Rising          | 95.0000ms   | 5.0000s     | true                         | 1.0212s        | PASS   | ⇒ <sub>Go</sub>   |

### **Sample Test Report in HTML form**

Next Generation Test Cell / Test Operation

2020

# **Summary & Impact of Power Sequencing Tester**

| Components              | Improvements |  |  |  |  |

|-------------------------|--------------|--|--|--|--|

| Hardware Cost           | 78.57%       |  |  |  |  |

| Test Time               | 99.33%       |  |  |  |  |

| Headcount               | 100.00%      |  |  |  |  |

| Characterization Method | 100.00%      |  |  |  |  |

| Result Accuracy         | 100.00%      |  |  |  |  |

### **Improvement Summary**

- Quality Impact: Eliminate human dependencies and improve test quality and time

- Business Impact: Strengthen Intel's customers engagement with state of art technologies

- · Competitive advantage in SoC validation: Quality, Accuracy & Speed

Next Generation Test Cell / Test Operation

2020

# **Acknowledgements**

- Eric Chan VP in Intel IoTG (Internet of Thing Group)

- Board of Directors in Intel Malaysia Design Center (MDC)

- Goh, Kean Hean Engineering Lab Manager

- Ooi, Seong Guan Product Owner & Staff Technologist

2020

Next Generation Test Cell / Test Operation

# With Thanks to Our Sponsors!

### **Premier**

Since 1979

Honored

**Distinguished**

# **Test Tooling Solutions Group**

### Innovate. Collaborate. Deliver.

TTS Group is dedicated to bring the best possible testing solutions to our customers and to help solve some of the most challenging issues in test and tooling today.

Total headcount of 400 specialists

Total production area of 400,000 sqft. for Probe Pin and Socket operations

Total investment of USD 75 Million

### COPYRIGHT NOTICE

The presentation(s)/poster(s) in this publication comprise the proceedings of the TestConX China 2020 virtual event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at TestConX China. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

TestConX, TestConX China, the TestConX logo, and the TestConX China logo are trademarks of TestConX. All rights reserved.

www.testconx.org