Session 7 Presentation 1

Heating Up - Thermal

# Implementation of WL-HTOL for Early Reliability Assessments

#### KRISHNA MOHAN CHAVALI GLOBALFOUNDRIES

Virtual Event • May 11-13, 2020

TestConX Workshop

www.testconx.org

May 11-13, 2020

www.testconx.org

- Industry standard BI and HTOL are done on package level.

- New Scheme: Wafer Level full functional stress for BI & ELFR:

- At high temperature and voltages.

- Saves Time: 6~8 weeks;

- Huge Cost savings: BIBs w/o full WLBI Systems.

- This concept can be used where faster feedback is needed:

- Early Reliability Assessments on circuits / products

- For Process changes and New Product Introductions (NPI's)

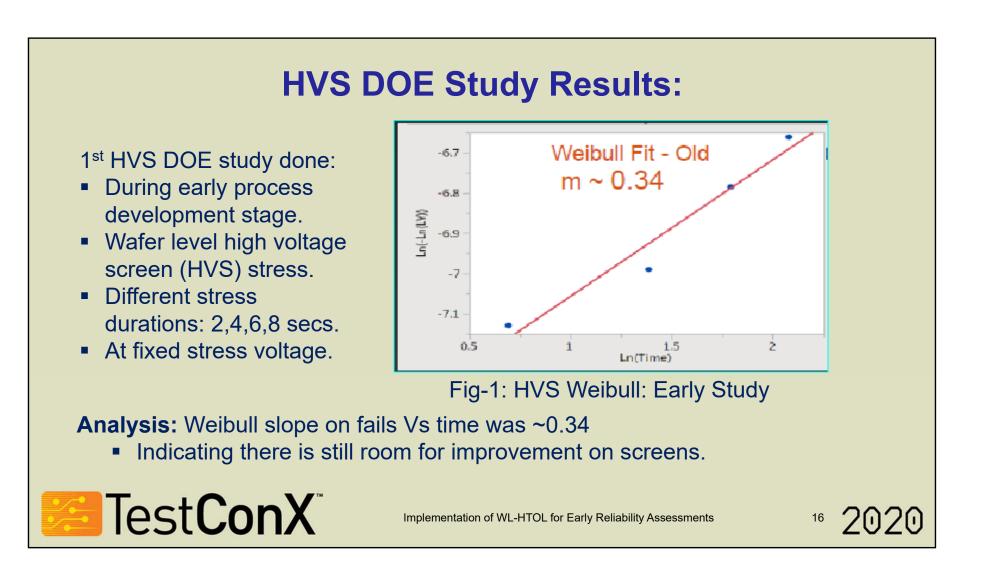

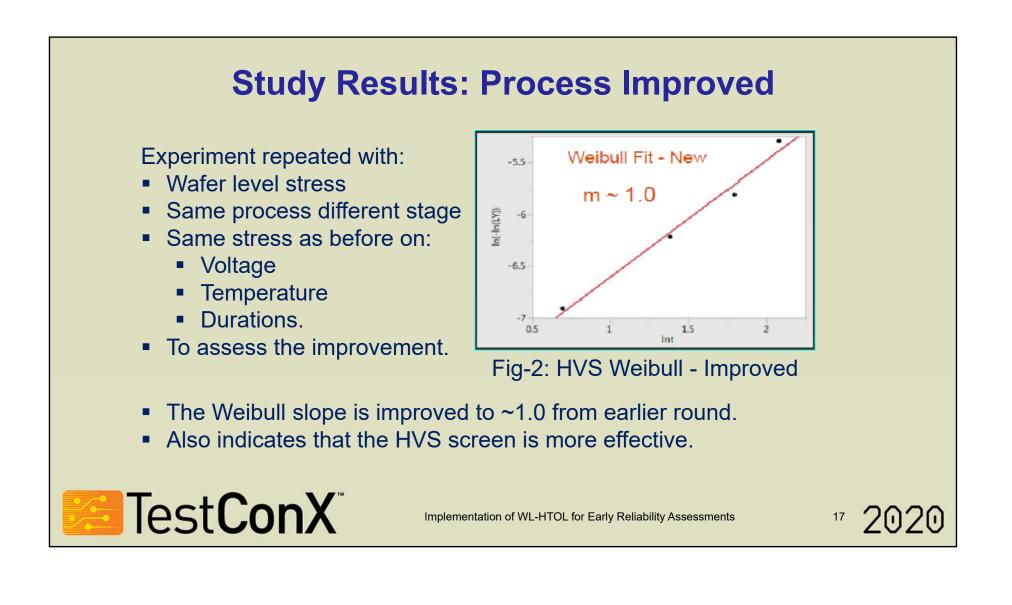

- For Process DOE's, Kinetic studies and HVS/DVS etc.,

- During product/process development.

Heating Up - Thermal

## Purpose

- Reliability qualification need package stresses. e.g. ELFR, HTOL

- Long setup times & costs: Bumping bump masks.

- Packaging: Substrate Design, tooling: 12~15 weeks.

- WLBI Systems: High costs & long design time 6-9 months.

- New scheme: Done at wafer level, full circuit functional stress.

- Implemented with high temp. probe cards and existing tester/s.

- Stress to meet early qualification needs: done in @2-3 weeks.

- Reduces high costs of BIBs, WLBI systems & long lead times.

Session 7 Presentation 1

Heating Up - Thermal

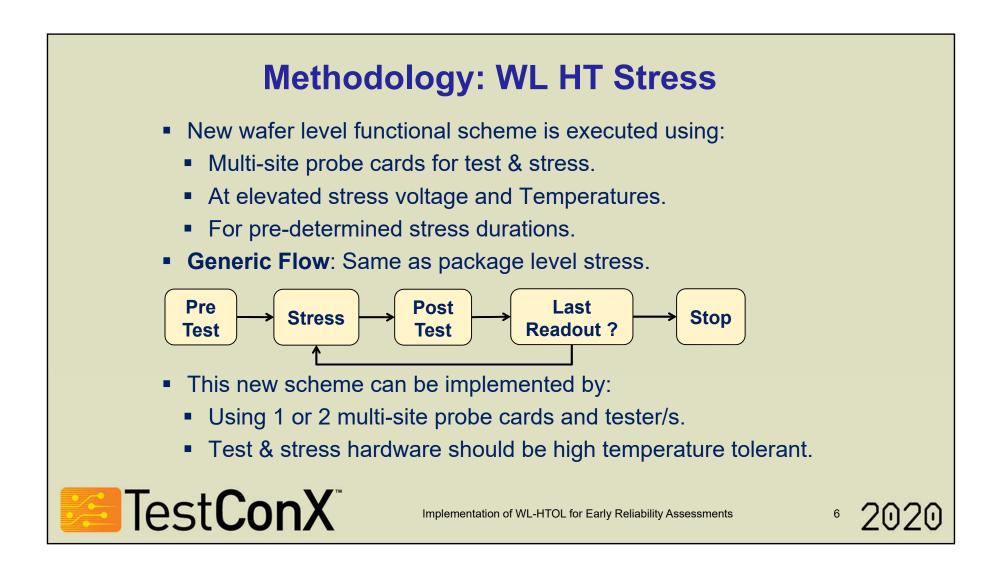

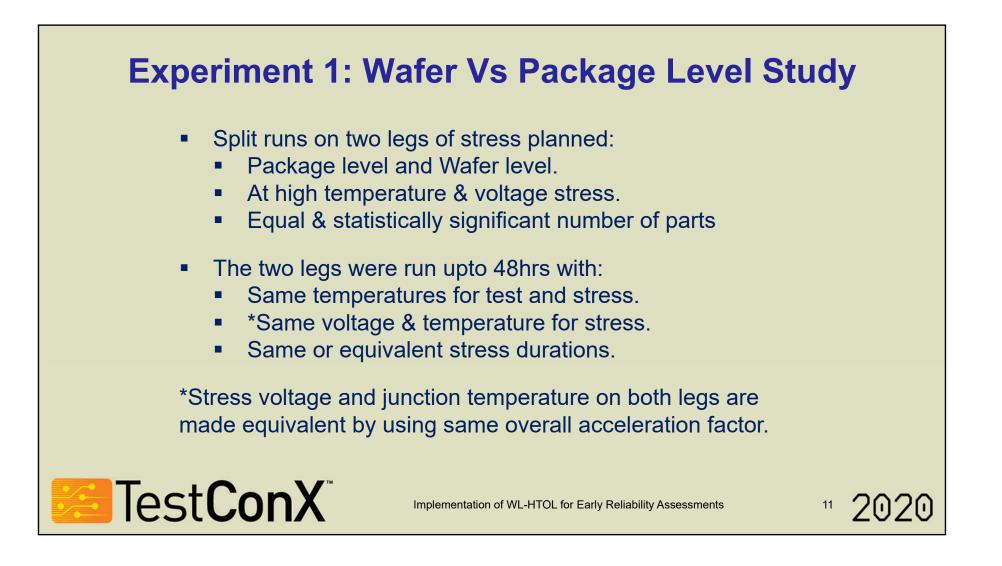

Before full implementation of the scheme:

- A correlation study to be run

- Wafer level and Package level.

- To compare, correlate & validate results.

- Statistically significant equal number of parts for legs.

- Standard LPTD or AQL tables can be used.

- Die locations: from all zones & across wafer.

- Dies from >3 wafers: wafer-to-wafer variability.

- Wafers from >1 lot: lot-to-lot variability.

Implementation of WL-HTOL for Early Reliability Assessments

2020

Test**ConX**

- Probe cards suitability at high temp. continuous stress.

- Use same set of parametric and functional tests as BI.

- Same stress: voltage, temperature & speed etc.

- If IR drop & self heating issues exists:

- Stress Voltage & Temp. levels to be adjusted.

- When used for DVS/HVS and burn-in:

- Set adequate levels of voltage & temperature.

- Validate with stress results after screens.

Heating Up - Thermal

www.testconx.org

www.testconx.org

Session 7 Presentation 1

Session 7 Presentation 1

Heating Up - Thermal

Various advantages of this method are:

- Demonstrated on different experiments done.

- Implemented on multiple technology nodes.

- As a replacement for package level BI & Screens.

- At different stages of process and

- Product's maturity stages.

The application purpose, probe card types, cycle time (CT) and cost savings Vs package level burn-in are listed. All the details are compared to estimate cost Savings  $\rightarrow$

| <b>Projects Implemented &amp; Cost Savings</b><br>Cost savings from different projects implemented w.r.t package level are: |                         |                 |                   |                    |                                |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------|-------------------|--------------------|--------------------------------|--|--|--|--|

| Tech.<br>Node                                                                                                               | Test Chip &<br>Purpose  | #of PC<br>sites | Stress<br>Details | Cycle Time<br>Days | Relative<br>savings<br>% to BI |  |  |  |  |

| 1                                                                                                                           | SRAM ERA                | 4               | Tj:125C 24h+24h   | 7                  | 42%                            |  |  |  |  |

| 2                                                                                                                           | eFuse Qual<br>CCS & CVS | 25              | @85C, 36h+36h     | 12                 | 51%                            |  |  |  |  |

|                                                                                                                             | SRAM ERA                | 9               | Tj:125C, 24h+24h  | 9                  | 54%                            |  |  |  |  |

| 3                                                                                                                           | SRAM ERA                | 4               | Tj:125C, 24h+24h  | 12                 | 48%                            |  |  |  |  |

|                                                                                                                             | SRAM<br>HVS DOE         | 4               | 25-85C, 24h+RO    | 12                 | 46%                            |  |  |  |  |

> Average of @50% cost savings achieved with this WL stress scheme.

Implementation of WL-HTOL for Early Reliability Assessments

19 2020

Test**ConX**®

#### **Cycle Time Savings**

#### Cycle time comparison: Package Vs Wafer Level

| Conventional Package Level Burn- | Typical | ١   | Wafer Level Burn-In Flow        | Typical  |

|----------------------------------|---------|-----|---------------------------------|----------|

| In Flow (at Module Level)        | TAT     |     | (at wafer probe)                | TAT      |

| Fabout Sort & Data Review        | 3 days  |     | Fabout Sort & Data Review       | 3 days   |

| Ship to Bump House               | 4 days  |     | Receive & Queue for tester      | 0.5days  |

| Bumping, Post Bump Sort/HVS      | 7 days  | 5   | Setup Tester & Stabilize at HT  | 0.5 days |

| Sort review, Wfr slection+OQA    | 2 days  | ] [ |                                 |          |

| Ship to Assembly House           | 4 days  | ] [ |                                 |          |

| Packaging TAT at Assembly for FC | 21 days | 1 [ |                                 |          |

| Ship to Test House/Lab           | 4 days  | 1 [ |                                 |          |

| Handler/Tester setup FT@3Temps   | 3 days  | ] [ | T0 FT at 3 Temperatures         | 2 days   |

| Load, Run 24hrs & Unload         | 2 days  | ] [ | Load, Run 24hrs & Unload        | 1 day    |

| T24 FT at 3 temperatures         | 3 days  | ] [ | T24 FT at 3 temperatures        | 2 days   |

| Load, Ramp & Run 24hrs & Unload  | 2 days  | ] [ | Load, Ramp & Run 24hrs & Unload | 1 days   |

| T48 FT at 3 temperatures         | 3 days  | ]   | T48 FT at 3 temperatures        | 2 days   |

| Verifications & Report           | 2 days  |     | Verifications & Report          | 2 days   |

| Converntional Burn-In TAT        | 60 days |     | Fast Wafer Burn-In TAT          | 14 days  |

- Gain of @6~7 weeks using WLHT Scheme.

- Very useful during process development stage.

- Faster feedback to process changes or improvements.

Heating Up - Thermal

Longer stress times & larger part counts call for:

- Tester/s dedication and bandwidth [6].

- Probe cards with high temperature design.

- Swapping between stress and test modes.

- if single tester used, increased total time.

- Stress might limit to 12hrs or 24hrs intervals.

- Readout at 12 and 24hrs & continue.

- Prior understanding of Chip Package Interaction (CPI) on fails necessary Vs module burn-in.

Test**ConX**

Implementation of WL-HTOL for Early Reliability Assessments

22 2020

#### Conclusion

- Simple wafer level high temp. stress concept.

- For functional & product stress w/o full fledged WLBI

- Implemented and experimentally validated.

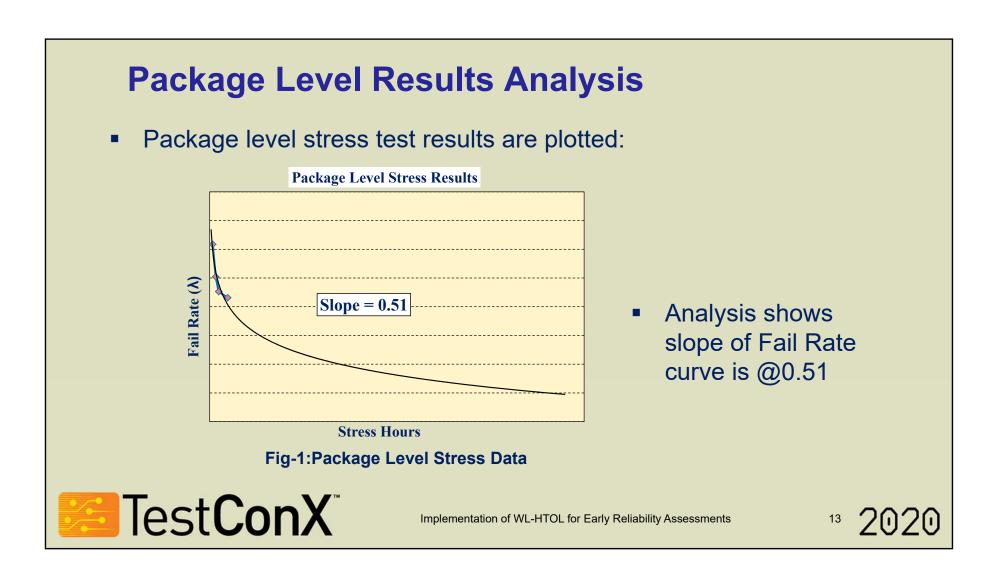

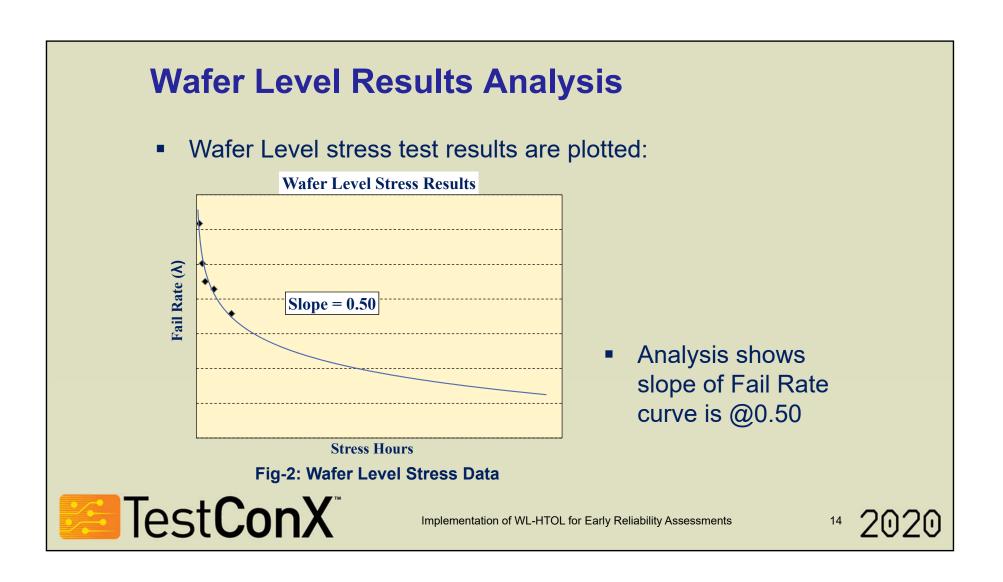

- Results correlated with conventional package burn-in.

- For smaller stress hours: ELFR & screens.

- Limitation on longer stress hours >168hrs for HTOL.

- By design of high temperature probe cards.

- This scheme enables:

- Shorter learning cycles faster feedback.

- HVS / DVS screen and kinetic studies.

- Quick functional reliability assessments.

Test**ConX**®

Implementation of WL-HTOL for Early Reliability Assessments

23 2020

Session 7 Presentation 1

### TestConX 2020

1) Wafer Level Burn-In Decision Factors by Steve Steps, AEHR, Burn-In & Test Strategies Workshop 2013, Mesa, AZ, US. 2) Wafer-level Test and Burn-in (WLB). Copyright © 2001-2004 www.EESemi.com

3) Introduction to Wafer Level Burn-In, Semiconductor Wafer Test by William R. Mann, 2002, South West Test Workshop.

4) A New Wafer Level Latent Defect Screening Methodology for Highly Reliable DRAM Using a Response Surface Method, by Junghyun Nam, et. al, International Test Conference (ITC) 2008. IEEE International, pp. 1-10, 2008, ISSN 1089-3539.

5) Wafer level burn-in by D. R. Conti; J. Van Horn, 50th Electronic Components and Technology Conference Proceedings,

2000, Pages 815-821.

6) Sea of Leads (SoL) ultrahigh density wafer-level chip input/output interconnections for giga scale integration (GSI), by M.S. Bakir, H.A. Reed, H.D. Thacker, C.S. Patel, P.A. Kohl, K.P. Martin, J.D. Meindl, Electron Devices IEEE Transactions on, vol. 50, pp. 2039-2048, 2003, ISSN 0018-9383.

7) Test Pattern Ordering for Wafer Level Test During Burn-In, Sudarshan Bahukudimbi, Krishnendu Chakrabarty, 26th IEEE VLSI Test Symposium, 2008, Pages 193-198.

8) Assessing Intrinsic and extrinsic end-of-life risk using functional SRAM wafer level testing by Y. Mamy Randriamihaja et. all, IEEE IRPS-2015.

9) Qualifying a Process for Higher Burn-In Voltage or Over Drive Application by Krishna Mohan Chavali, Burn-In & Test Strategies Workshop 2017 AZ US.

10) Statistical Method for setting up Safe Screen Voltage for Products by Krishna Mohan Chavali, Burn-In & Test Strategies Workshop 2017 AZ, US.

Heating Up - Thermal

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2020 TestConX Virtual Event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2020 TestConX Virtual Event. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

#### www.testconx.org

TestConX Workshop