Session 6 Presentation 3

Creative Checking - Validation

# 99% Validation Efficiency through Cloud Power Sequencing

Angie Ng See Tien Seong Guan Ooi Intel Corporation

Virtual Event • May 11-13, 2020

Session 6 Presentation 3

Creative Checking - Validation

### Contents

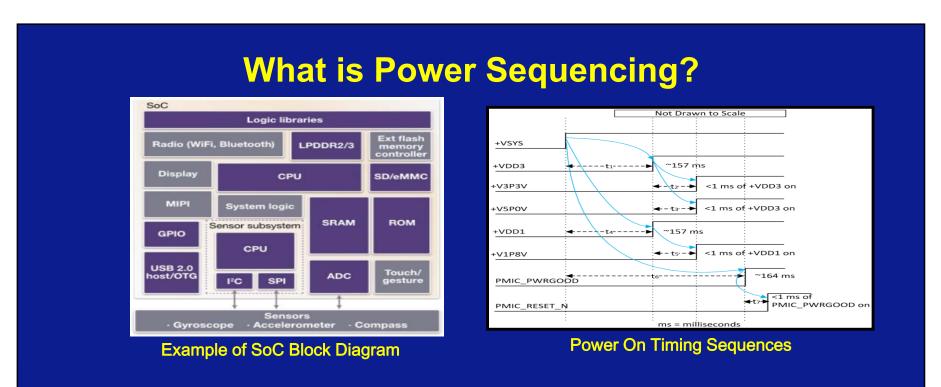

- What is Power Sequencing

- Problem Statements

- Objectives

- Solution Overview

- Impact of Cloud Power Sequencing

- Summary

- Acknowledgements

Creative Checking - Validation

- Measure Power On and Power Down timings and Voltages

- Critical to ensure products functionality

TestConX<sup>™</sup> 99% Validation Effic

99% Validation Efficiency through Cloud Power Sequencing

<sup>3</sup> 2020

Creative Checking - Validation

### **Problem Statement**

- Cost to perform power sequencing test

- 4 x Tektronix MSO58 scope = \$140,000

- Power sequencing test time = 5 hours/test

- Engineer/technician involved = 2 heads

- Characterization method = manual

- Result accuracy = vary by person/skills

#### - Disadvantages:

- Slow

- High cost

- Inaccurate

- In-depth technical skills required

- Physical touch required

#### Estimation of Performing Power Sequencing Test

Session 6 Presentation 3

Creative Checking - Validation

TestConX Workshop

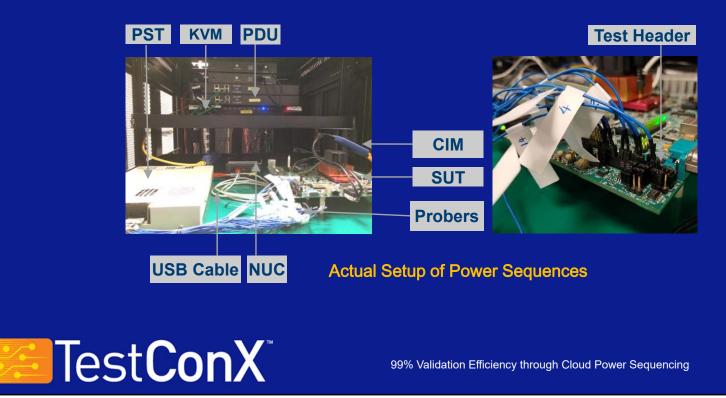

### **Solution Overview**

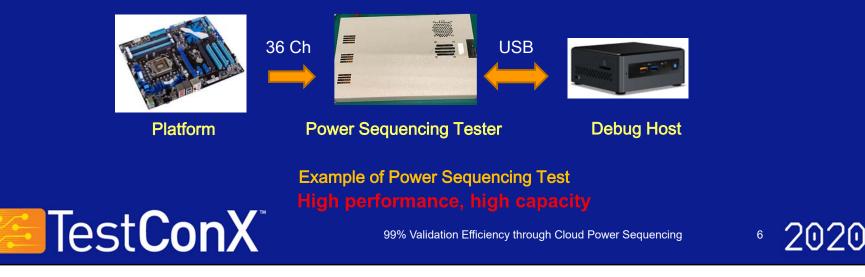

Power Sequencing Tester serve as a multi-channel oscilloscope that

- Software : Applying FPGA (Field Programmable Gate Array) & Verilog scripting for the automation.

- Hardware Design : 36 probers & 4 GNDs are connected to platform to measure voltage and timing requirements.

- Dashboard : Graphical User Interface (GUI) is developed to allow easy entry of power rules, voltage specification. The graphs are plotted after post processing.

- Test Report : test results can be retrieved from debug host and report out as pass/fail in html/Pdf format.

Creative Checking - Validation

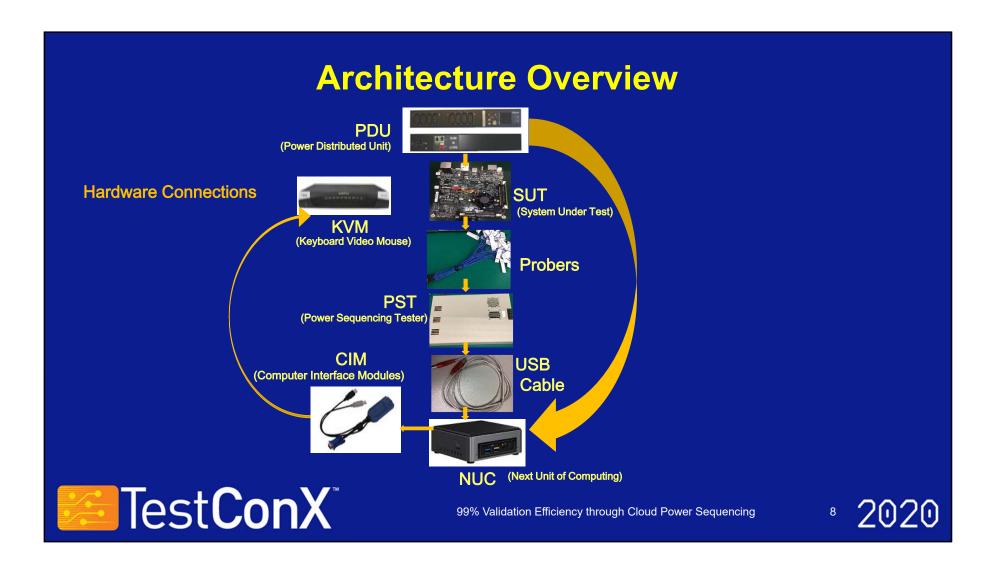

### **Architecture Overview**

- KVM & PDU is to enable remote access and power cycling.

- NUC is connected to KVM via CIM cable.

- NUC can be configured as Virtual Machine.

**PST Solution Specifications:**

- 36 simultaneous measurement channels

- 8-bit resolution/channel

- Sampling rate at 1M/second/channel

- Input impedance @  $1M\Omega$

- 3 voltage range (0-5V, 0-20V, +/-10V)

- · Stored up to 1min of measurement data

- Single channel edge triggering (rising/falling), with adjustable threshold and selectable channel

Session 6 Presentation 3

### TestConX 2020

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

### **Architecture Overview**

- NUC can be configured as Virtual Machine (VM).

- VM is connecting to Cloud Environment to enable maximum efficiency.

Session 6 Presentation 3

### TestConX 2020

Creative Checking - Validation

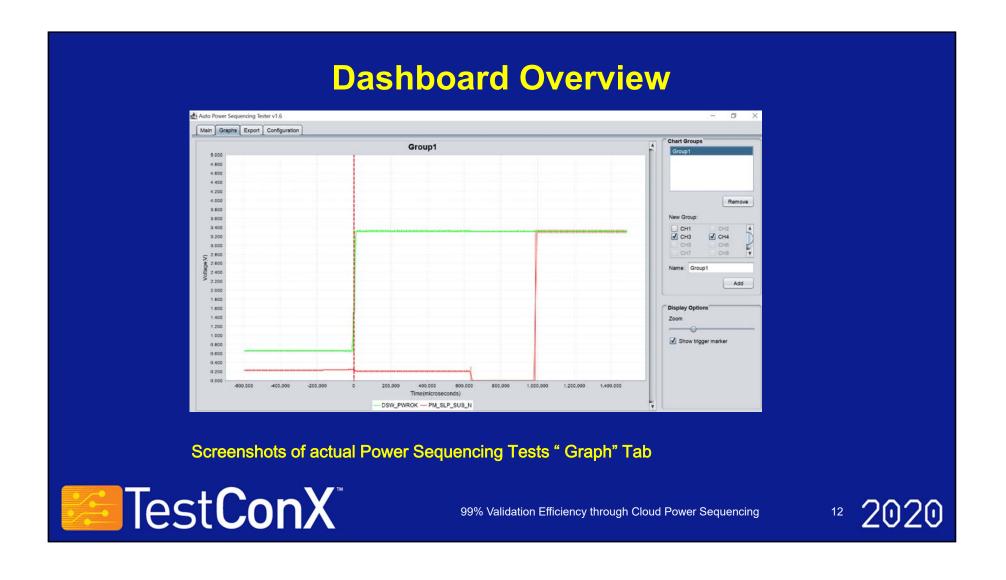

### **Dashboard Overview**

Screenshots of actual Power Sequencing Tests " Main Tab

TestConX®

Creative Checking - Validation

|           | phs Export Con                                                                          |                                                              |             |             |                                                      |                                                                    |                                                             |                                                             |                                               |                                                      | _ |  |  |

|-----------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|-------------|-------------|------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------|---|--|--|

| Channe    | I Setup and Volta                                                                       | VRange                                                       | Enable      | Trigger     | Threshold                                            | Edge                                                               | Offset(s)                                                   | Avg.Win                                                     | d Lower Li.                                   | Upper Li                                             |   |  |  |

|           | 5 SYS_PWROK<br>6 GND<br>7 SRTC_RST_N<br>8 +V1.8A<br>9 RTC_RST_N<br>10 VCCIN<br>11<br>12 | 0-5V<br>0-5V<br>0-5V<br>0-5V<br>0-5V<br>0-5V<br>0-5V<br>0-5V |             |             | 3.3<br>3.3<br>3.3<br>3.0<br>1.8<br>3.3<br>3.3<br>3.3 | Rising<br>Rising<br>Rising<br>Rising<br>Rising<br>Rising<br>Rising | Oms<br>Oms<br>Oms<br>Oms<br>Oms<br>Oms<br>Oms<br>Oms<br>Oms | 0ms<br>0ms<br>0ms<br>0ms<br>0ms<br>0ms<br>0ms<br>0ms<br>0ms | 2.5<br>2.5<br>2.5<br>2.0<br>0.5<br>2.5<br>2.5 | 4.0<br>4.0<br>4.0<br>4.0<br>3.0<br>4.0<br>4.0<br>4.0 | 5 |  |  |

| Timing I  | Rules<br>Name                                                                           | Start at(s)                                                  | 1st<br>Chan | 1st<br>Edge | 2nd<br>Chan                                          | 2nd<br>Edge                                                        | Lower<br>Limit(s                                            |                                                             |                                               | Delete r<br>2nd edge after<br>1st edge               |   |  |  |

| 1         | Test                                                                                    | 0ms                                                          | 9           | Rising      | 10                                                   | Rising                                                             | 10ms                                                        | 10                                                          | ms                                            |                                                      |   |  |  |

| Trigger P | osition: 1 🛉                                                                            | 6                                                            |             |             |                                                      |                                                                    |                                                             |                                                             | Open                                          | Save                                                 |   |  |  |

Session 6 Presentation 3

Creative Checking - Validation

Creative Checking - Validation

|                                                                                                                                                                                                       |                                                                                                            | Power Sequencing                                                       | Fester Report                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| oftware Version: 1.6<br>reation Date: 2020-01-14T14:22:46.7301587+0<br>onfig file: C:\Users\WorkStation 1\Desktop\PST<br>verall result: Pass<br>oltage check result: Pass<br>iming check result: Pass |                                                                                                            |                                                                        |                                                                                  |

| oltage checking rules and results                                                                                                                                                                     |                                                                                                            |                                                                        |                                                                                  |

| han #Name Meas. Voltage Range/Channel Er   RTC_RST_N 0.5V True   DSW_PWROK 0.5V True   PM_SLP_SUS_N0-3V True                                                                                          | Time 1.5V Rising 10.0000   True 1.5V Rising 10.0000   True 1.5V Rising 10.0000   False 1.5V Rising 10.0000 | ms 10.0000ms 2.5V 4.0V                                                 | Imit Measured value Result Fail reasor   2.097V PASS   3.314V PASS   3.307V PASS |

| iming checking rules and results                                                                                                                                                                      |                                                                                                            |                                                                        |                                                                                  |

| ule #Name Start checking from From ChannelFrom Cl<br>tPCH32 -1.0000ms 3 Rising                                                                                                                        |                                                                                                            | ver LimitUpper Limit2nd edge only after 1st edg<br>0000ms 5.0000s true | eMeasured value Result Fail reason Cl<br>1.0212s PASS                            |

Creative Checking - Validation

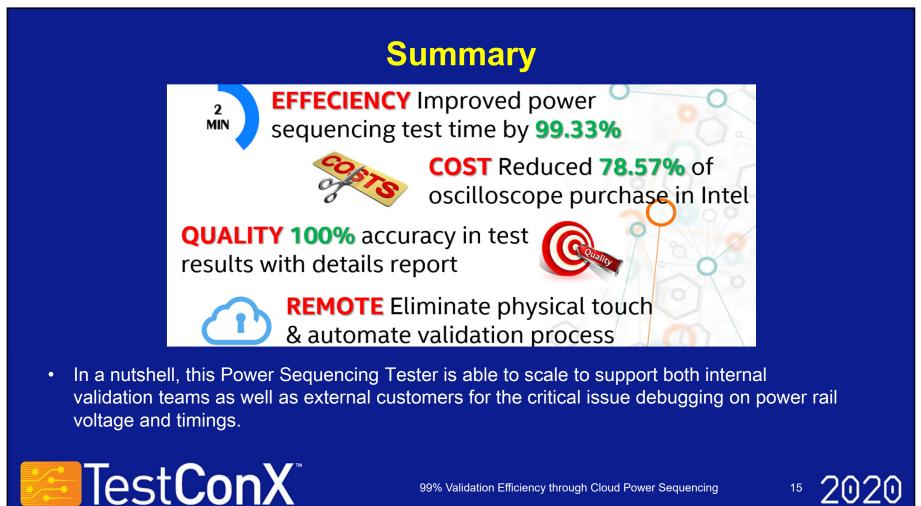

### Impact of Cloud Based Remote Debug

| Components                 | Before                   | After      | Improvements |

|----------------------------|--------------------------|------------|--------------|

| Hardware Cost              | \$140,000                | \$30,000   | 78.57%       |

| Test Time                  | 5 hours/test             | 2 minutes  | 99.33%       |

| Headcount                  | 2 heads                  | 0 heads    | 100.00%      |

| Characterization<br>Method | Manual                   | Systematic | 100.00%      |

| Result Accuracy            | Vary by<br>person/skills | Systematic | 100.00%      |

- Better customer engagement & collaboration: Solution will be offered to Intel's customers as part of features in Cloud Based Remote Debug infrastructure

- Competitive advantage through IP: All SoC (System On Chip) designers performed power sequencing test

**Creative Checking - Validation**

Creative Checking - Validation

#### **Acknowledgements**

- Eric Chan VP in Intel IoTG (Internet of Thing Group)

- Board of Directors in Intel Malaysia Design Center (MDC)

- Ng, Hooi Ching IT Malaysia Hub Manager

- Goh, Kean Hean Engineering Lab Manager

- Ooi, Seong Guan Post-Silicon Technologist & Product Owner

99% Validation Efficiency through Cloud Power Sequencing

TestConX Workshop

www.testconx.org

May 11-13, 2020

Creative Checking - Validation

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2020 TestConX Virtual Event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2020 TestConX Virtual Event. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

#### www.testconx.org

TestConX Workshop