Session 6 Presentation 2

## TestConX 2020

Creative Checking - Validation

# New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements

### KRISHNA MOHAN CHAVALI, JOSHUA DRAGULA GLOBALFOUNDRIES

Virtual Event • May 11-13, 2020

TestConX Workshop

www.testconx.org

May 11-13, 2020

Session 6 Presentation 2

Creative Checking - Validation

#### Acronyms

- SER Soft Error Rate

- SEU Single Event Upset

MFF Million FF's.

- SET Single Event Transient

- ASER Alpha Soft Error Rate

- TNSER Thermal Neutron SER

- HEN High Energy Neutron

- pSER Proton SER

- FF Flip Flop

- FITs Failures in Time

- STS A: Chip with Standard FF's

- STS\_B: Chip with Enhanced FF's

- MIL-STD Military Standard

- JESD89 JEDEC SER Standard

New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements 3

Creative Checking - Validation

## Abstract

- Off-shelf testers will not survive the accelerated harsh radiation environment.

- Custom designed new tester need to go through proper qualification procedure to ensure before releasing for regular SER testing.

- How a new package level tester was qualified with high energy proton beam SER stress testing, to qualify and to release.

- Proper correlation of new tester in beam test environment is planned.

- An existing old qualified tester was used as reference standard to compare.

- Both went through the proton high energy beam testing and data collection.

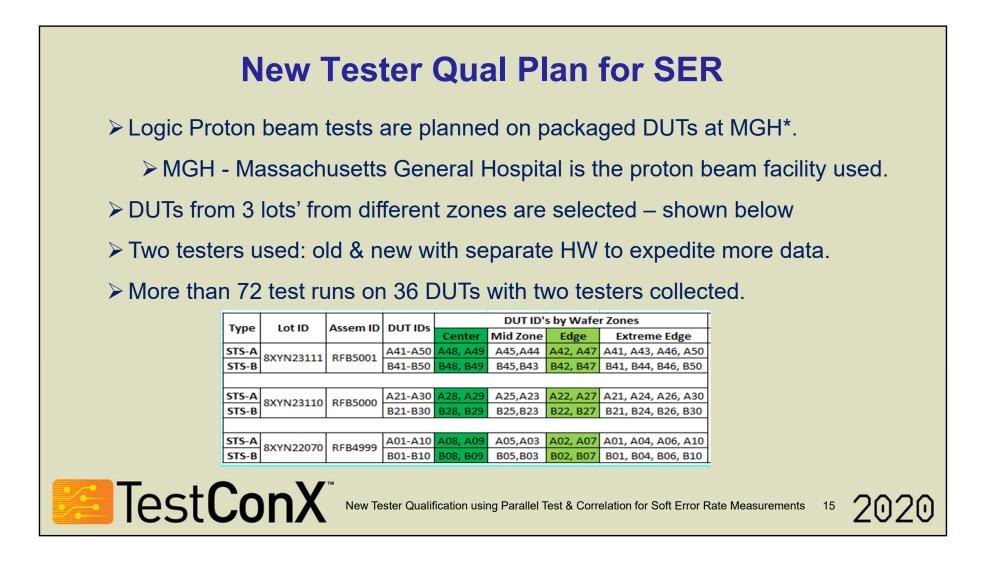

- Logic test chips from FinFETs bulk process were used by both testers.

- Testers run in parallel, through the beam environment, for data collection along with the correlation data results, presented.

| Factors that Impact SER                                                                                                         |                                  |                                    |

|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------------|

|                                                                                                                                 | Process:                         | Bumping/Assembly/Material:         |

|                                                                                                                                 | ➢ Bulk or SOI.                   | ➤ Wafer Bumping:                   |

|                                                                                                                                 | Doping concentration & profile   | SnAg or Copper Pillar              |

|                                                                                                                                 | in substrate and wells.          | Assembly material & coating        |

|                                                                                                                                 | Junction: Voltage & capacitance. | Lead frame & Die attach            |

|                                                                                                                                 | Materials & Passivation:         | Molding Compounds:                 |

|                                                                                                                                 | BPSG, SiN or Polyimide           | Synthetic, plastic, ceramic        |

|                                                                                                                                 | Design & Device:                 | Application:                       |

|                                                                                                                                 | Bit Cell Size                    | Radiation Level                    |

|                                                                                                                                 | Redundancy                       | Altitude & Latitude                |

|                                                                                                                                 | Error Correction Code (ECC)      | Consumer, Industrial               |

|                                                                                                                                 | Refresh Rate.                    | Avionics, Space (Mission Critical) |

| <b>TestConX</b> <sup>™</sup> New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements 6 2020 |                                  |                                    |

TestConX Workshop

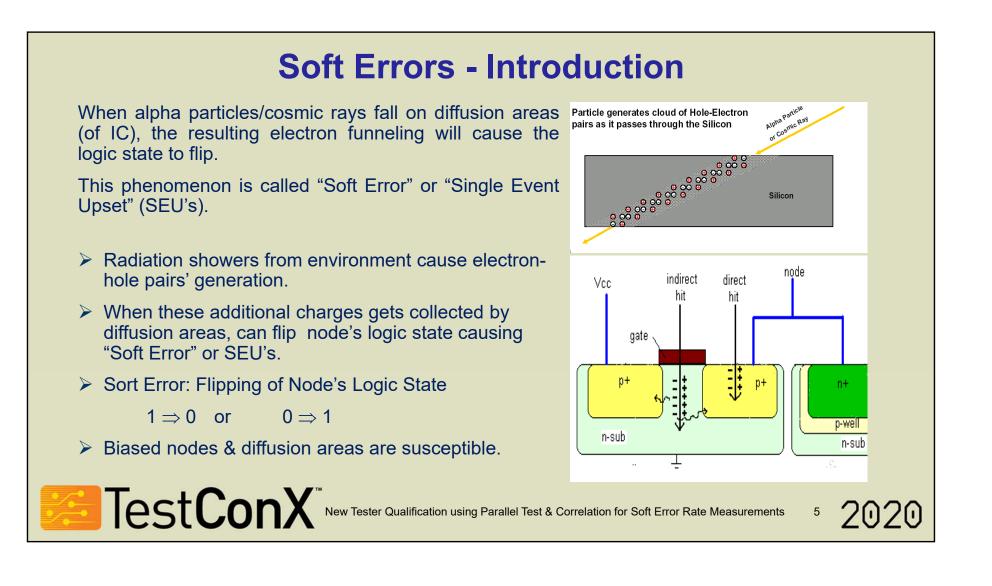

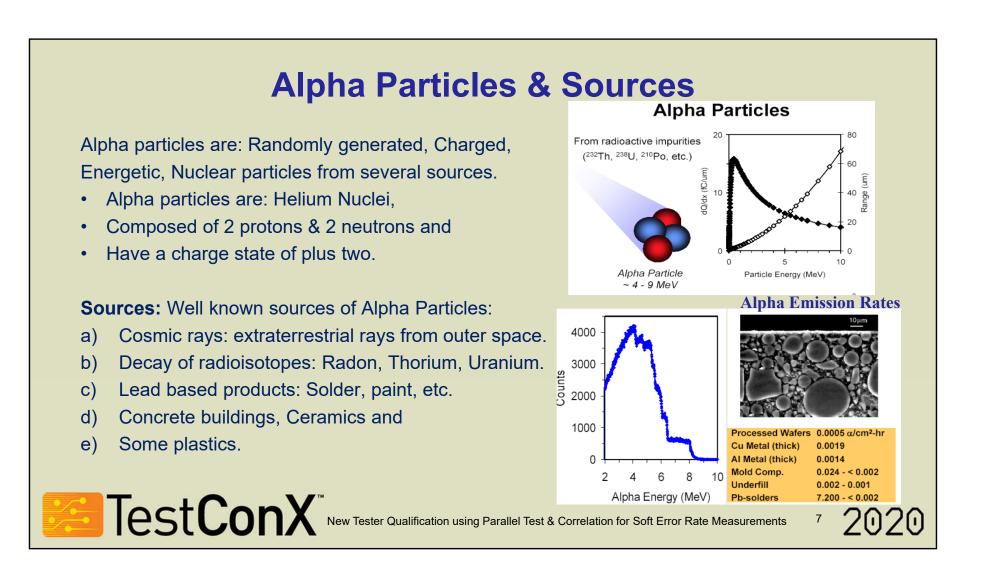

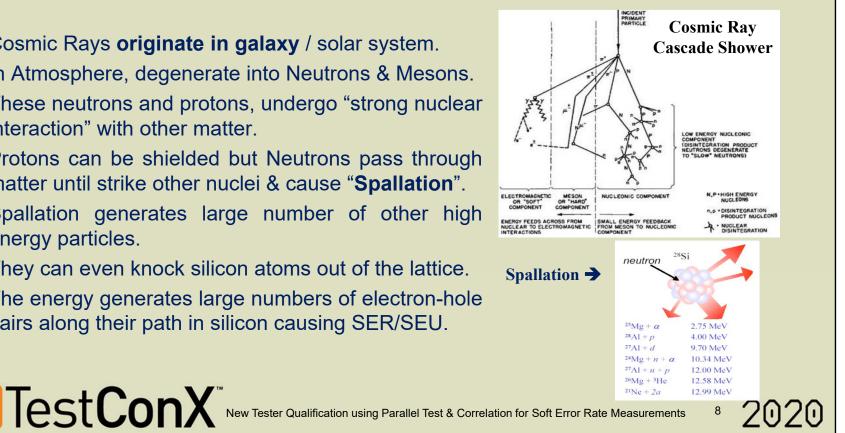

#### **Cosmic Rays & Spallation**

- Cosmic Rays originate in galaxy / solar system.

- In Atmosphere, degenerate into Neutrons & Mesons.

- These neutrons and protons, undergo "strong nuclear interaction" with other matter.

- Protons can be shielded but Neutrons pass through matter until strike other nuclei & cause "Spallation".

- Spallation generates large number of other high energy particles.

- They can even knock silicon atoms out of the lattice.

- The energy generates large numbers of electron-hole pairs along their path in silicon causing SER/SEU.

Creative Checking - Validation

## **SER Qual Requirements**

- Soft Error Radiation (SER) tests are part of Tech. node Quals.

- SER Qualification and test methodology based on JESD-89.

- SER Qual is done using either SRAM or Logic test chips/vehicles.

- SER Qual Tests, generally, done in three radiation environments.

- Alpha SER, Thermal Neutron SER and High Energy Neutron Beam SER.

- Alpha: @0-5MeV; Thermal Neutron: @5-50MeV; HE Neutron:@50-500MeV (1GeV).

- Commercial/off-shelf testers end up failing or give wrong results.

- Due to the radiation interacting with test hardware, might produce wrong data.

- Custom designed testers to withstand harsh radiation environment.

## SER – Test Standard

This test measures the failure rates: FITs/hr/MFF or FITs/hr/Mb Under different accelerated radiation environments: Alpha, Thermal Neutron & High Energy Neutron etc.,

- JEDEC Standard No: JESD-89

- Test Patterns

- Military Standard No: MIL-STD-883E, Method 1032.1

- Radiation Source : Alpha, T. Neutron, HE Neutron

- Voltages Used : Vnom-10%, Vnom, Vnom+10%

- Stress Modes : Static and Dynamic

- INV/CHBD, S0, S1, S0-1, S1-0. 1

TestconX<sup>®</sup> New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements

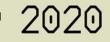

### Need for 2<sup>nd</sup> Tester Qual

- Existing tester was 20years old, though working need backup

- $\rightarrow$  If it fails need 1year to redesign Tech. node quals impact.

- Beam time is costly: @1000~1200 USD/hr, @30K for beam/qual alone.

- > By having 2 testers and parallel testing 2xDUTs can be tested.

- > New tester completed assembly, integration & prelim tests after 3years.

- Planned to use next Qual beam testing to use both testers in parallel.

- Existing tester was used as standard for reference data to compare.

- Data from both testers, running simultaneously can be correlated using:

- > Running both testers in parallel for each run, same duration, swapping DUTs etc.,

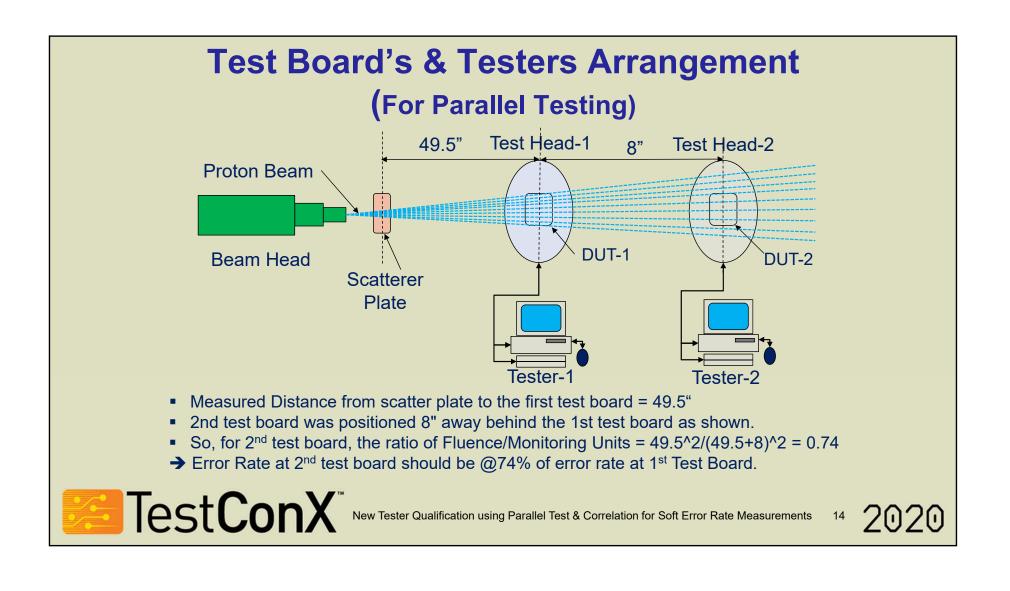

- Distance & position of DUT from beam were off-set by the Geometry Factor.

Session 6 Presentation 2

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

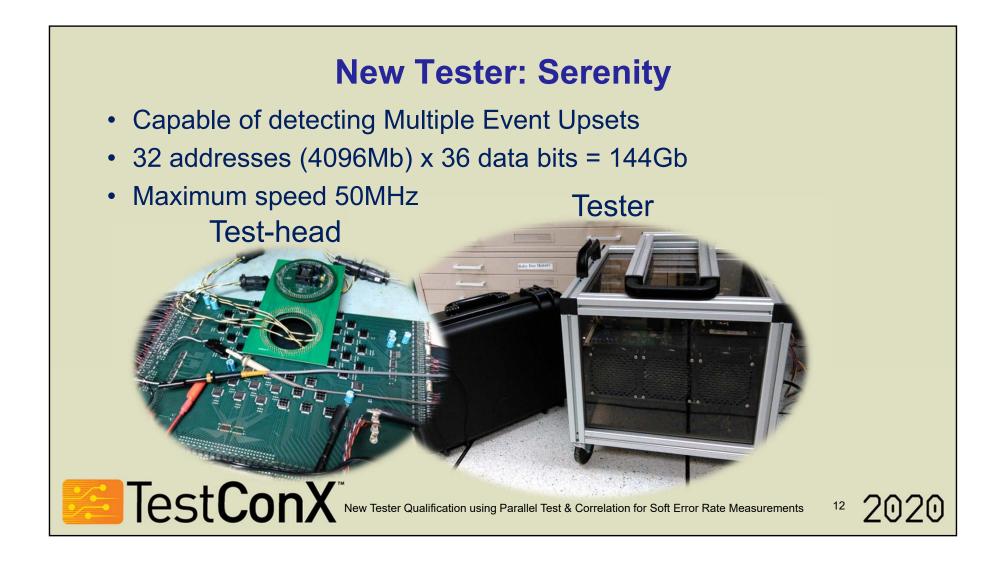

#### Soft Error Rate Testing Room

• The Test heads (1 &2), containing the DUT sockets, were placed directly in the proton beam path.

- The Testers 1 & 2 were • placed on the side.

- Testing was performed in • the Experiment room.

Creative Checking - Validation

Creative Checking - Validation

TestConX Workshop

### **Correlation Checks Planed**

The below checks are implemented to correlate data between two testers (1 & 2):

- ✓ Equal number of DUTs tested on both testers from all zones and lots.

- $\checkmark$  Testers were run in parallel for each test run two DUT cards used.

- ✓ 2Pcs of DUT boards were ordered same design & supplier.

- $\checkmark$  Test duration for each test run (beam exposure) is same for both testers.

- ✓ DUTs from one DUT card and tester were swapped to collect data.

- ✓ Run-1: Terster-1, DUT-1 and Tester-2, DUT-2 → Run-2: Tester-1, DUT-2 and Tester-2, DUT-1

- ✓ Both Run-1 and Run-2 are run with same beam <u>fluence</u>\*, voltage, patterns and type.

- ✓ Data on two test chips collected with both testers: Standard & Enhanced FF's.

- ✓ Data on two types of Logic fails collected: SEU's and SET's.

\***Fluence** is radiation flux integrated over duration of exposure.

TestconX<sup>®</sup> New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements

#### **Correlation by DUT's Swap Data** $\checkmark$ DUTs from one DUT card and tester were swapped to collect data. $\checkmark$ The fail rate and FITs data collected by swapping found to be @13% $\checkmark$ For SER tests, given the variations, <20% delta is within limits. Pattern **T1-FITs** MeV Type Voltage **T2-FITs** Delta % Swap 0.72 11.67 14.11 17 A28 on T1 9.40 A29 on T2 150 SEU **S**1 0.80 8.48 10 Test Data 0.88 6.88 7.53 9 0.72 9.87 11.44 14 8.84 7 150 SEU **S**1 0.80 8.22 A29 on T1 A28 on T2 7.12 7.59 0.88 6 now swap 0.72 6.62 7.75 15 on Testers 150 SET **S**1 0.80 4.48 5.38 17 17 0.88 3.44 4.17 Avg. Delta **a**13 % TestconX<sup>®</sup> New Tester Qualification using Parallel Test & Correlation for Soft Error Rate Measurements

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

## **Cost & Cycle Time Savings**

Some of the advantages of using 2 testers in parallel for SER:

- 2x DUTs can be tested for each run Vs using 1 tester.

- Need two DUT boards for parallel testing: 2K Vs 4K USD.

- Considering beam cost & cycle time savings → justified.

- Beam time to book can be halved as 2x DUTs can be tested.

- $\rightarrow$  50% reduction in beam costs can be achieved.

- → This will further reduce trip costs hotel/stay costs by 50%.

- Project/trip Test time can also be reduced:

- 3persons x 3days → 2persons x 2days → @40% reduction.

- Saved time used for data checks & analysis faster Qual.

**Creative Checking - Validation**

## Conclusion

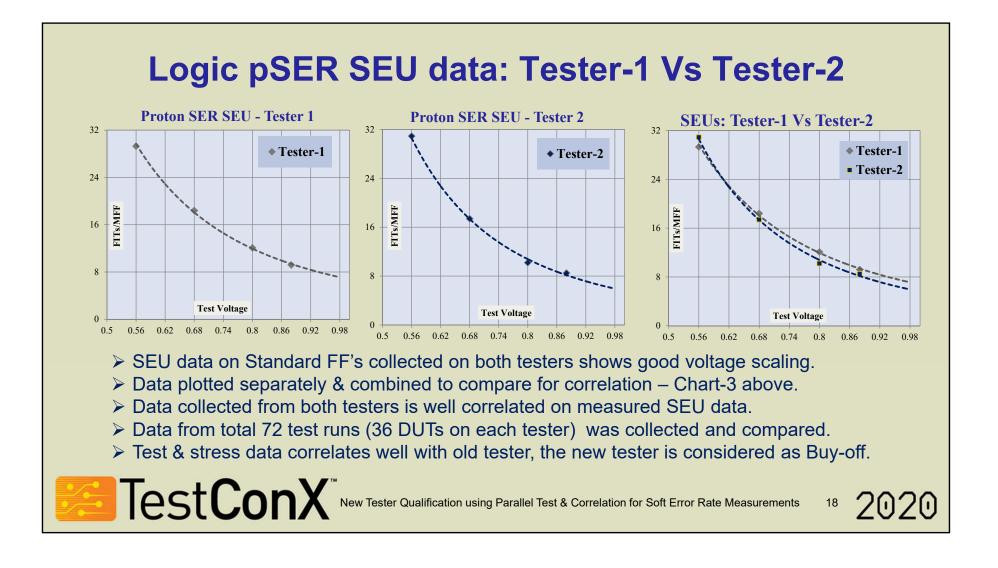

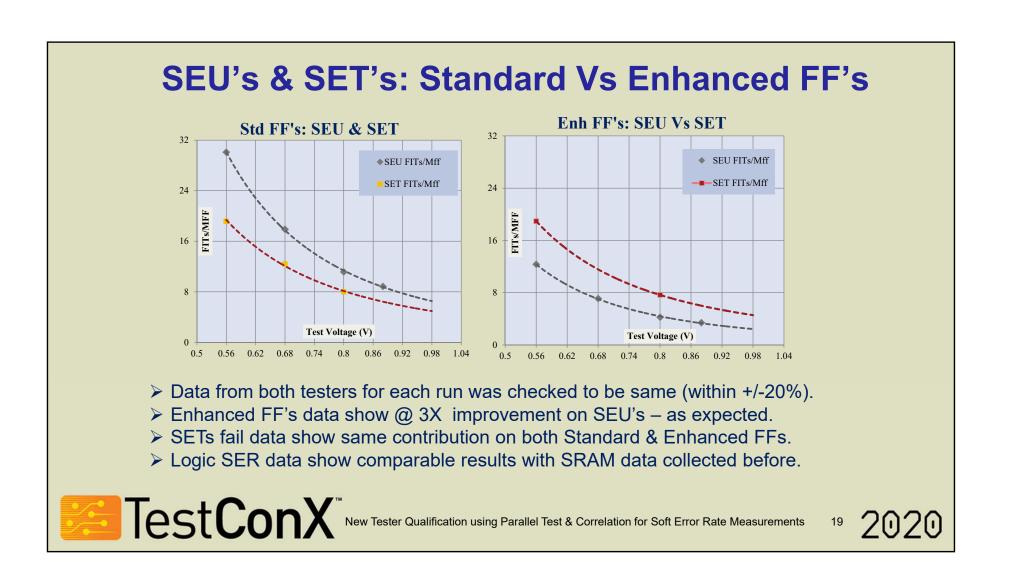

SEU & SET data on 2 test chips collected on both testers: ➤Good voltage scaling observed both old and new testers.  $\triangleright$  Data from total 72 test runs (36 DUTs on each tester) compared.  $\triangleright$ Both testers data for each run was checked to be same: < +/-20%. Enhanced FF's show @ 3X improvement on SEU's – expected. SETs FITs show same contribution on Standard & Enhanced FFs. Data plots from both testers on SEU & SET data – well correlated. Logic SER data show comparable results with SRAM data. New tester's test & stress data correlates well with old tester The new tester is considered Qualified and released.

**Creative Checking - Validation**

#### References

1) JESD89: Measurement and Reporting of Alpha Particle and Terrestrial Cosmic Ray-Induced Soft Errors in Semiconductor Devices by JEDEC.

2) Alpha Particle induced Single-Event Error Rates and Scaling Trends in Commercial SRAM Cells by I. Chatterjee, B. L. Bhuva, S.J. Wen, R. Wong.

3) Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic Premkishore Shivakumar et. all, Proceedings of the 2002 International Conference on Dependable Systems and Networks.

4) SER Scaling and Trends in Planar Submicron Technology Nodes by Krishna Mohan Chavali, EDTM-2017, Tokyo, Japan.

5) Soft Error Rate from Planar to FinFETs and Bulk Vs SOI by Krishna Mohan Chavali, EDTM-2018, Tokyo, Japan.

6) Soft error rate scaling for emerging SOI technology options, by P. Oldiges et al., in Proc. 2002 Symposium VLSI Technology Dig. Tech. Papers, HI, June 11–13, 2002, Tech. Papers, pp. 46–47.

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2020 TestConX Virtual Event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2020 TestConX Virtual Event. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

#### www.testconx.org

TestConX Workshop