Session 6 Presentation 1

Creative Checking - Validation

# Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

#### Xiao-Ming Gao Intel Corporation

TestConX Workshop

www.testconx.org

Creative Checking - Validation

### Agenda

- 7nm SOC validation platform design challenges

- Modular platform architecture

- Power delivery network design strategies

- Validation and measurement

- Summary

TestConX Workshop

Session 6 Presentation 1

Creative Checking - Validation

## 7nm SOC Validation Platform Design Challenges

- Multiple voltage domains

- Ultra low voltages and high current

- Complex power up sequencing (over 40 rails)

- Low voltage AC/DC noise tolerance

- Tight transient response range

TestConX Workshop

Creative Checking - Validation

## **7nm SOC Validation Platform Design Challenges**

#### Silicon Process Scaling

|              | 7nm vs 10nm              |

|--------------|--------------------------|

| Speed        | Faster                   |

| Power        | Less                     |

| Density      | Higher                   |

| Core voltage | ~0.6v (7nm), ~0.7v(10nm) |

Session 6 Presentation 1

Creative Checking - Validation

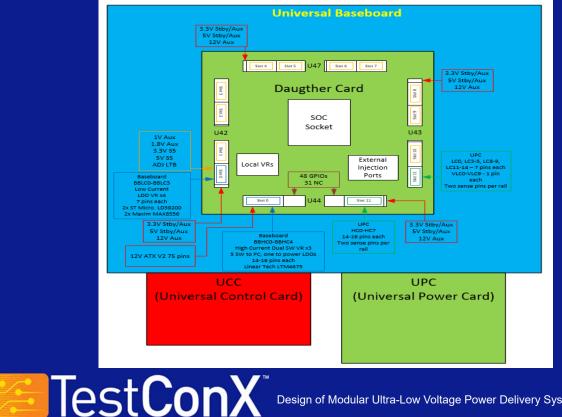

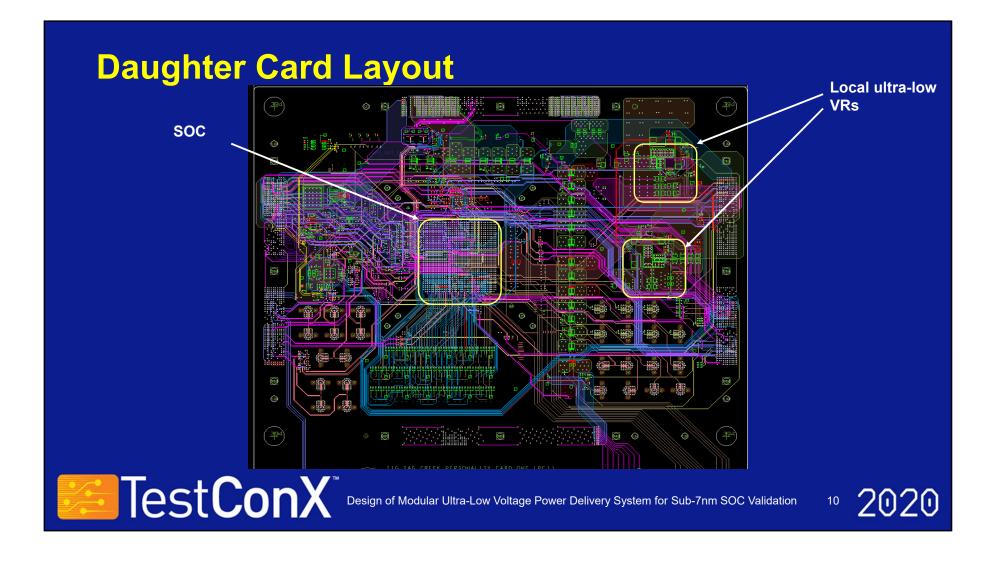

#### **Modular Platform Architecture**

#### **Modules:**

Universal Baseboard (UBB) **Daughter Card (DC)** Universal Control Card (UCC) Universal Power Card (UPC)

Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

Session 6 Presentation 1

Creative Checking - Validation

Creative Checking - Validation

### **Universal Base Board Stack up**

| Objects |                |                      | Thickness 🕨 |       |  |  |

|---------|----------------|----------------------|-------------|-------|--|--|

| #       | Name           | Layer Layer Function |             | Value |  |  |

|         | name           |                      |             | mil   |  |  |

| *       | *              | *                    | *           | •     |  |  |

|         | SOLDERMASK_TOP | Mask                 | Solder Mask | 0.5   |  |  |

| 1       | ТОР            | Conductor            | Conductor   | 1.4   |  |  |

|         |                | Dielectric           | Dielectric  | 3.8   |  |  |

| 2       | L02_GND        | Plane                | Plane       | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4     |  |  |

| 3       | L03_SIG        | Conductor            | Conductor   | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4.1   |  |  |

| 4       | L04_GND        | Plane                | Plane       | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4     |  |  |

| 5       | L05_SIG        | Conductor            | Conductor   | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4.1   |  |  |

| 6       | L06_GND        | Plane                | Plane       | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4     |  |  |

| 7       | L07_SIG        | Conductor            | Conductor   | 0.6   |  |  |

|         |                | Dielectric           | Dielectric  | 4.1   |  |  |

| 8       | L08_GND        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 4     |  |  |

| 9       | L09_PWR        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 4.1   |  |  |

| 10      | L10_GND        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 3     |  |  |

| 11      | L11_PWR        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 3.3   |  |  |

| 12      | L12_GND        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 2.5   |  |  |

| 13      | L13_PWR        | Plane                | Plane       | 1.2   |  |  |

|         |                | Dielectric           | Dielectric  | 3.3   |  |  |

| Objects |                   |            | Types          | Thickness |  |

|---------|-------------------|------------|----------------|-----------|--|

| #       | Name              | Layer      | Layer Function | Value     |  |

|         |                   |            | ,              | mil       |  |

|         | *                 | *          | *              | *         |  |

| 14      | L14_PWR           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 2.5       |  |

| 15      | L15_GND           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 3.3       |  |

| 16      | L16_PWR           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 3         |  |

| 17      | L17_GND           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 4.1       |  |

| 18      | L18_PWR           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 4         |  |

| 19      | L19_GND           | Plane      | Plane          | 1.2       |  |

|         |                   | Dielectric | Dielectric     | 4.1       |  |

| 20      | L20 SIG           | Conductor  | Conductor      | 0.6       |  |

|         |                   | Dielectric | Dielectric     | 4         |  |

| 21      | L21 GND           | Plane      | Plane          | 0.6       |  |

|         |                   | Dielectric | Dielectric     | 4.1       |  |

| 22      | L22 SIG           | Conductor  | Conductor      | 0.6       |  |

|         | _                 | Dielectric | Dielectric     | 4         |  |

| 23      | L23_GND           | Plane      | Plane          | 0.6       |  |

|         |                   | Dielectric | Dielectric     | 4.1       |  |

| 24      | L24_SIG           | Conductor  | Conductor      | 0.6       |  |

|         |                   | Dielectric | Dielectric     | 4         |  |

| 25      | L25 GND           | Plane      | Plane          | 0.6       |  |

|         |                   | Dielectric | Dielectric     | 3.8       |  |

| 26      | BOTTOM            | Conductor  | Conductor      | 1.4       |  |

|         | SOLDERMASK BOTTOM | Mask       | Solder Mask    | 0.5       |  |

**Power layers:** <u>L9, L11, L13,</u> L14, L16, L18

#### **Ground layers:**

L2, L4, L6, L8, L10 L12, L15, L17, L19 L21,L23, L25

Signal layers: L3, L5, L7, L20, L22, L24

Session 6 Presentation 1

Creative Checking - Validation

TestConX Workshop

Session 6 Presentation 1

Creative Checking - Validation

### **Daughter Card Stack up**

| Objects Types |                | Thickness 🕨          |                | Objects | Objects Types |                   | Thickness  |                |         |

|---------------|----------------|----------------------|----------------|---------|---------------|-------------------|------------|----------------|---------|

| #             | Name           | Layer                | Layer Function | Value   | #             | Name              | Layer      | Layer Function | Value   |

| 1             | Name           | Layer Layer runction | Layer Function | mm      |               |                   |            |                | mm      |

|               |                |                      |                |         | •             | •                 | •          |                |         |

|               |                |                      | <u></u>        |         |               |                   | Dielectric | Dielectric     | 0.08382 |

| <u></u>       |                | Surface              |                |         | 14            | L14_PWR           | Plane      | Plane          | 0.03048 |

| ~~~~          | SOLDERMASK_TOP | Mask                 | Solder Mask    | 0.0127  |               |                   | Dielectric | Dielectric     | 0.0635  |

| <u>_1</u> _   | ТОР            | Conductor            | Conductor      | 0.03556 | 15            | L15_GND           | Plane      | Plane          | 0.03048 |

|               |                | Dielectric           | Dielectric     | 0.09652 |               |                   | Dielectric | Dielectric     | 0.08382 |

| 2             | L02_GND        | Plane                | Plane          | 0.01524 | 16            | L16_PWR           | Plane      | Plane          | 0.03048 |

|               |                | Dielectric           | Dielectric     | 0.1016  |               |                   | Dielectric | Dielectric     | 0.0762  |

| 3             | L03_SIG        | Conductor            | Conductor      | 0.01524 | 17            | L17_GND           | Plane      | Plane          | 0.03048 |

| ****          |                | Dielectric           | Dielectric     | 0.10414 |               |                   | Dielectric | Dielectric     | 0.10414 |

| 4             | L04_GND        | Plane                | Plane          | 0.01524 | 18            | L18_PWR           | Plane      | Plane          | 0.03048 |

| <u></u>       |                | Dielectric           | Dielectric     | 0.1016  |               |                   | Dielectric | Dielectric     | 0.1016  |

| 5             | L05_SIG        | Conductor            | Conductor      | 0.01524 | 19            | L19_GND           | Plane      | Plane          | 0.03048 |

|               |                | Dielectric           | Dielectric     | 0.10414 |               |                   | Dielectric | Dielectric     | 0.10414 |

| 6             | L06_GND        | Plane                | Plane          | 0.01524 | 20            | L20_SIG           | Conductor  | Conductor      | 0.01524 |

|               |                | Dielectric           | Dielectric     | 0.1016  |               |                   | Dielectric | Dielectric     | 0.1016  |

| 7             | L07_SIG        | Conductor            | Conductor      | 0.01524 | 21            | L21_GND           | Plane      | Plane          | 0.01524 |

|               |                | Dielectric           | Dielectric     | 0.10414 |               |                   | Dielectric | Dielectric     | 0.10414 |

| 8             | L08_GND        | Plane                | Plane          | 0.03048 | 22            | L22_SIG           | Conductor  | Conductor      | 0.01524 |

| ****          |                | Dielectric           | Dielectric     | 0.1016  |               |                   | Dielectric | Dielectric     | 0.1016  |

| 9             | L09_PWR        | Plane                | Plane          | 0.03048 | 23            | L23_GND           | Plane      | Plane          | 0.01524 |

|               |                | Dielectric           | Dielectric     | 0.10414 |               |                   | Dielectric | Dielectric     | 0.10414 |

| 10            | L10_GND        | Plane                | Plane          | 0.03048 | 24            | L24_SIG           | Conductor  | Conductor      | 0.01524 |

|               |                | Dielectric           | Dielectric     | 0.0762  |               |                   | Dielectric | Dielectric     | 0.1016  |

| 11            | L11_PWR        | Plane                | Plane          | 0.03048 | 25            | L25_GND           | Plane      | Plane          | 0.01524 |

|               |                | Dielectric           | Dielectric     | 0.08382 |               |                   | Dielectric | Dielectric     | 0.09652 |

| 12            | L12_GND        | Plane                | Plane          | 0.03048 | 26            | BOTTOM            | Conductor  | Conductor      | 0.03556 |

|               |                | Dielectric           | Dielectric     | 0.0635  |               | SOLDERMASK_BOTTOM | Mask       | Solder Mask    | 0.0127  |

| 13            | L13_PWR        | Plane                | Plane          | 0.03048 |               |                   | Surface    |                |         |

#### **Power layers:** L9, L11, L13, L14,L16, L18

#### **Ground layers:** L2, L4, L6, L8, L10 L12, L15, L17, L19 L21,L23, L25

Signal layers: L3, L5, L7, L20, L22, L24

Session 6 Presentation 1

Creative Checking - Validation

TestConX Workshop

Session 6 Presentation 1

Creative Checking - Validation

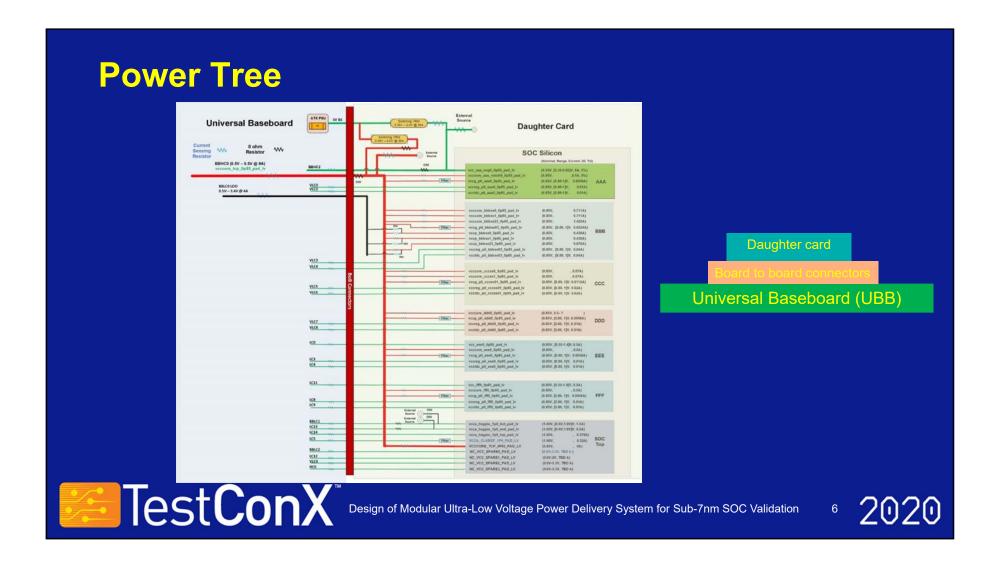

### **Power Delivery Network Design Strategies**

- Power planes partition

- DC and AC Platform performance optimization

- AC noise and load transient minimization

TestConX Workshop

www.testconx.org

Session 6 Presentation 1

Creative Checking - Validation

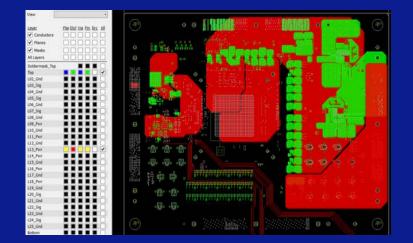

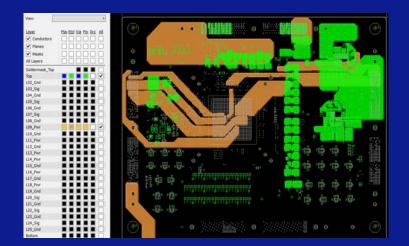

#### **High Current Power Rails Planning**

#### High current power rails use adjacent planes

TestconX<sup>™</sup> Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

TestConX Workshop

www.testconx.org

Session 6 Presentation 1

Creative Checking - Validation

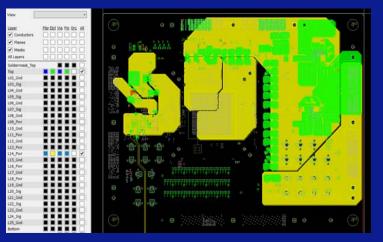

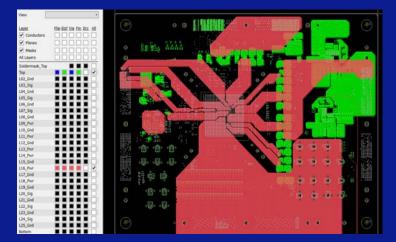

#### Low Current Power Rails Planning

Low current power rails need proper space to avoid interferences

TestConX Workshop

www.testconx.org

Session 6 Presentation 1

Creative Checking - Validation

#### **Low Current Power Rails Planning**

TestConX Workshop

www.testconx.org

Session 6 Presentation 1

Creative Checking - Validation

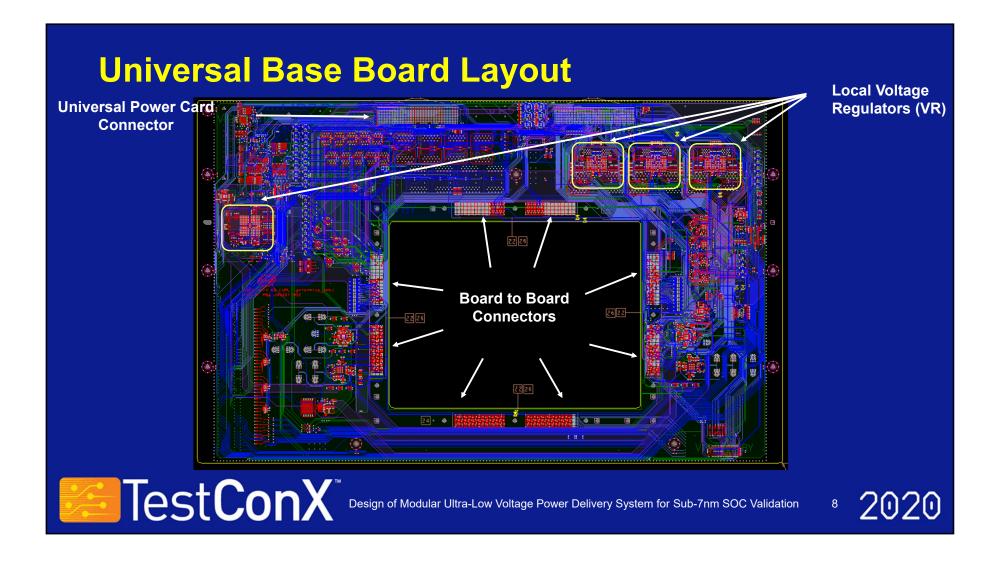

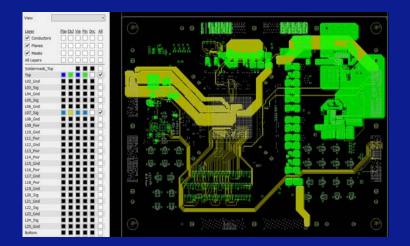

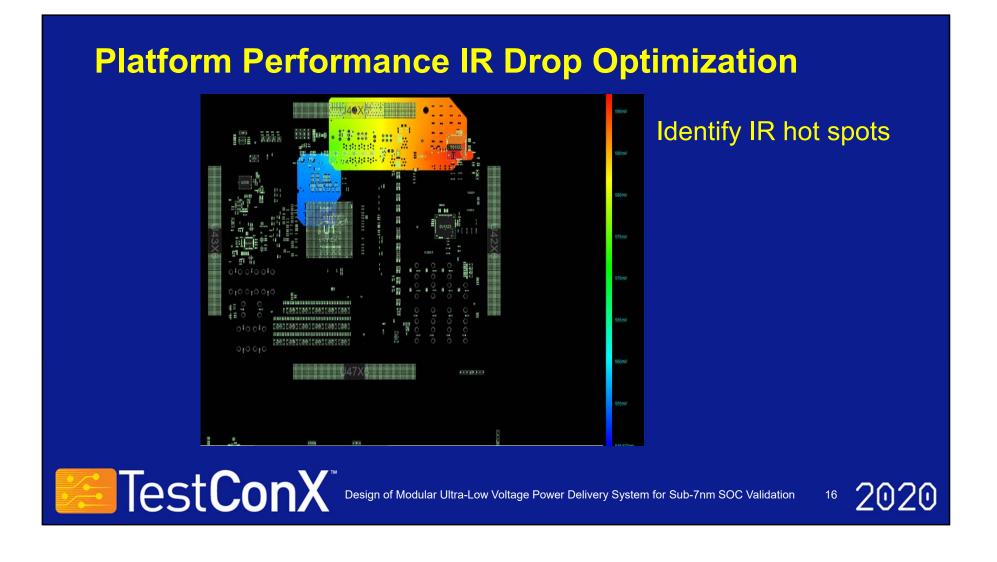

### **Platform Power Performance Optimization**

- Optimal placement of VRs

- Use of PowerDC (Cadence tool) to optimize power shapes

- Reduce power rails IR drop

- Use of PowerSI (Cadence tool) to reduce power rails impedance

- Isolation of power rails to reduce noise

Session 6 Presentation 1

Creative Checking - Validation

TestConX Workshop

Creative Checking - Validation

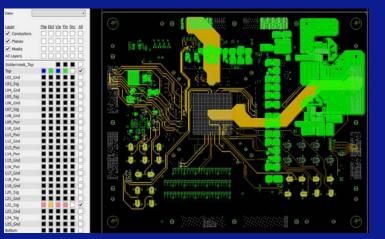

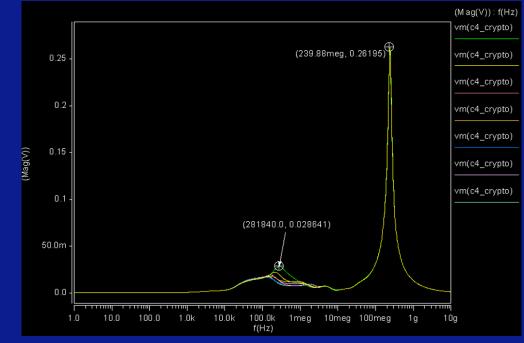

## **Platform Performance Impedance Optimization**

Power rail impedance needs to be minimized

TestconX<sup>™</sup> Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

Session 6 Presentation 1

Creative Checking - Validation

#### Validation and Measurement Set Up

TestConX Workshop

www.testconx.org

Creative Checking - Validation

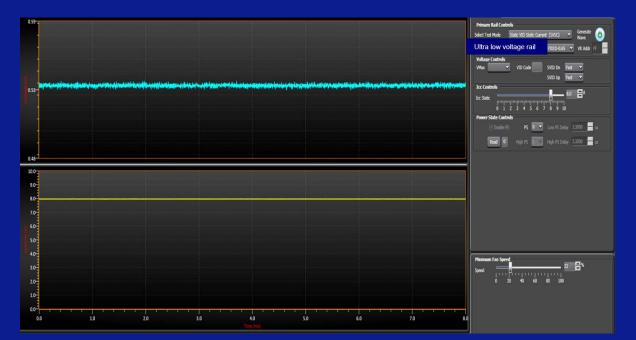

#### Voltage needs to be stable under heavy load

TestconX<sup>™</sup> Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

Creative Checking - Validation

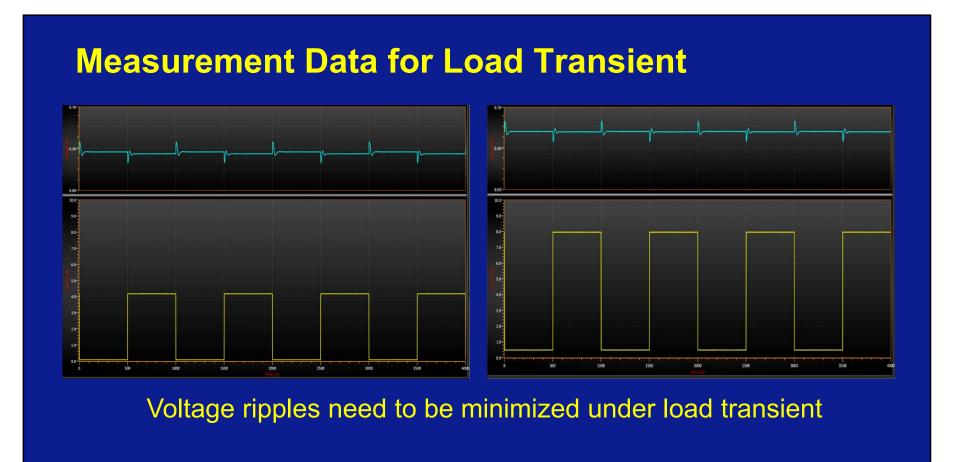

TestconX Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

TestConX Workshop

Session 6 Presentation 1

Creative Checking - Validation

Testconx Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

20Z 21

TestConX Workshop

Session 6 Presentation 1

Creative Checking - Validation

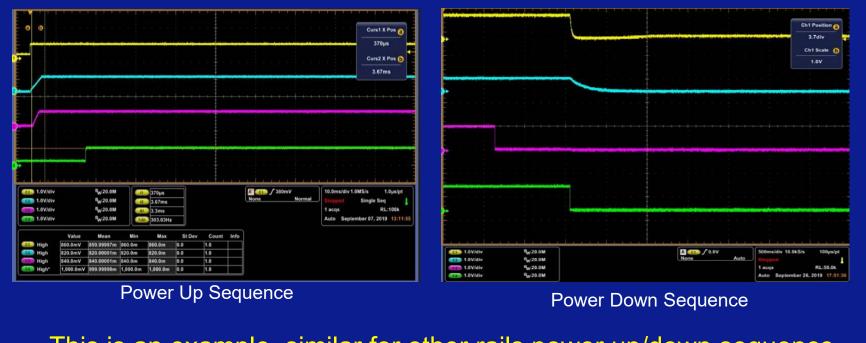

## Power Sequencing Control

This is an example, similar for other rails power up/down sequence

TestconX<sup>™</sup> Design of Modular Ultra-Low Voltage Power Delivery System for Sub-7nm SOC Validation

Creative Checking - Validation

### Summary

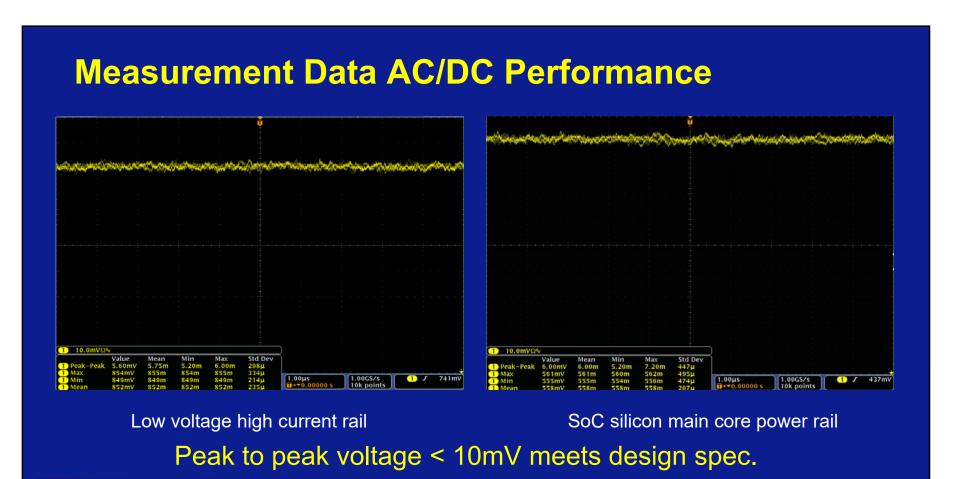

- Optimal power delivery is the key for successful sub-7nm SOC validation

- Multi-domain and ultra low voltage require optimal power planes partition

- IR drop and AC/DC noise should be minimized

- Tight load transient response to guarantee reliable operation

TestConX Workshop

Session 6 Presentation 1

**Creative Checking - Validation**

#### Acknowledgement

The author would like to thank Paul Marciniak, Dan Simon, and Ray Lamoreau for their support. Thanks also go to Rahima Mohammed and Naveid Rahmatullah for the reviews.

TestConX Workshop

Creative Checking - Validation

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2020 TestConX Virtual Event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2020 TestConX Virtual Event. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

#### www.testconx.org

TestConX Workshop