# Power Integrity in Load Boards from the GND Up

Don Thompson R&D Altanova

## What is Power Integrity?

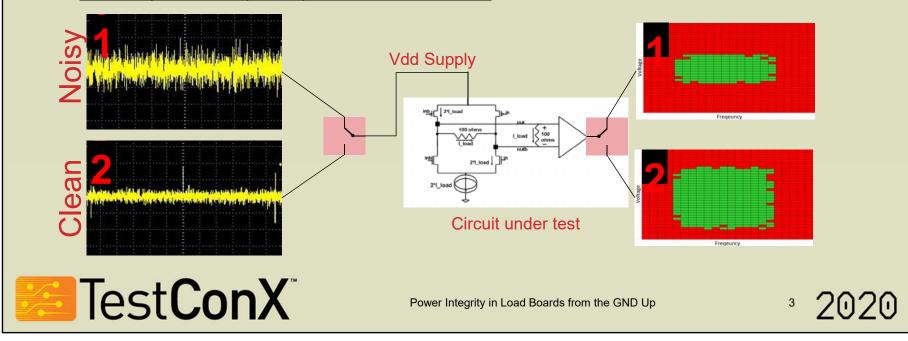

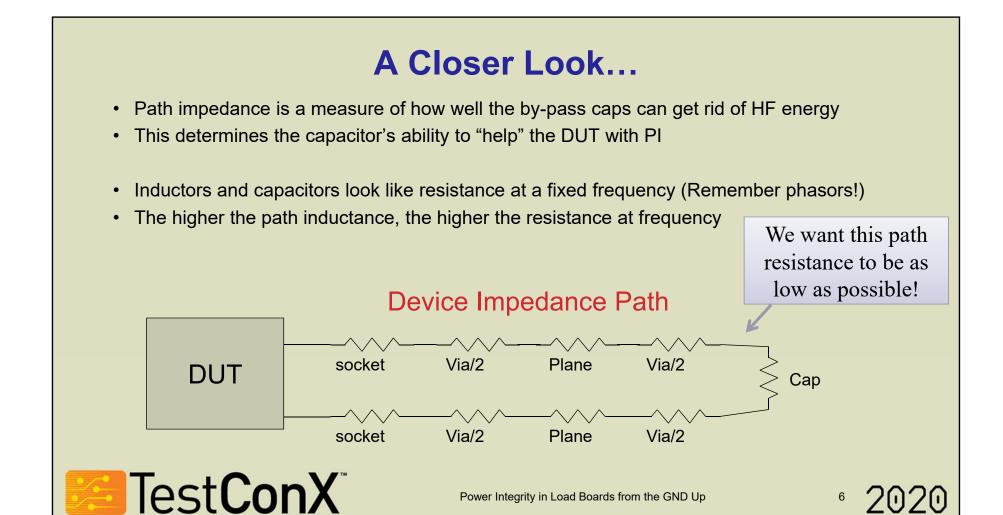

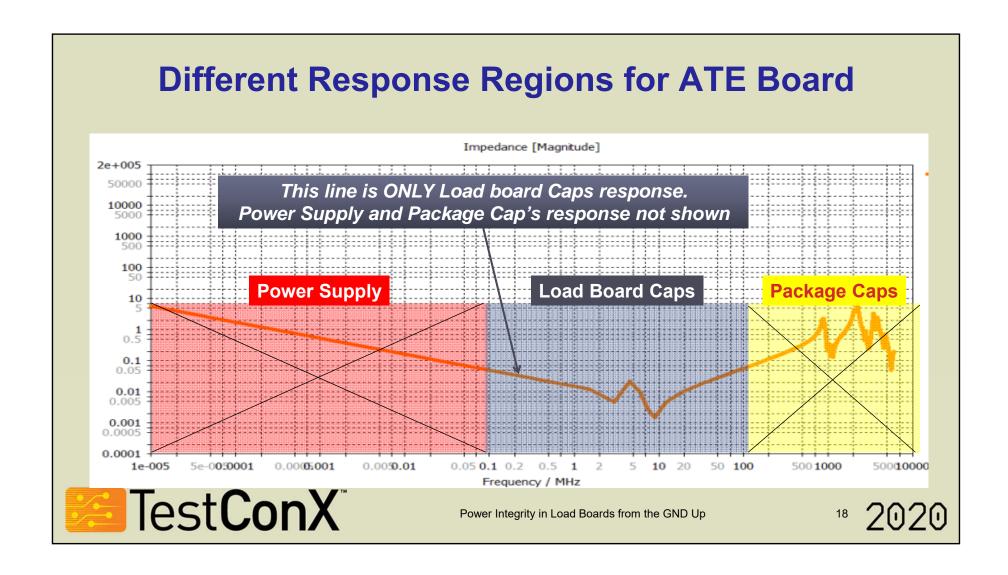

- Power Integrity (PI) is the behavior of your Power Distribution Network (PDN) as it relates to frequency

- Closely related is IR drop analysis, which is the behavior of your device at DC

- IR drop analysis is relatively intuitive and deals with resistance and thermal concerns with in the board. <u>This is not addressed in this paper.</u>

- Power Integrity is typically represented as an Impedance. (That's another way of saying "resistance as it relates to frequency"!)

Power Integrity in Load Boards from the GND Up

2020

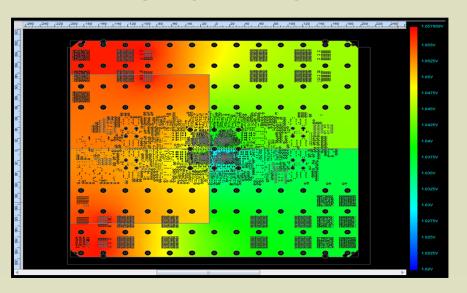

- PI relates to how the power supply ripples under load. (Both Vdd and GND!)

- As your power supply ripples, your ability to test your part will be reduced. Ripple on your supply will lead to a yield hit and you may not even be aware of it!

## Yesterday's Model of PI: Rules of Thumbs

#### To Start:

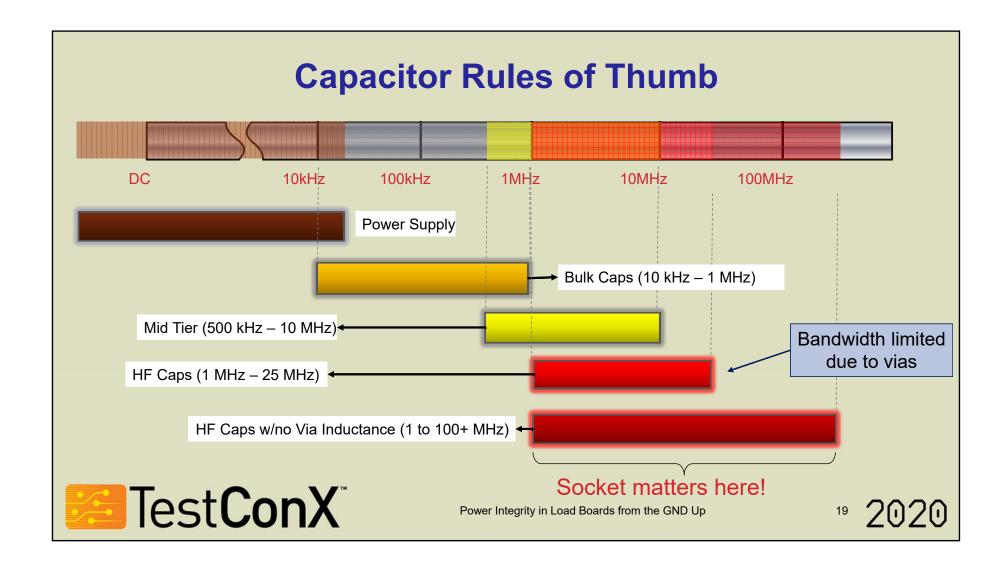

Capacitor scheme comes from device app notes for a <u>soldered down device</u> on a thin board

#### **Apply Rules:**

- Big caps can be placed anywhere on the board, but should be closer to DUT

- Small capacitors must be placed on back side of DUT

- Power and ground planes should be close together

- · Shorter is better

#### And if it fails:

- Add more capacitors!

- Hold meetings and come up with wild guesses at what may be causing the problem!

Power Integrity in Load Boards from the GND Up

2020

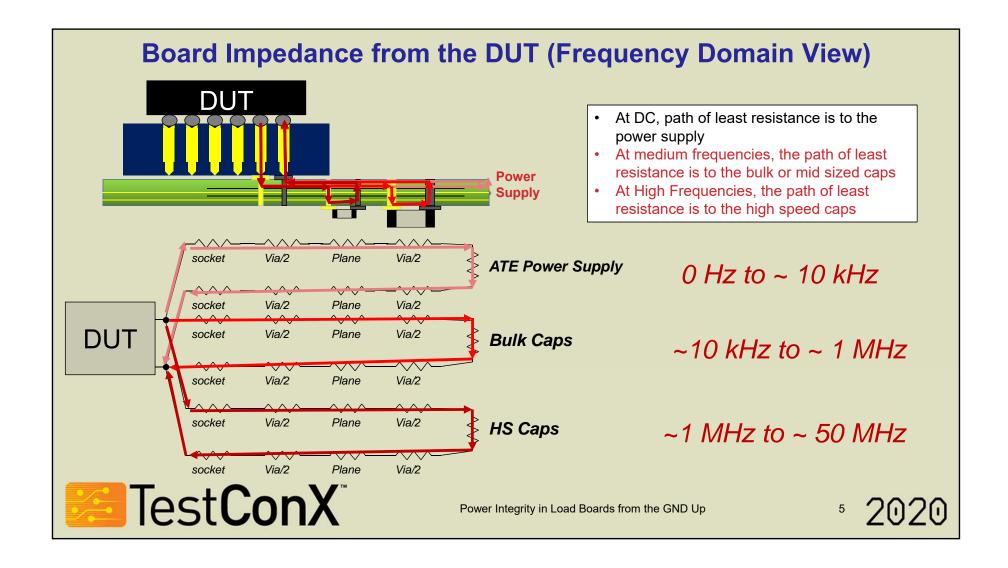

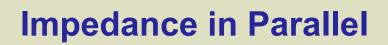

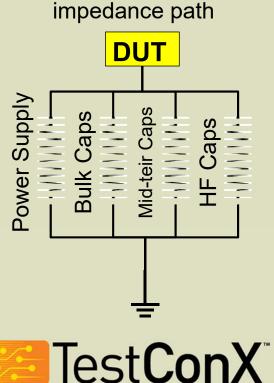

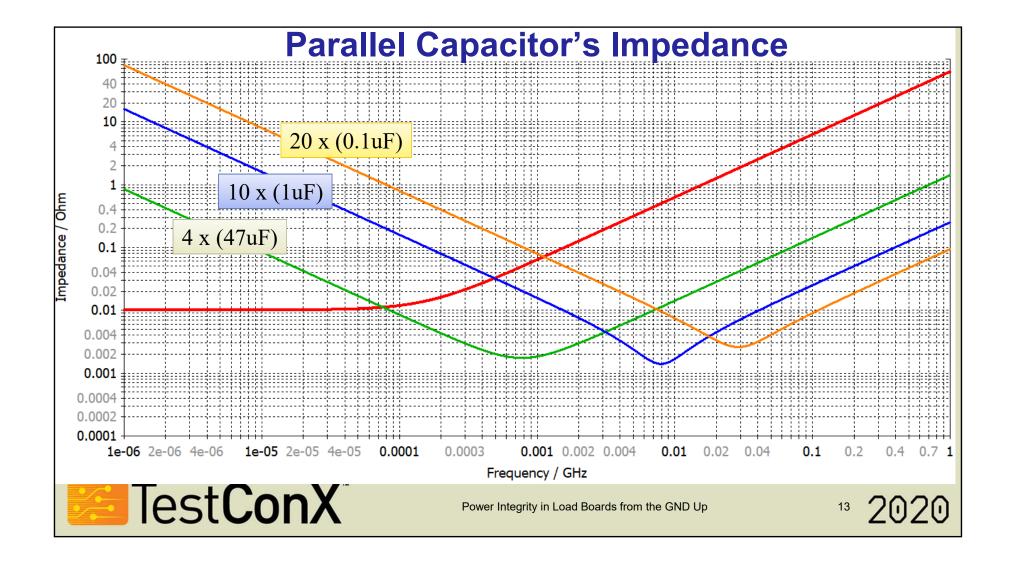

The system will look like resistors in parallel and will find the lowest

At different frequency bands, alternate paths will provide the "path of least resistance"

Power Integrity in Load Boards from the GND Up

\* 2020

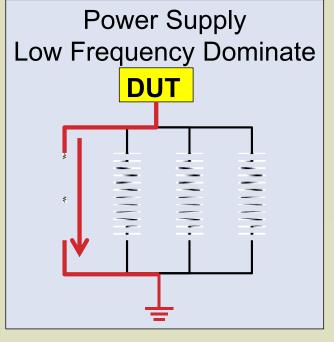

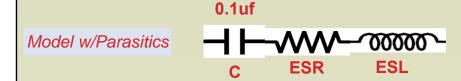

# **Capacitor Modeling**

#### **Modeling Tradeoff Example: MLC Capacitor**

$$Z = \frac{1}{(S)C}$$

or  $\frac{1}{(j\omega)C}$

$$Z = \frac{S^2 + S\left(\frac{R}{L}\right) + \frac{1}{LC}}{\frac{S}{L}}$$

$$Z(j\omega) = j\omega^2 - \frac{j}{LC} + \frac{\omega R}{L}$$

Power Integrity in Load Boards from the GND Up

2020

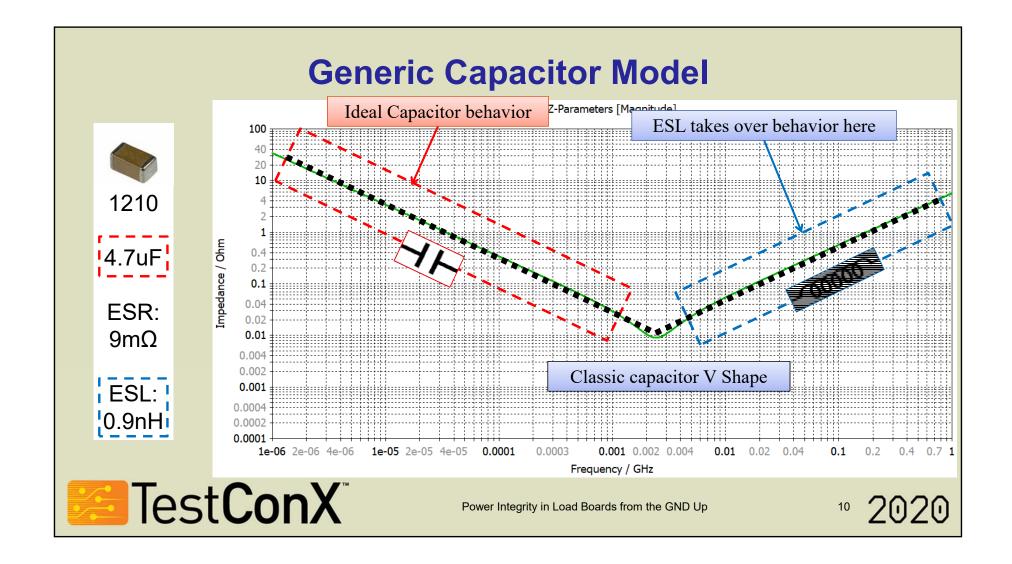

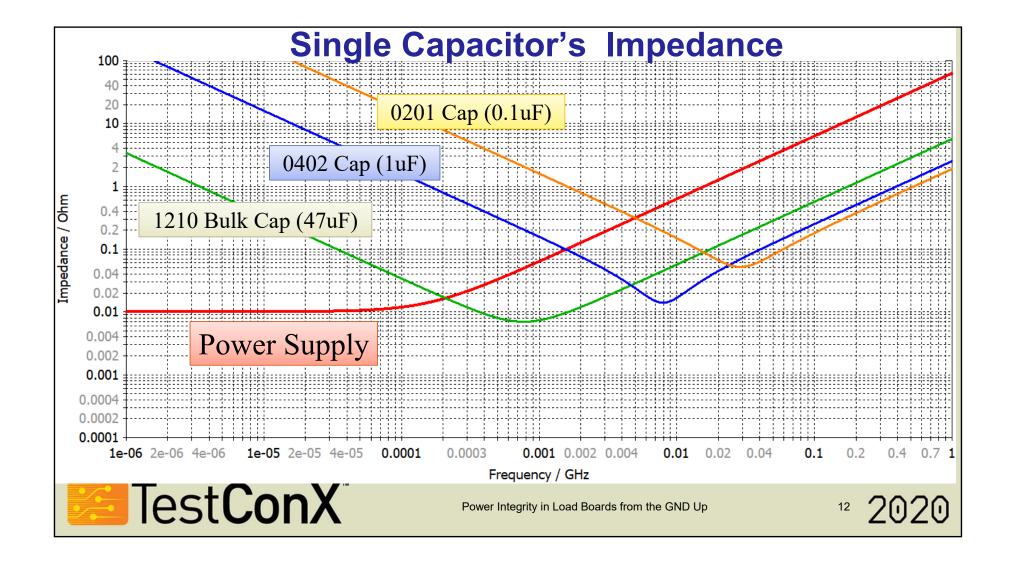

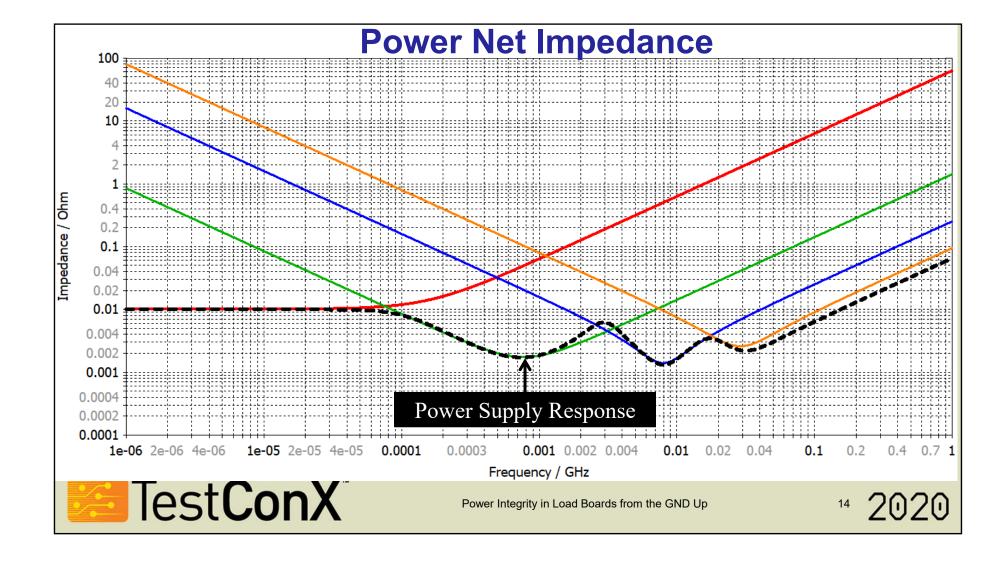

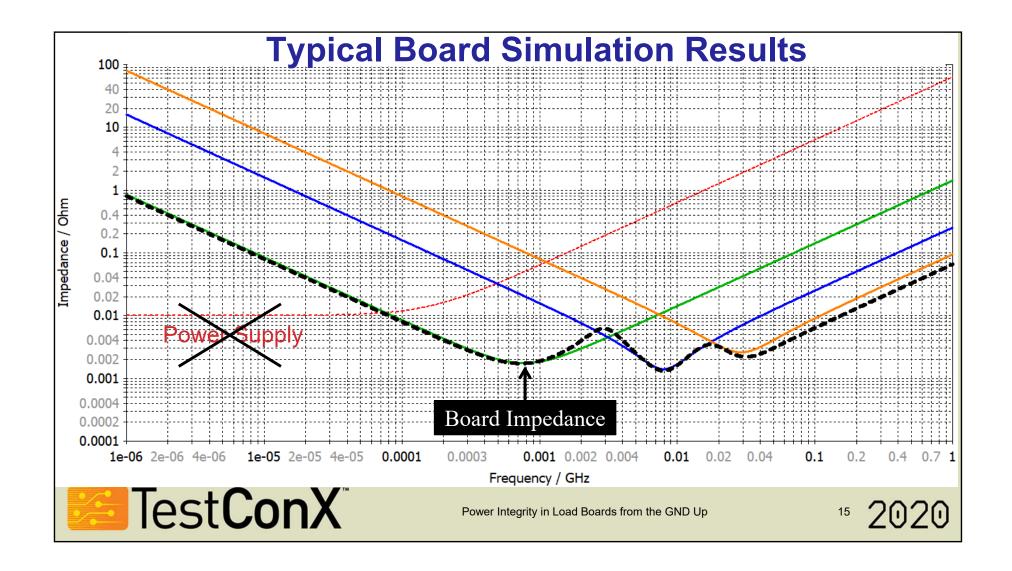

# Impedance Plots in Detail

- Single Capacitor Impedance

- Parallel Capacitor Impedance

- Complete Power Net Impedance

- Typical Board Simulation Results

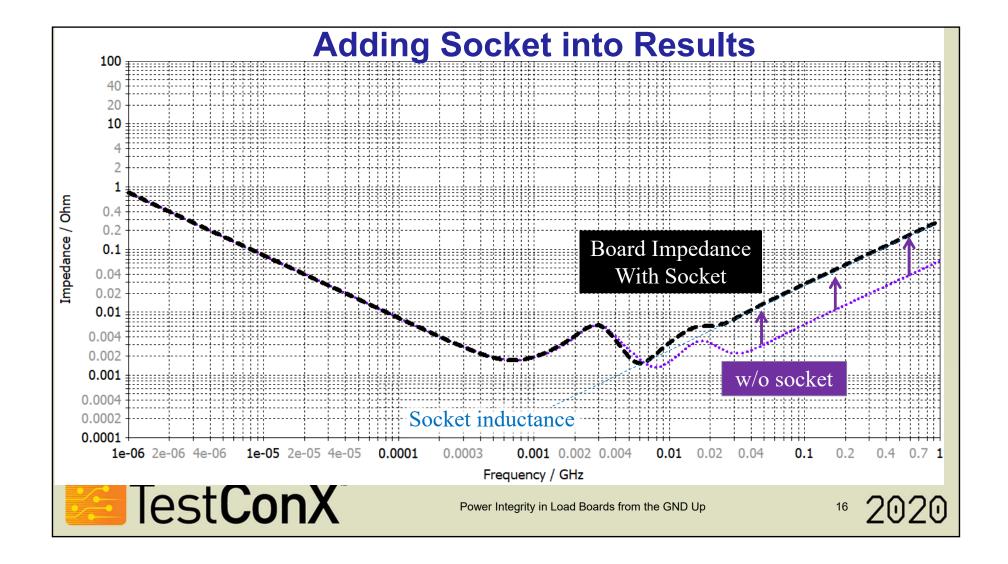

- Including Sockets

We will step through the plots to help understand in detail

Power Integrity in Load Boards from the GND Up

· 2020

## **Load Board Power-Integrity Analysis**

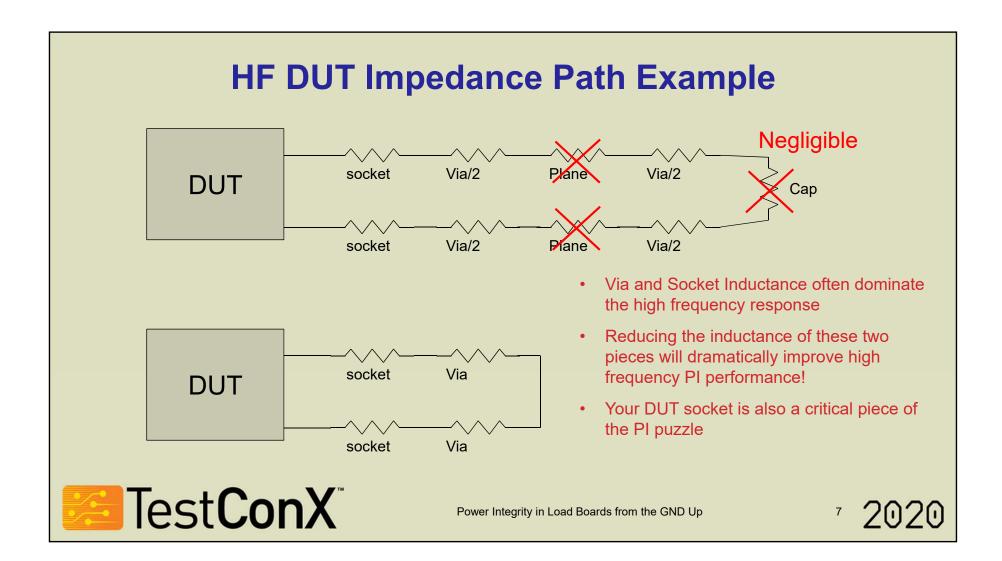

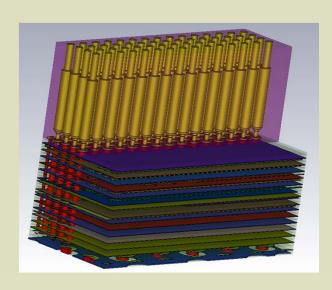

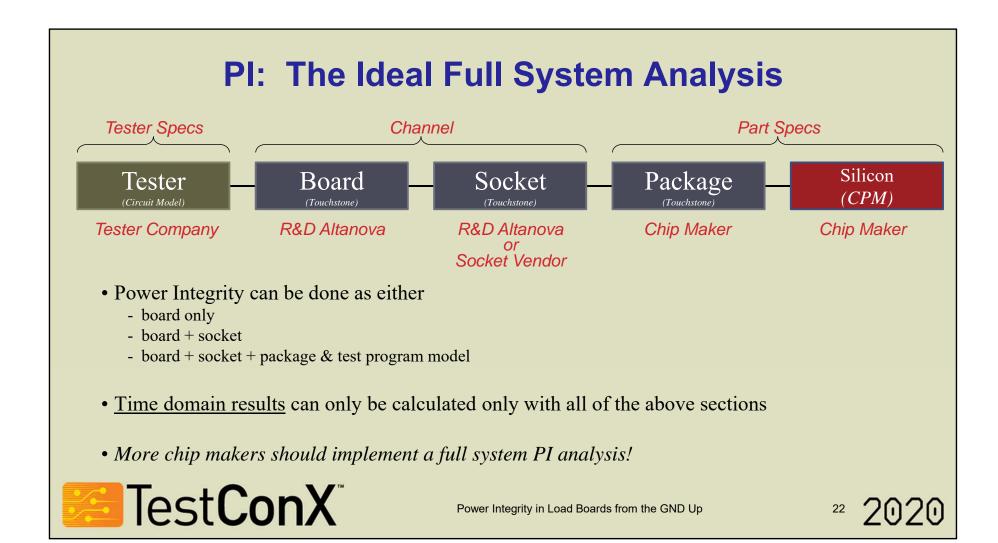

Simulation should take into account all aspects of the board design, including capacitor models, power planes routing, and socket performance 95% of PI modeling in ATE does not include the socket

Power Integrity in Load Boards from the GND Up

20 20 20

## **PI Strategy**

#### **Initial Pre-Layout Simulations**

- Use previous design results and pre-modeled results to estimate performance before layout

- This is very useful for quick "what if" analysis. (What if you add more bulk caps?

What if you add more high speed caps? What if you add EC? Etc.)

- We have seen good correlation between spice and Full Board Simulations

- Simulation time is minutes

#### Final Post-Layout Full Board Simulations

- Import finished design into simulation tool and model entire board PI

- These simulations are full board simulations and include power plane effects

- Socket is not included and if possible should be added after completion

- Simulation time can be 10-20 hours

Power Integrity in Load Boards from the GND Up

<sup>21</sup> 2020

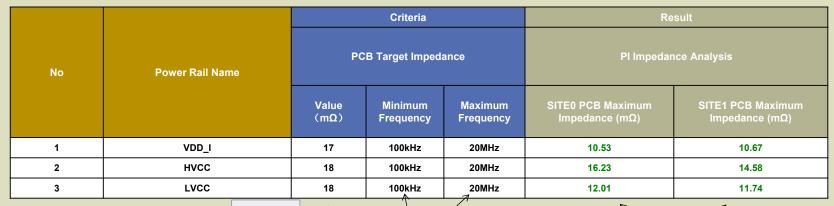

Spec

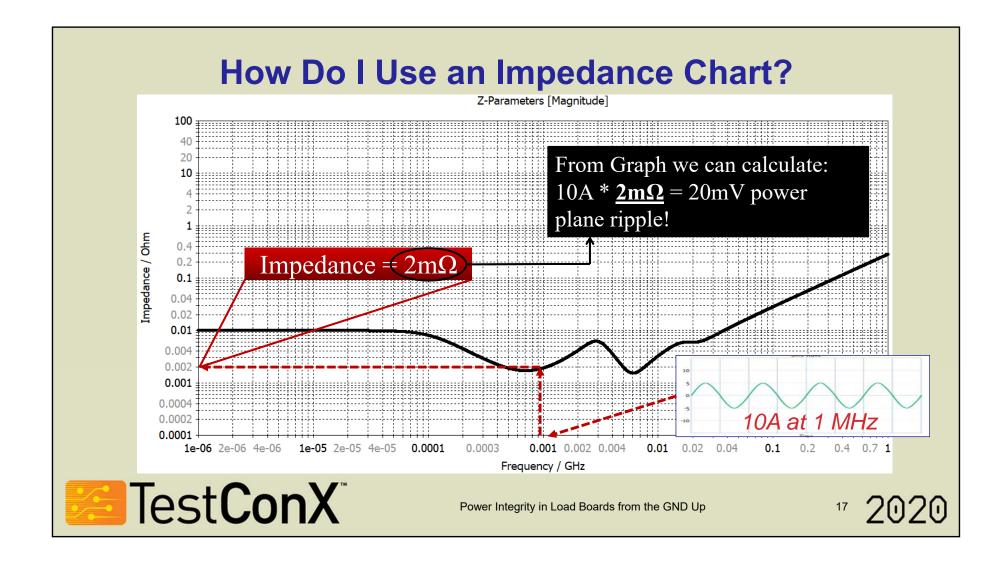

PI is typically listed at specific frequency points to make defining targets easier

Simulation Results

Power Integrity in Load Boards from the GND Up

<sup>23</sup> 2020

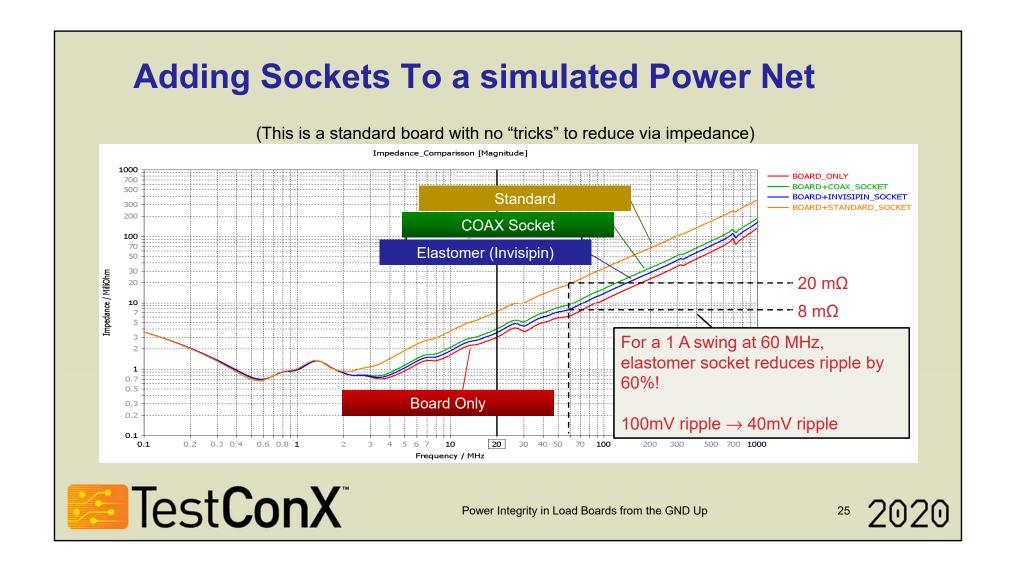

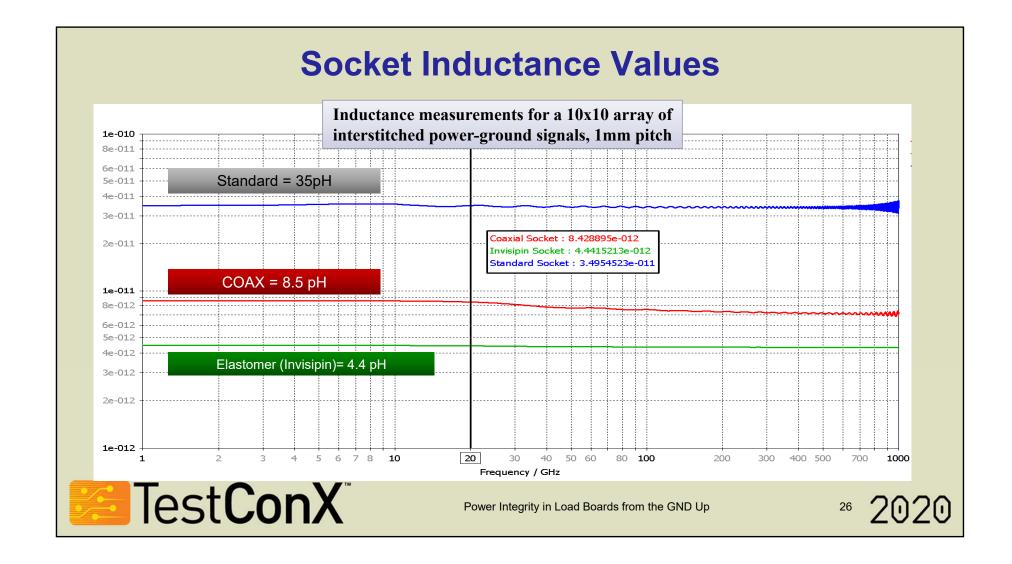

# **Socket Power Integrity**

"Standard"

• The baseline performance

Coax

Power pins specifically designed for low inductance. (This will not be true for all

coax sockets!)

Elastomer

Inductance is proportional to length, so the ultra short height of elastomers makes this solution have very low inductance

Power Integrity in Load Boards from the GND Up

· 2020

### **Conclusion**

- As an industry we need to do better on power integrity and use the tools available

- Impedance plots are valuable and straight forward method of analyzing your power net response

- Sockets are a critical part of the PI of the system

Power Integrity in Load Boards from the GND Up

<sup>7</sup> 2020

#### COPYRIGHT NOTICE

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2020 TestConX Virtual Event. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2020 TestConX Virtual Event. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

www.testconx.org