# Review today's test strategy on ATE and SLT

Liang "Neil" Zhang Teradyne

## Content **□**Device test trend and challenge □High throughput SLT test □Speed up IP debug □Case study on test strategy definition **□**Conclusion Test**ConX**+ Review today's test strategy on ATE and SLT

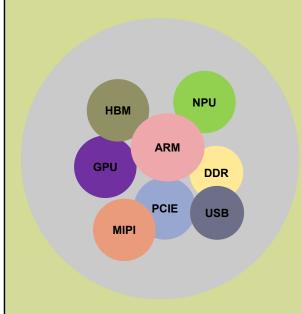

## Device is now much more complex

- More IP integrated (ARM, NPU, GPU, Sensor ..)

- Advance process introduced (10nm -> 7nm -> 7+nm -> 5nm ..)

- Highly integration in package (2.5D -> 3D package)

- High quality requirement and short time to market

Review today's test strategy on ATE and SLT

2019

\_\_\_\_

## **Review Test Strategy for the Device Challenge**

Scenario 1 Scenario 2 Scenario 3 More CP test needed due Wafer to yield concern of Wafer Wafer Test Test advance process **Test** Final More SLT introduced due Test to complex IP integration **Final Test** Final and un-know failure Test SLT Device bring up time **SLT** accelerated from months SLT to weeks Test**ConX**中国 2019 Review today's test strategy on ATE and SLT

## High Throughput SLT Solution is Required

**Teradyne SLT Solution - Titan**

SLT normally take much longer test time than ATE (10 times more!) Traditional SLT handler is limited to 12 or 16 sites

- Supports up to <u>320</u> sites per system

- Supports PoP, PGA, BGA, LGA, etc.

- Test sites are fully asynchronous (load and test)

- System can be serviced while running for ~100%

OEE

High Throughout

Cost Effective

Review today's test strategy on ATE and SLT

2019

Э

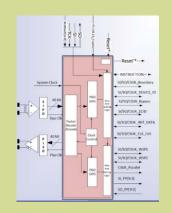

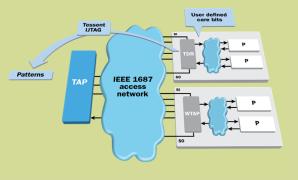

## **Industry Standard Trend**

- ☐ IEEE 1149.10

- Scan test over high speed Interface (like USB)

- ☐ IEEE1687/1500

- Allows IP vendors to offer standardized access to Silicon IP for test

- □ Accellera "Portable Stimulus Group" (IEEE 1800.2-2017)

- system-level design, modeling, and verification standards

Source: IEEE High Speed JTAG P1149.10 Working Group

Review today's test strategy on ATE and SLT

2019

6

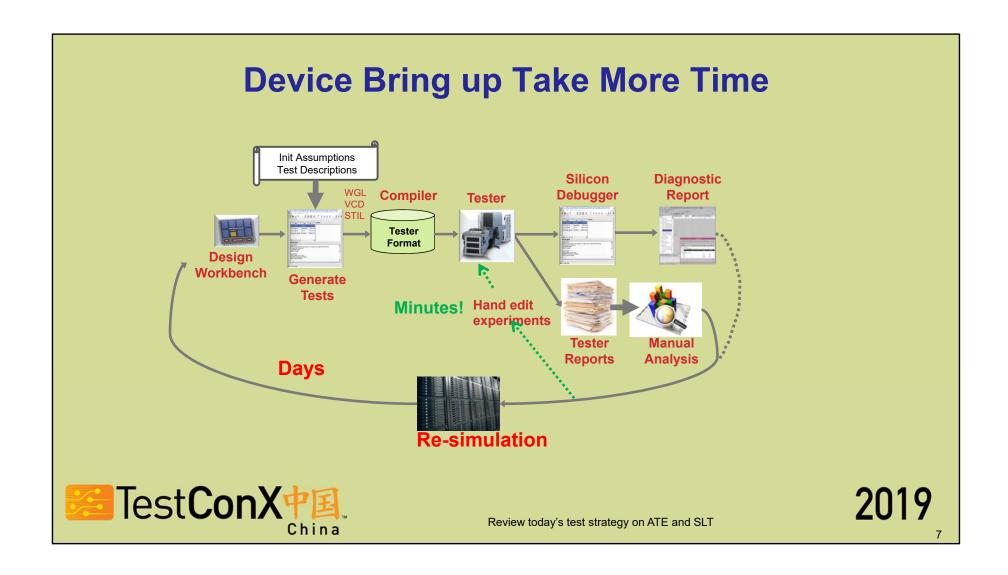

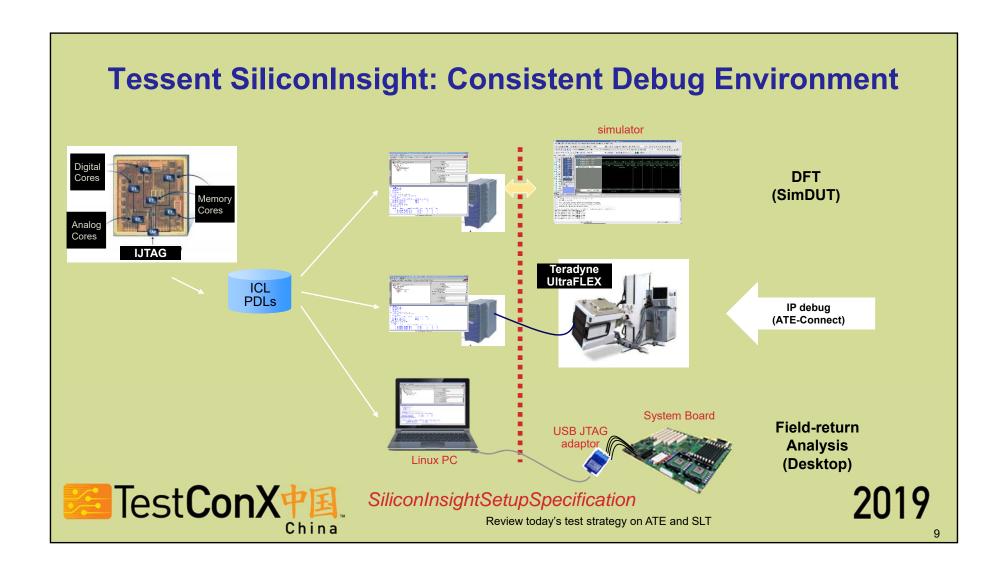

## Teradyne/Mentor Announcement at International Test Conference

Mentor introduces ATE-Connect<sup>™</sup> test technology with Teradyne, dramatically speeding silicon debug and bring-up

Review today's test strategy on ATE and SLT

**.**U19

5G and mm-wave Test Challenges

## **Case Study in Emerging Markets**

#### ΑI

- ☐ There are two pieces to AI: Infrastructure and Edge

- ☐ Infrastructure will always use SLT for the usual reasons

- What About Edge devices?

- Now it's about volume, cost and reliability

- More like applications processors we do today that have a wide range of test strategies

#### **ADAS**

- □ Automotive IC manufacturers seem to know how to make complex devices without using SLT

- ☐ What about Level 3 / 4 ADAS?

- ☐ What about the higher volume devices (e.g. MCUs)?

Review today's test strategy on ATE and SLT

2019

11

Session 2

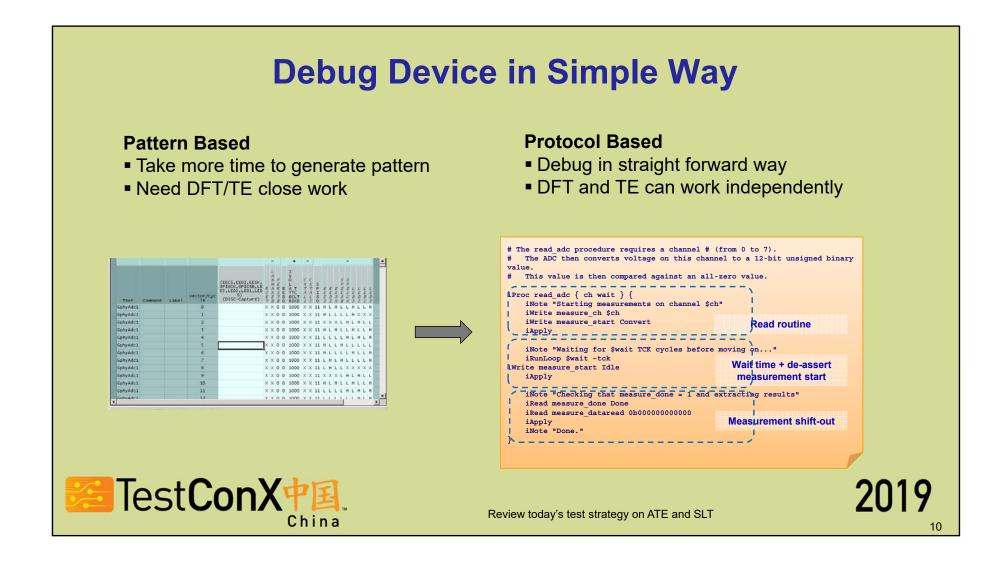

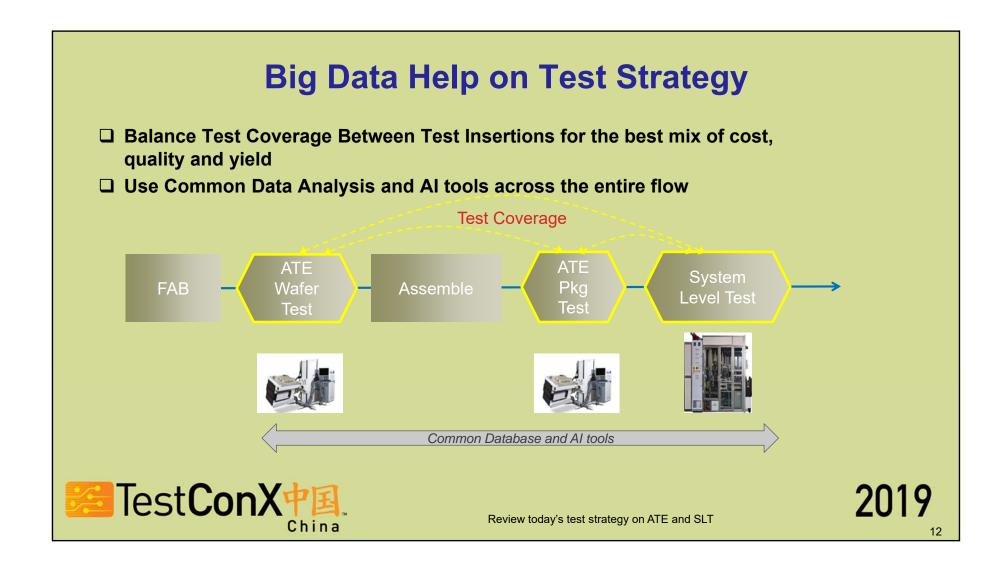

### **Bridge the ATE and SLT**

- Unify programming environments for ATE and functional/SLT

- efficient test deployment, code portability, better failure analysis

- Balance test coverage and test cost based on big data

- Test strategy for each insertion would be different for different application

- New Al techniques will help to improve coverage and identify right strategy

- Outlier detection, etc.

Review today's test strategy on ATE and SLT

2019

13

### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2019 TestConX China workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2019 TestConX China workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2019 TestConX China workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The TestConX China logo and TestConX logo are trademarks of TestConX. All rights reserved.

www.TestConX.org