# October 29, 2019

lest

InterContinental Shanghai Pudong Hotel

# Archive

The Future of Advanced Packaging: Meeting the Challenges

#### Why FO-WLP?

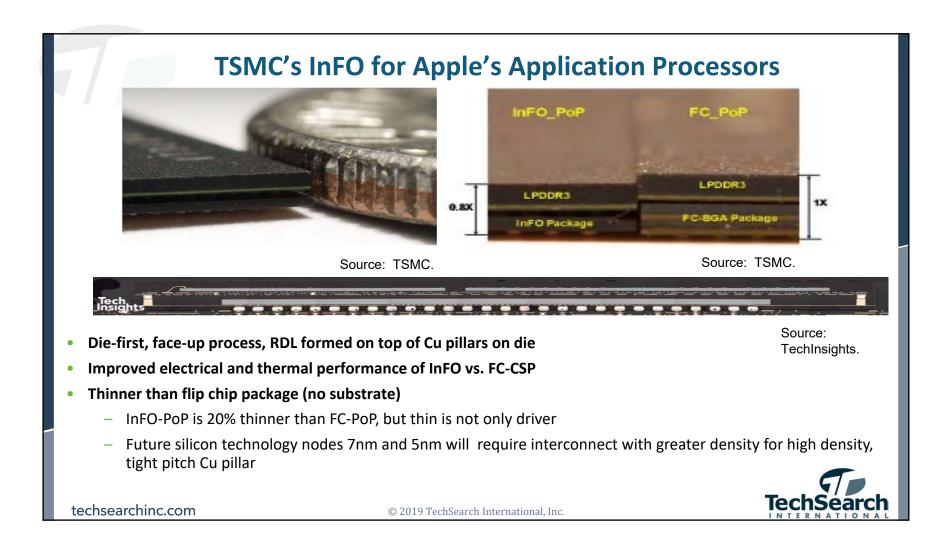

- Smaller form factor, lower profile package: similar to conventional WLP in profile

- Thinner than flip chip package (no substrate)

- Support increased I/O density

- Fine L/S (10/10μm)

- Roadmaps for  $<5/5\mu$ m L/S, future 2/2 $\mu$ m L/S

- Split die package or multi-die package/SiP

- Multiple die in package possible

- Die fabricated from different technology nodes can be assembled in a single package

- Can integrate passives

- Excellent electrical and thermal performance

- Future silicon technology nodes ≤ 5nm will require interconnect with greater density for high density, tight pitch Cu pillar

- Pad pitch of < 55  $\mu$ m will be required and laminate can not achieve

techsearchinc.com

© 2019 TechSearch International, Inc.

The Future of Advanced Packaging: Meeting the Challenges

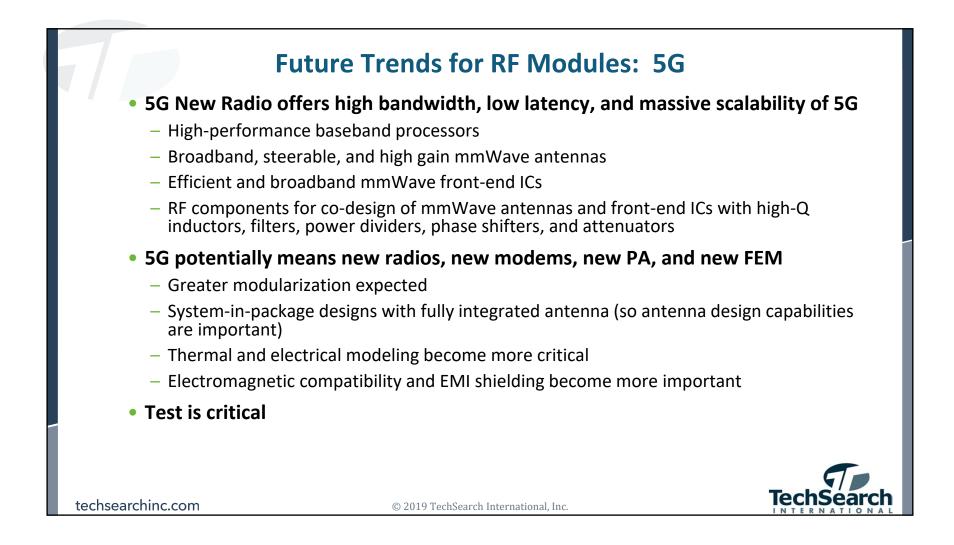

#### **5G Drives New Test Approaches**

- Most existing test and commercial 5G networks exist in the sub-6 GHz range

- Requires some adjustment in software, networks, antenna configuration and other functions

- Only as much change as moving from 3G to 4G

#### 5G advantage comes from shift to mmWave frequencies above 24GHz

- These frequencies provide more bandwidth than other frequencies

- With mmWave the package is the antenna

- 5G capabilities rely on advanced networking capabilities

- Beam-forming (vs. previous generation of omnidirectional or wide-beam antennas)

- Phased arrays (must be able to send and receive shaped waveforms tested under realistic conditions)

- Massive Multiple-input/multiple-output (mMIMO)

- Discussions about over-the-air test

- Some similarities with what is done in automotive radar

- Concerns

- Lack of automated test equipment

- Pressure to move 5G products to market driving many to cobble together own solutions using network analyzers or high-frequency RF analyzers

techsearchinc.com

© 2019 TechSearch International, Inc.

The Future of Advanced Packaging: Meeting the Challenges

techsearchinc.com

© 2019 TechSearch International. Inc.

The Future of Advanced Packaging: Meeting the Challenges

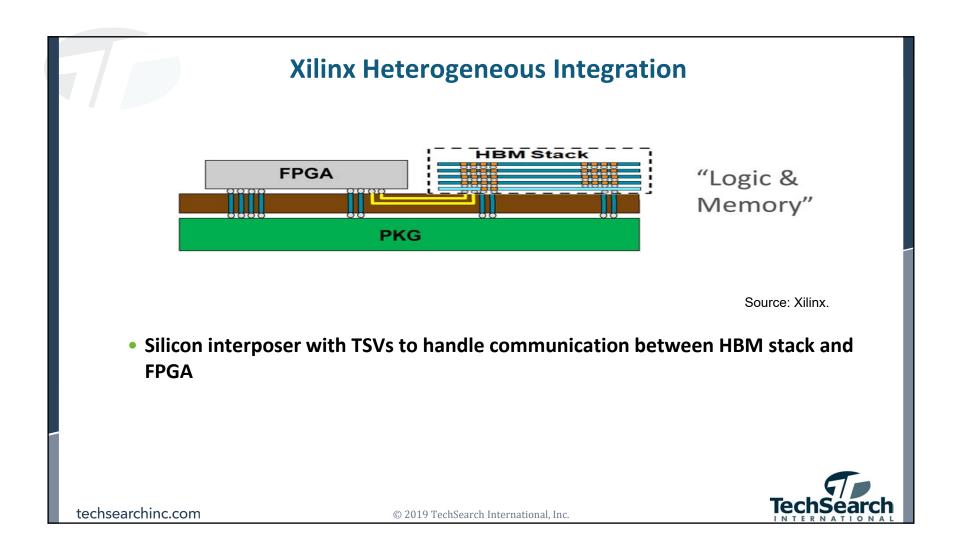

#### Xilinx VIRTEX UltraScale+™

- VIRTEX UltraScale+<sup>™</sup> silicon interposer with TSVs

- Interposer as large as 30 mm x 36 mm

- Metal line stitching used for larger than reticle interposer products at <1µm pitch</li>

- 3 Cu metal layers plus 1 Al layer

- Dual damascene process used to form vias and diameters

- ~0.4µm lines and spaces

- Approximately 660,000 interconnects in the module

Source: Xilinx.

techsearchinc.com

$\ensuremath{\textcircled{O}}$  2019 TechSearch International, Inc.

The Future of Advanced Packaging: Meeting the Challenges

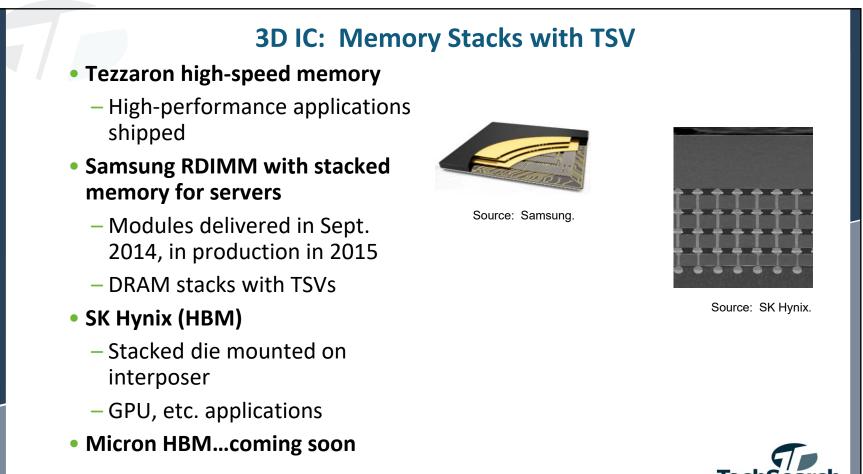

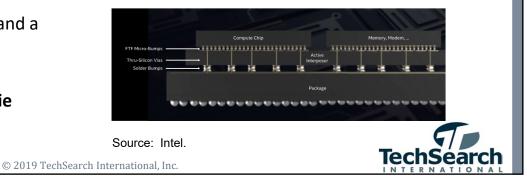

- 3D integration of image sensors, memory and logic

- In production today

- 3D memory stacking

- In production today

- Intel's Foveros

- TSMC's WoW and SoIC

- System on Integrated Chip (SoIC) 3D stack using CoW process to handle <10µm bond pitch between chips

- Two-die stack face-to-face (F2F) and a three die stack

- Use of hybrid bonding

- New forms of 3D stacking (die-to-die interconnects) are coming

techsearchinc.com

Source: TSMC.

# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2019 TestConX China workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2019 TestConX China workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2019 TestConX China workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The TestConX China logo and TestConX logo are trademarks of TestConX. All rights reserved.

## www.TestConX.org