# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2019 TestConX workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2019 TestConX workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2019 TestConX workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

# www.testconx.org

# Time to Market Acceleration with Virtual Validation Farm in Post-Silicon

Angie See Tien Ng & Seong Guan Ooi Intel Corporation

#### **Contents**

- Introduction

- Design Validation in Post-Silicon

- Validation Challenges in Post-Silicon

- TTM Acceleration with Virtual Validation Farm

- Summary

- Acknowledgements

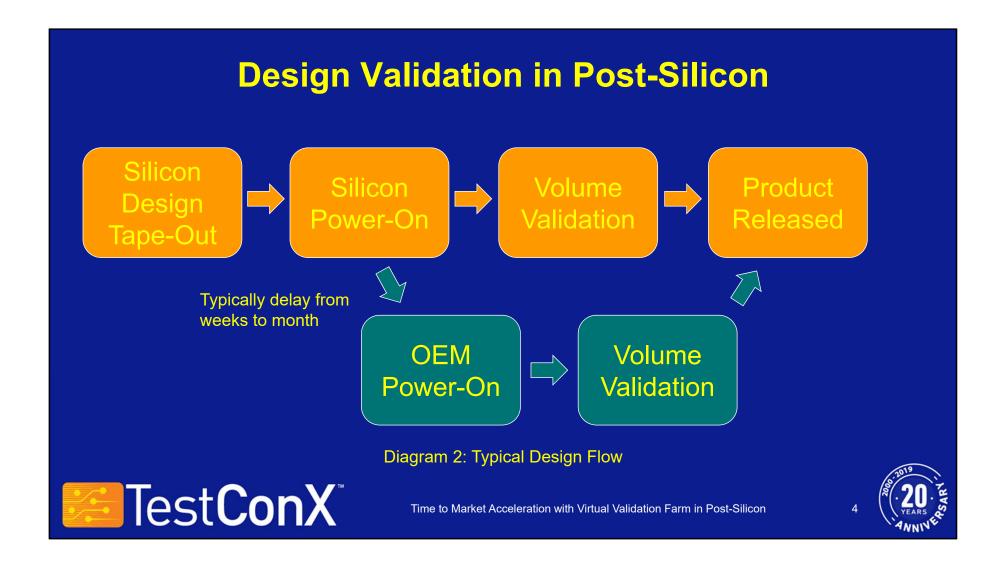

## **Design Validation in Post-Silicon**

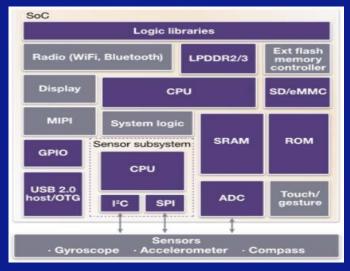

System on Chip (SoC) design consists of multiple predesigned Intellectual Property (IP) blocks, which leads to complexity in design validation/debug

Diagram 1: Sample of SoC IP Blocks

# Validation Challenges in Post-Silicon

- Collaboration from cross functional team in bug sighting

- External IP supplier to support bug sighting

- Limited first article silicon

- Slow in silicon design iteration

# **High Development Cost!**

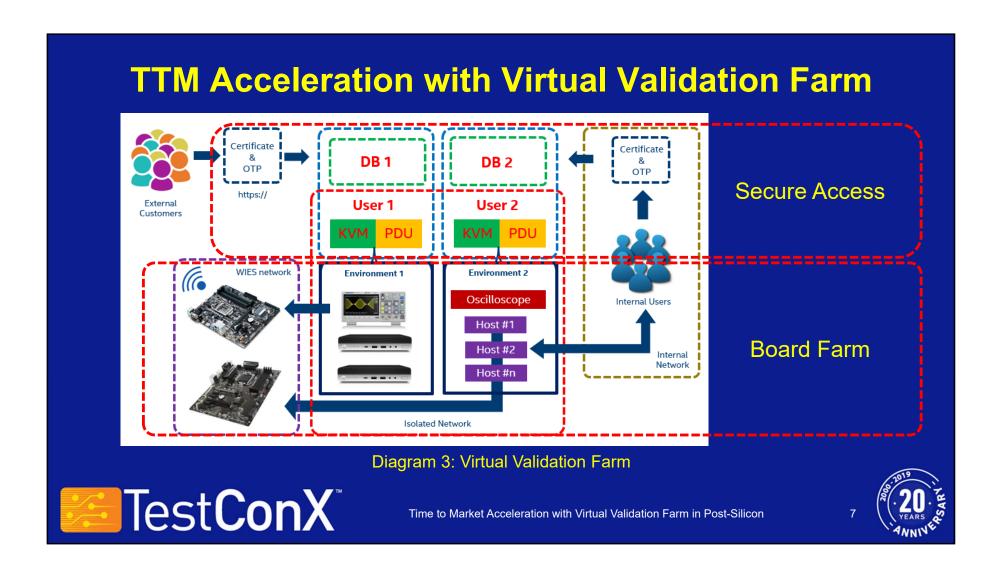

#### TTM Acceleration with Virtual Validation Farm

#### Ideal development environment:

- 1. Secure debug environment

- 2. Self-operate

- 3. 24x7 validation operation

- 4. Remote accessible

- 5. Fast access, anytime, anywhere

# Improved Time-to-Market!

#### TTM Acceleration with Virtual Validation Farm

- Secure Access:

- Online certificate

- Individual login credential

- Secure Virtual PrivateNetwork (VPN)

- One-Time-Passcode (OTP)

#### TTM Acceleration with Virtual Validation Farm

- Board Farm:

- Asset access & control management system

- Platform scheduling system

- Auto OS provisioning solution

- Extensive remote debug features

## **Summary**

- Virtual Validation Farm has helped to transform validation operation in Intel by:

- Reduced 20% cost in reference board purchase

- Improved 3 weeks early customer engagement

- Improved 90% design infra setup time in lab

- Enabled 24x7 validation operation

- Received overwhelming response from users

## **Acknowledgements**

- Eric Chan VP in Intel IoTG

- Board of Directors in Intel Malaysia Design Center (MDC)

- Ng, Hooi Ching IT Malaysia Hub Manager

- Goh, Kean Hean Engineering Lab Manager

- Lim, Hock Lam MDC Lab Manager

- Chang, Siew Cuong Engineering Lab Manager

- Mamat, Siti Zurmarini Post-Silicon Technologist