# TWENTIETHANNUAI

estConX

### March 3 - 6, 2019

Hilton Phoenix / Mesa Hotel Mesa, Arizona

Archive

## **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2019 TestConX workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2019 TestConX workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2019 TestConX workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

Session 5B Presentation 3

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

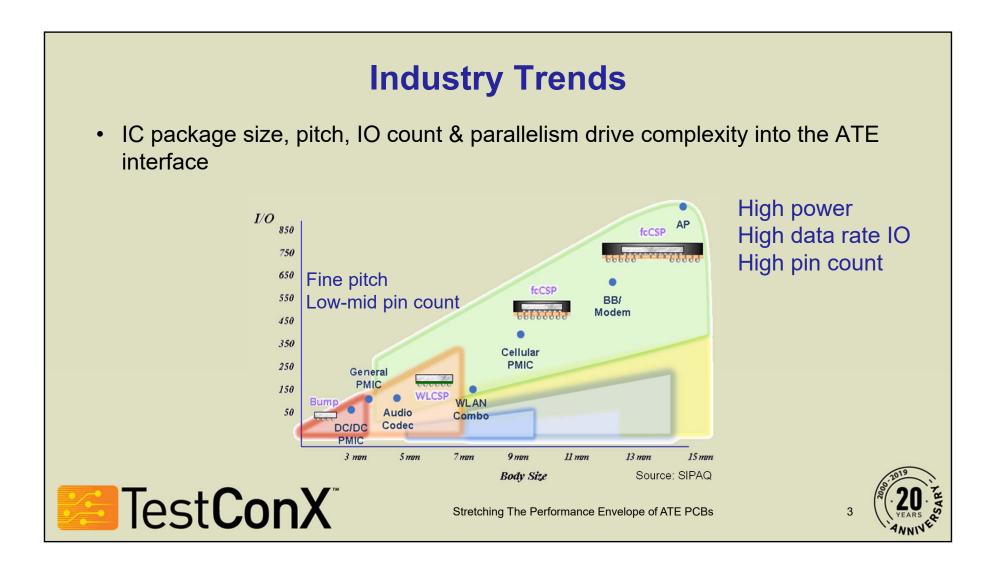

| <ul> <li>Impact on Production Test ATE Interface</li> <li>Basic and even advanced PCB manufacturing techniques need augmenting just to keep up</li> </ul> |                            |                      |               |                 |                            |                                                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------|---------------|-----------------|----------------------------|------------------------------------------------------------|--|--|--|

| Complexity                                                                                                                                                | Device Pitch               | Device Ball<br>Count | Parallel Test | Power (Current) | Speed                      | Test Cell Configuration                                    |  |  |  |

| Low                                                                                                                                                       | 0.5mm - 1mm                | 100                  | 1up – 4up     | < 1A            | <1GBS                      | Singulated package test<br>Staggered die                   |  |  |  |

| Med                                                                                                                                                       | 0.40mm<br>0.35mm<br>0.30mm | 200+                 | 4up – 16up    | 100A / DV 50mv  | 10GBS                      | WLSCP<br>Extended temp range<br>(Automotive)               |  |  |  |

| High                                                                                                                                                      | < 0.30mm                   | 6000                 | 16up - 128x   | 400A / DV <25mV | 28GBS NRZ /<br>112GBS PAM4 | Direct Attach<br>1 mil Flatness<br>pad condition<br>OTA 5G |  |  |  |

Stretching The Performance Envelope of ATE PCBs

Test**ConX**

Translating Specs - PCB Materials & Specifications

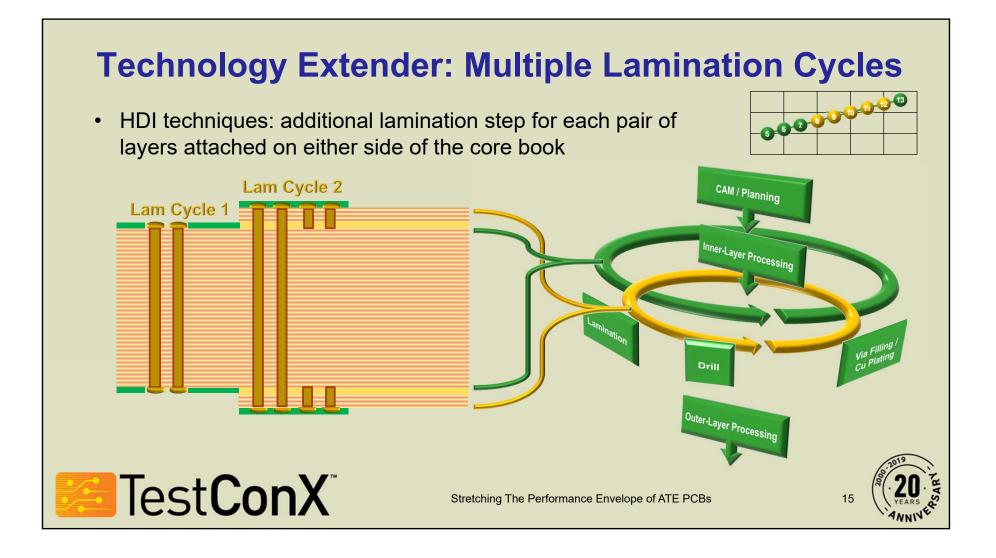

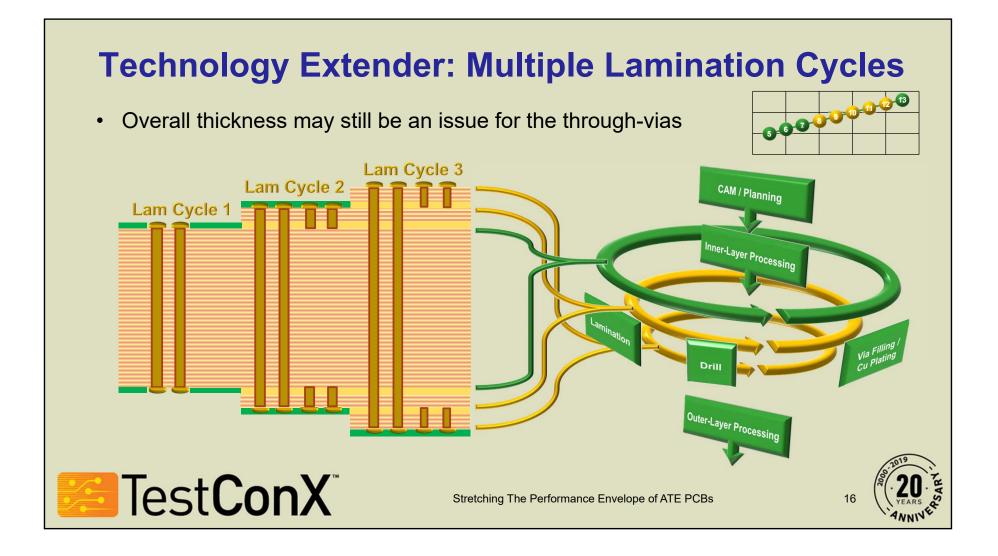

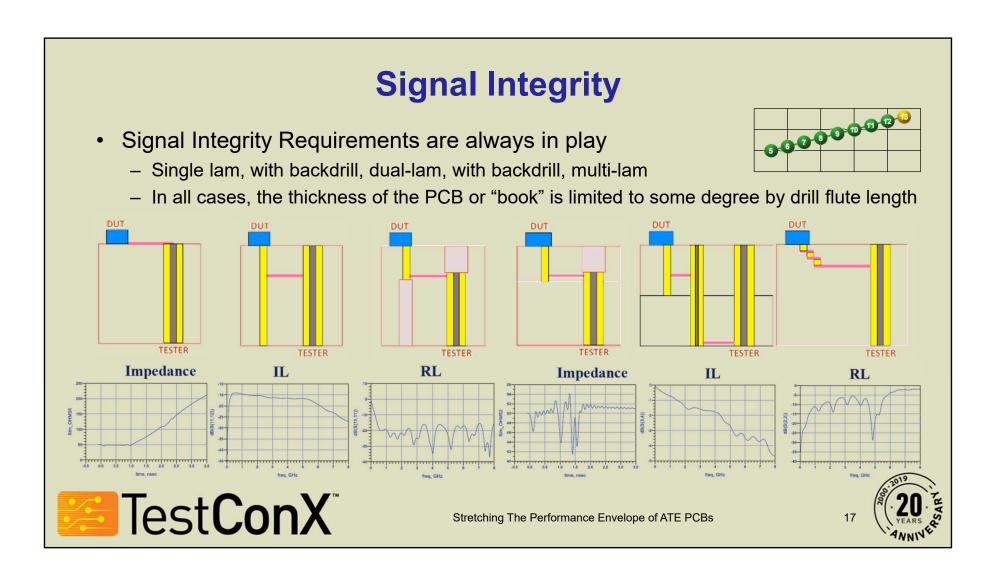

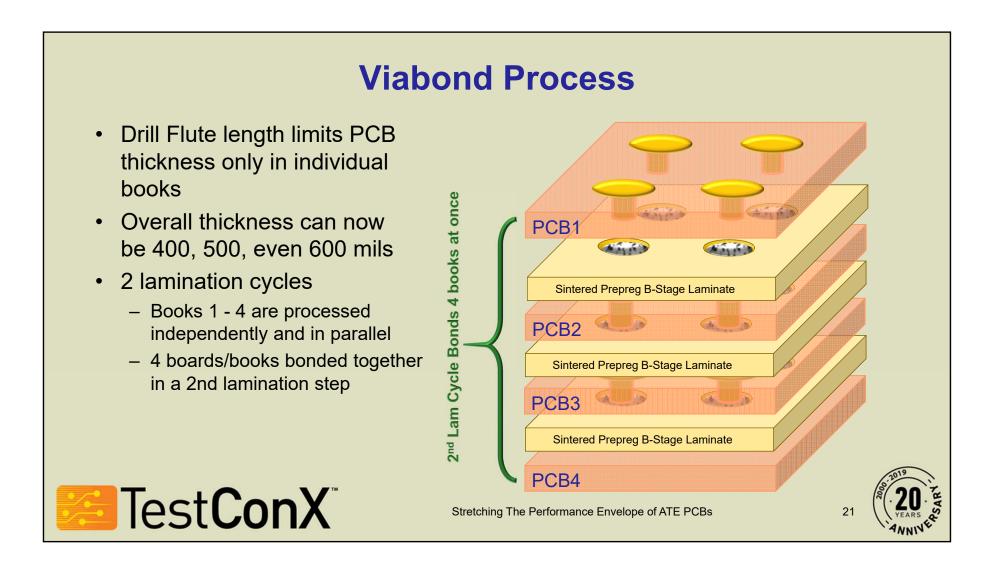

### **PCB Thickness vs Drill Flute Length** Dimensions (in) Drill Point Now ramp up the complexity factors: Size Angle DUT pin count / parallelism drives up layer count 10mm 0.0040 1/8 0.0700 1 1/2 118° 13mm 0.0050 1/8 0.0700 1 1/2 118° Layer count drives overall PCB thickness #97 0.0059 1/8 0.1200 $1 \frac{1}{2}$ 118° Encounter limitations of PCB drill dimensions, #96 0.0063 1/8 0.1200 $1 \frac{1}{2}$ 118° specifically Flute Length #95 0.0067 1/8 0.1200 $1 \frac{1}{2}$ 118° #94 0.0071 0.1500 1 1/2 1/8 118° Flute Length limits PCB Thickness • #93 0.0075 1/8 0.1500 1 1/2 118° D #92 0.0079 1/8 0.1500 1 1/2 118° #91 0.0083 1/8 0.1500 $1 \frac{1}{2}$ 118° #90 0.0087 1/8 0.1500 $1 \frac{1}{2}$ 118° #89 0.0091 1/8 0.2200 $1 \frac{1}{2}$ 118° #88 0.0095 1/8 0.2200 $1 \frac{1}{2}$ 118° Note that Flute Length varies with drill diameter .25mm 0.0098 1/8 0.2200 1 1/2 118° Smaller the drill diameter, shorter the flute length #87 0.0100 1/8 0.2200 1 1/2 118° 10 mil drill, flute length = 0.220" http://www.kyoceramicrotools.com/micro/drilling/Series-105-6 6 mil drill, flute length = 0.120" Test**ConX** Stretching The Performance Envelope of ATE PCBs

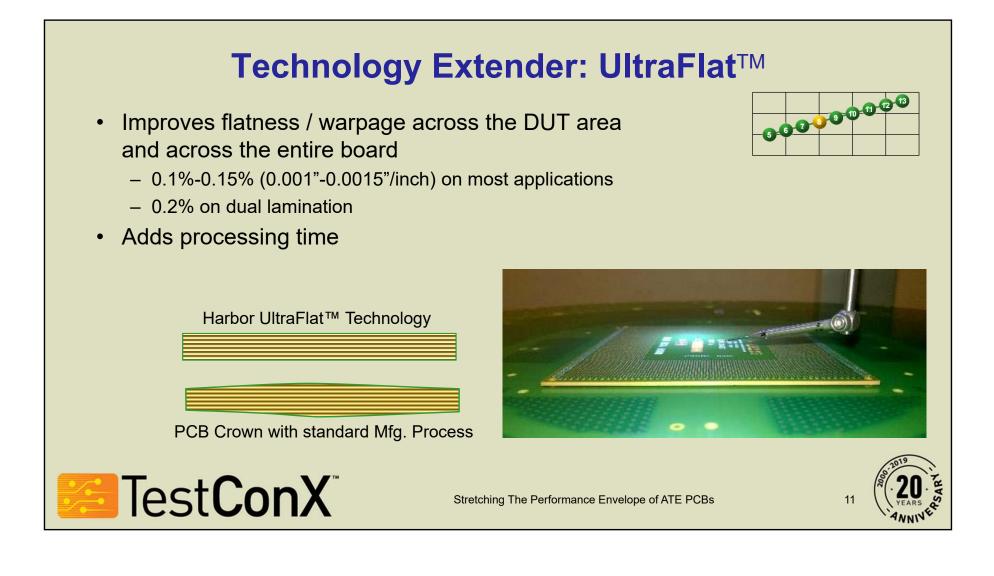

- Multi-site testing effectively increases area of DUT site

- So-called 'Direct Attach' applications which require excellent planarity (1 mil across entire DUT area)

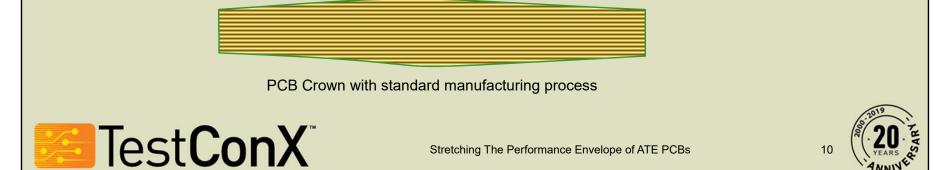

- In the PCB, Cu density is usually greatest at center / DUT sites

- Prepreg squeezes out the edge of the panel during lamination

- Rate varies with Cu density

- · Creates a board with 'crown' at / near center of PCB

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

Translating Specs - PCB Materials & Specifications

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

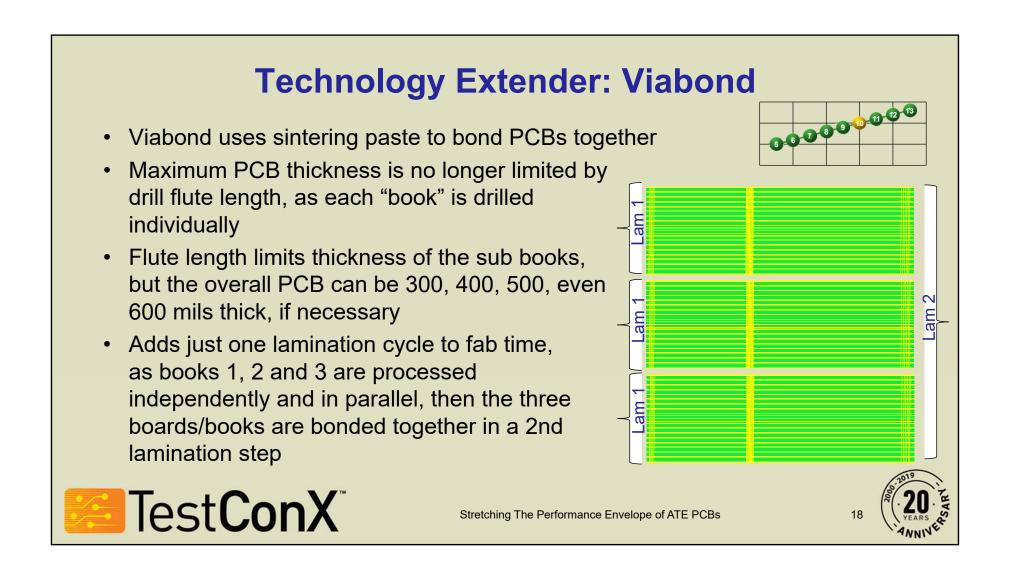

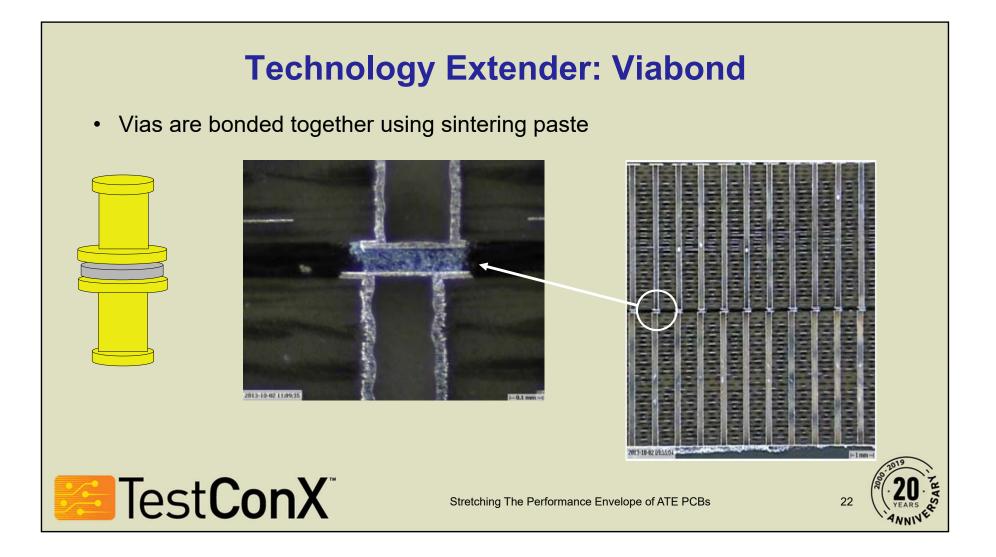

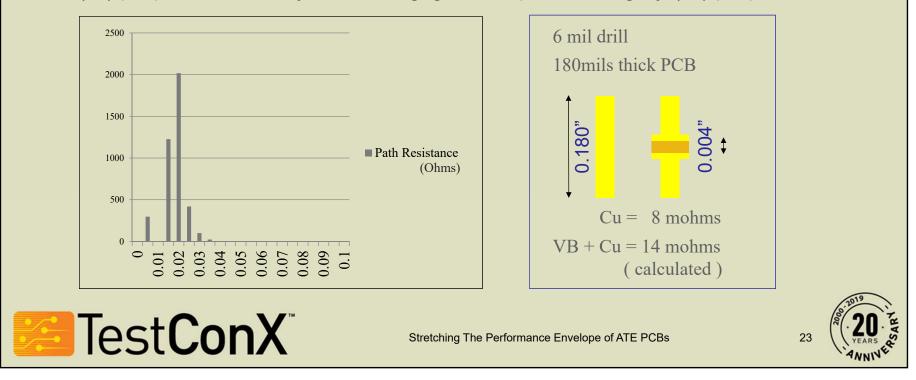

### Viabond Path Resistance

• Delta in path resistance between Cu and Viabond is negligible for signal integrity (SI) purposes, but may not be negligible for power integrity (PI) purposes

Translating Specs - PCB Materials & Specifications

### Viabond Yield

- Yield presented the biggest challenge, took a long time to get right

- Now approaching parity with the more traditional PCB fabrication techniques

- Sintering paste recipes are straightforward

- Applying to ATE PCBs is another matter

- Large form factor PCB, large number of vias

- In-process metrology is key (AOI, Kelvin flying probe test)

Stretching The Performance Envelope of ATE PCBs

Translating Specs - PCB Materials & Specifications

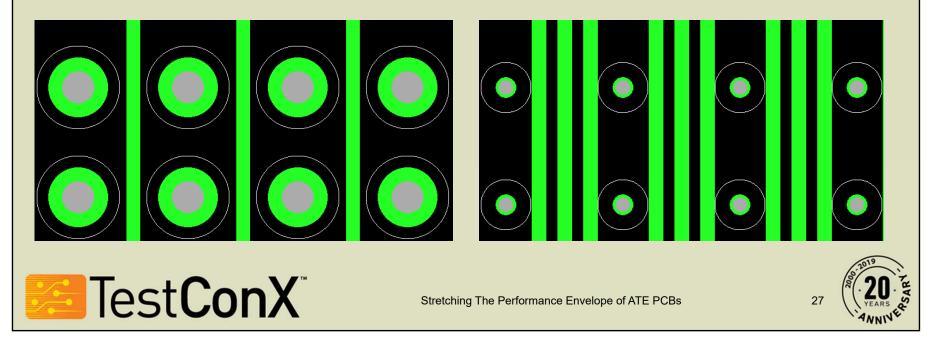

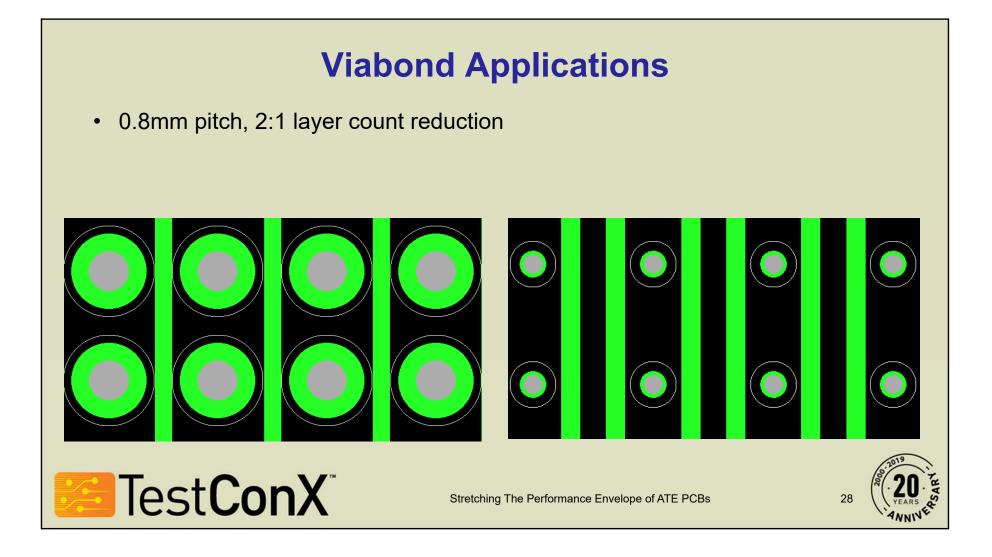

- Overall layer count can be reduced by improving DUT area breakout routing density

- 1mm pitch: 3:1 layer reduction in signal layers

TestConX Workshop

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

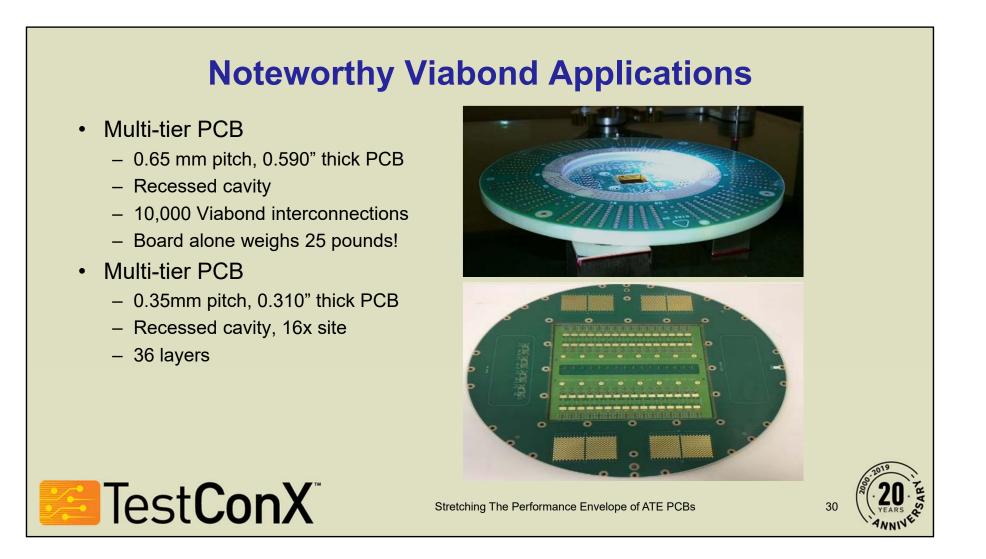

### **Noteworthy Viabond Applications**

- Motherboard Daughterboard

- Daughterboard:

Fine pitch, higher cost PCB

- Motherboard:

Gross pitch, low cost PCB

- Space transformation from PCB pitch to IC package pitch

- At DUT site or to adapt to specialty component footprints

Stretching The Performance Envelope of ATE PCBs

Translating Specs - PCB Materials & Specifications

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

Stretching The Performance Envelope of ATE PCBs

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

TestConX Workshop

Translating Specs - PCB Materials & Specifications

### **Viabond Next Steps**

- In-depth Power Integrity characterization

- Signal Integrity / via tuning

- Simulation to measurement correlation

- In-process metrology continuous improvement

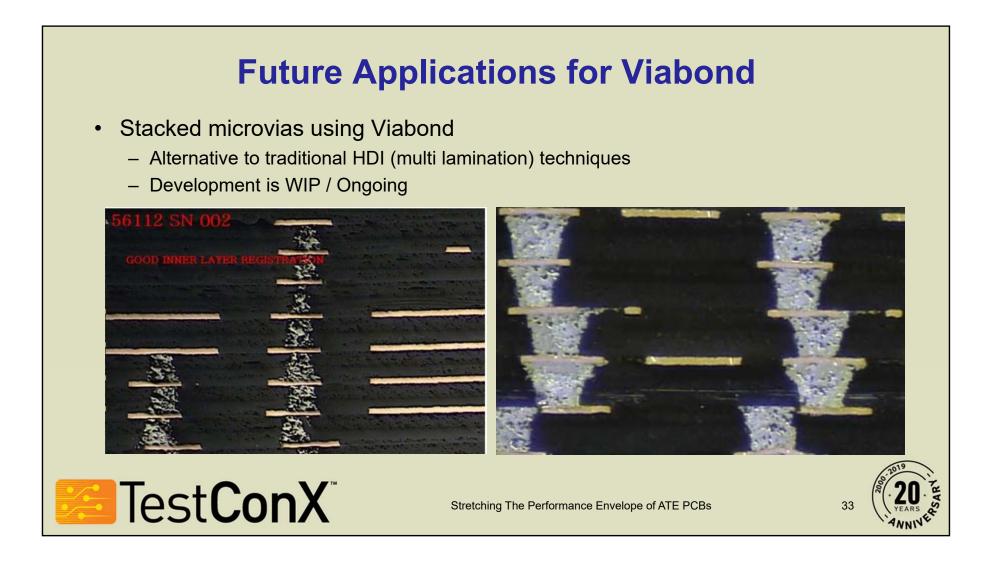

- Stacked via characterization

- Space transformer integration studies

- Flatness

- Design & fabrication timeline compression

Stretching The Performance Envelope of ATE PCBs

Translating Specs - PCB Materials & Specifications

| <ul> <li>Summary:</li> <li>Viabond extends the reach of what can be achieved in the ATE Interface PCB</li> <li>Thicker, high aspect ratio, high layer count PCBs</li> <li>Fine pitch holes (small drills) through thick PCBs</li> <li>Alternative to sequential lamination, with fewer lamination cycles</li> </ul> |               |                      |              |           |              |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------------|--------------|-----------|--------------|--|--|--|--|

|                                                                                                                                                                                                                                                                                                                     | Flip Drilling | Multiple Laminations | Backdrilling | UltraFlat | Viabond      |  |  |  |  |

| Layer Count                                                                                                                                                                                                                                                                                                         | $\otimes$     | $\otimes$            | $\otimes$    |           | $\otimes$    |  |  |  |  |

| DUT Pitch                                                                                                                                                                                                                                                                                                           | $\otimes$     | $\otimes$            | $\otimes$    |           | $\otimes$    |  |  |  |  |

| Routing Density                                                                                                                                                                                                                                                                                                     |               | $\otimes$            | $\otimes$    |           | $\otimes$    |  |  |  |  |

| Signal Integrity                                                                                                                                                                                                                                                                                                    |               | $\otimes$            | $\otimes$    |           | $\otimes$    |  |  |  |  |

| Power Delivery                                                                                                                                                                                                                                                                                                      | $\otimes$     | $\otimes$            |              |           | $\otimes$    |  |  |  |  |

| Direct Attach                                                                                                                                                                                                                                                                                                       |               |                      |              | $\otimes$ | $\bigotimes$ |  |  |  |  |

| Stretching The Performance Envelope of ATE PCBs 36                                                                                                                                                                                                                                                                  |               |                      |              |           |              |  |  |  |  |

TestConX Workshop