# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the proceedings of the 2019 TestConX workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2019 TestConX workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2019 TestConX workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by TestConX or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by TestConX. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

"TestConX" and the TestConX logo are trademarks of TestConX. All rights reserved.

# www.testconx.org

# SLT Test Fundamentals & Challenges

John Yi AMD

## **Contents**

- General Purpose of SLT

- SLT Challenges

- Customization vs Standardization

- Next generation features

- Conclusion

# **Purpose of SLT**

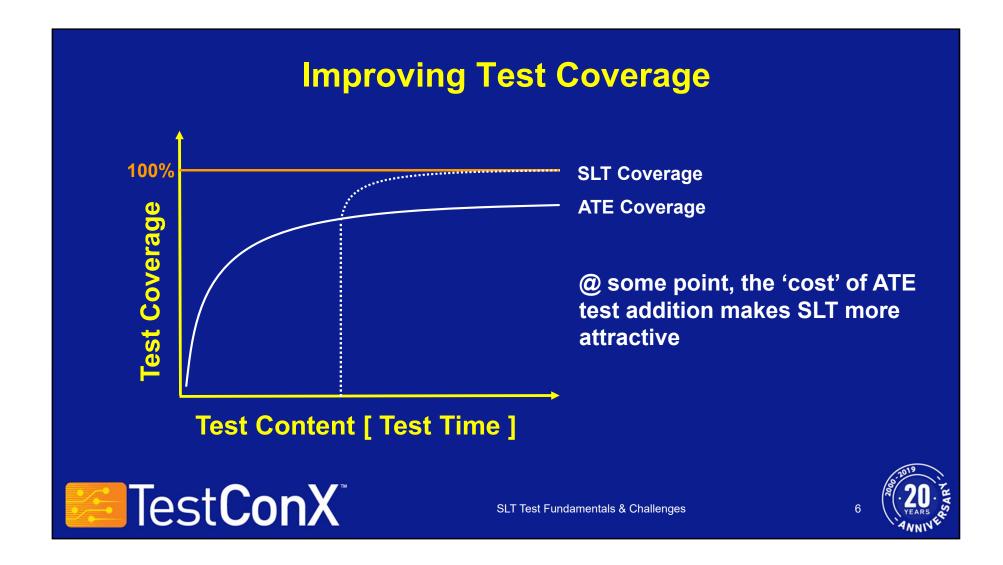

- 1. Fills the ATE coverage gap

- 2. Easier to match end-user experience

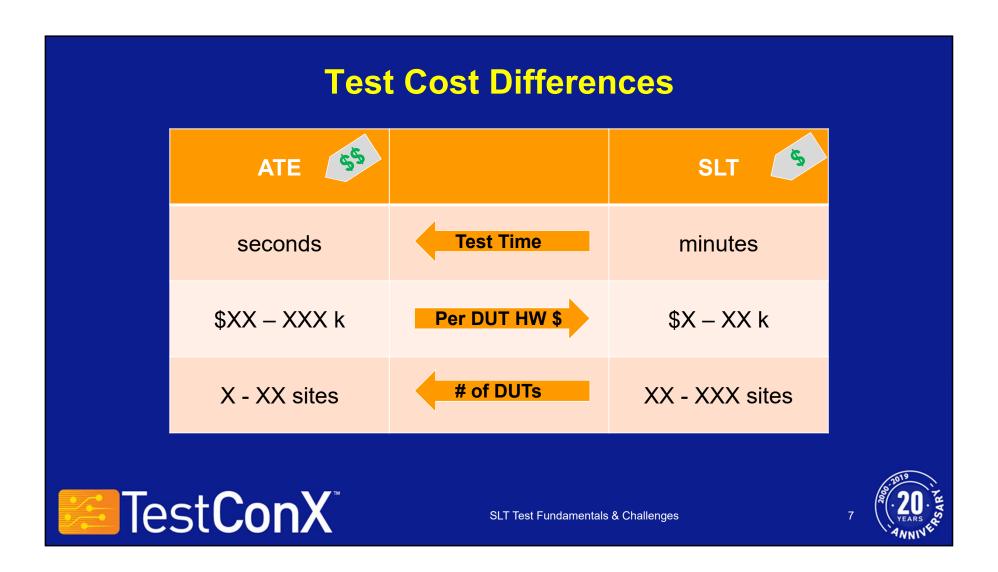

- 3. Lower Test costs

## **Baseline Test Insertions**

ATE Wafer Sort

- Coarse Performance Bucketing

- Stuck-at-Faults

Burn-in Wafer/Package

Accelerate Reliability Defects **Yield > 98%**

ATE Package Test

- Finer Performance Binning

- Assembly defects

- Additional faults (temp or voltage related)

**Yield > 99.xx%**

SLT Package Test

- Verify Performance Bin

- dPPM faults

Which of these matches better with End-User hardware & software?

ATE

SLT

**End-User**

Wring This Out - System Level Test

# **SLT Challenges**

- 1. Customization vs Standardization

- End-user modifications for SLT

- Leverage ATE or Burn-in for SLT

- 2. Next Generation Features → Higher Test Costs

- o Power management

- o I/O Protocols & Speed

- o More features → Longer test times → More Capacity

Test**ConX**®

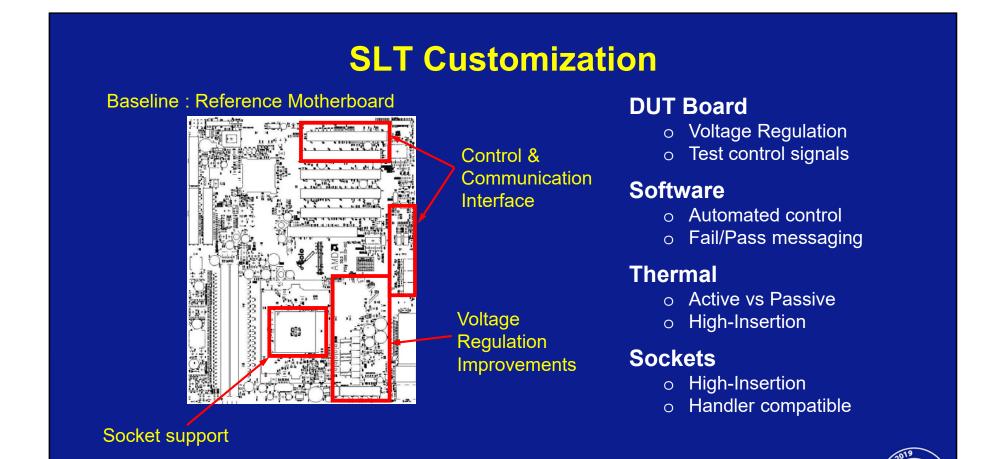

## **SLT Customization**

Active Thermals

High-Insertion socket

#### **DUT Board**

- Voltage Regulation

- o Test control signals

#### Software

- Automated control

- o Fail/Pass messaging

#### **Thermal**

- o Active vs Passive

- o High-Insertion

#### **Sockets**

- o High-Insertion

- o Handler compatible

Wring This Out - System Level Test

## **ATE or Burn-in SLT Integration**

### **Integrate SLT functions into ATE or Burn-in Infrastructure**

[ Accurate, Stable, Repeatable, Debuggable, Scalable ]

#### **ATE limitations**

- SLT Test Time constraints

- ATE Instrumentation constraints

- SLT Component reliability

#### **Burn-in limitations**

- SLT Test Time constraints

- o Burn-in Board space constraints

# **Next Gen Features - Power Management**

**Single P-State**

Multiple P-States

Single power plane

Multiple Finer P-States Independent power planes

Px - Power State (Voltage, Frequency)

Wring This Out - System Level Test

## **Next Gen Features - I/O Protocols**

[ Multiple connectors | Faster bit-rates | Advanced Power Management ]

DP

$$1.0 \rightarrow 1.1 \rightarrow 1.2 \rightarrow 1.3 \rightarrow 1.4$$

HDMI  $1.0 \rightarrow 1.1 \rightarrow 1.2 \rightarrow 1.3 --> 1.4 \rightarrow 2.0 \rightarrow 2.1$

USB

**USB Type A/B/C**

USB  $1.0 \rightarrow 2.0 \rightarrow 3.0 \rightarrow 3.1 \rightarrow 3.2$

PCle  $1.0 \rightarrow 2.0 \rightarrow 3.0 \rightarrow 4.0 \rightarrow 5.0$

# **Concluding Remarks**

- New Product features will continue to move faster than ATE or Burn-in capabilities... increasing the test cost burden into SLT.

- SLT in many ways is a mitigation to cover the coverage gap to guarantee end-user expectations.

- SLT Standardization (or integration into other test equipment) is starting to expand in both hardware and software environments allowing for better test support and scalability.