# NINETEENTH ANNUAL Burn-in & Test Strategies Workshop

## March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Session 6 Presentation 2

**BiTS 2018**

Making Certain - Debug and Validation

# Thermal Performance of Burn-In Board for Bare Die Qualification

#### Sujata Paul - Cisco Systems Jason Cullen - Plastronics

BiTS Workshop March 4 - 7, 2018

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

March 4-7, 2018

Making Certain - Debug and Validation

- Theoretical Modeling Thermal Simulations

- Real-World Testing Thermal Measurements

- Conclusions

Making Certain - Debug and Validation

**Objective:** Re-Visit 2 BiTS Presentations to see if we can simulate & predict die temperature of CPAK Module Components on a Mother Board.

-

......

CISCO

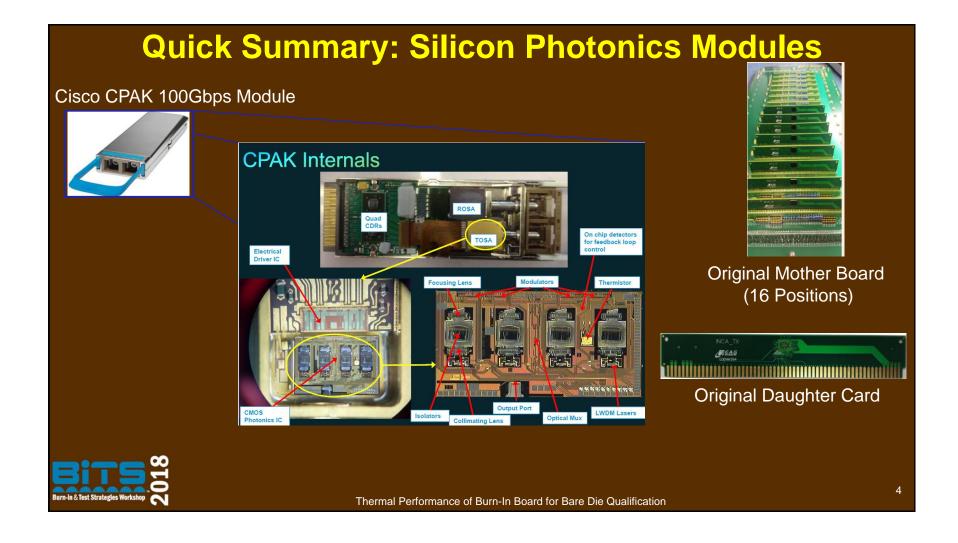

#### Reliability Characterization of Unpackaged (bare) die for Silicon Photonics module

Cisco: Sujata Paul, Andrew Fong, Samir Alqadhy, Huy Nguyen, Zoe Conroy EAG (Evans Analytical Group): Jag Jassal, Tom Elliot

| B           | 1         | 75             |   |

|-------------|-----------|----------------|---|

| Burn-in & T | est Strat | egies Workshop | , |

2016 <u>BiTS</u> Workshop March 6 - 9, 2016

Jason Cullen Plastronics Sockets & Connectors

2016 BiTS Workshop March 6 - 9, 2016

PLASTRONICS Sockets & connectors

3

Session 6 Presentation 2

Making Certain - Debug and Validation

**Burn-in & Test Strategies Workshop**

Session 6 Presentation 2

Making Certain - Debug and Validation

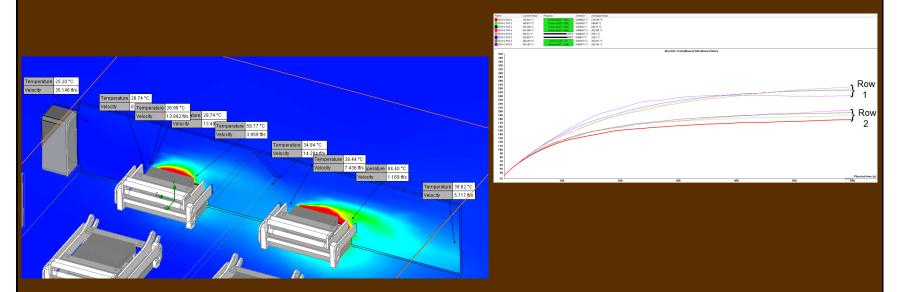

#### **Quick Summary: Modeling Socket Thermal Performance**

For passively cooled components, the temperature profile variance between socket locations on a BIB was significant, on the order of 10°C.

Making Certain - Debug and Validation

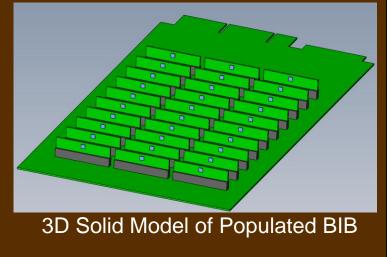

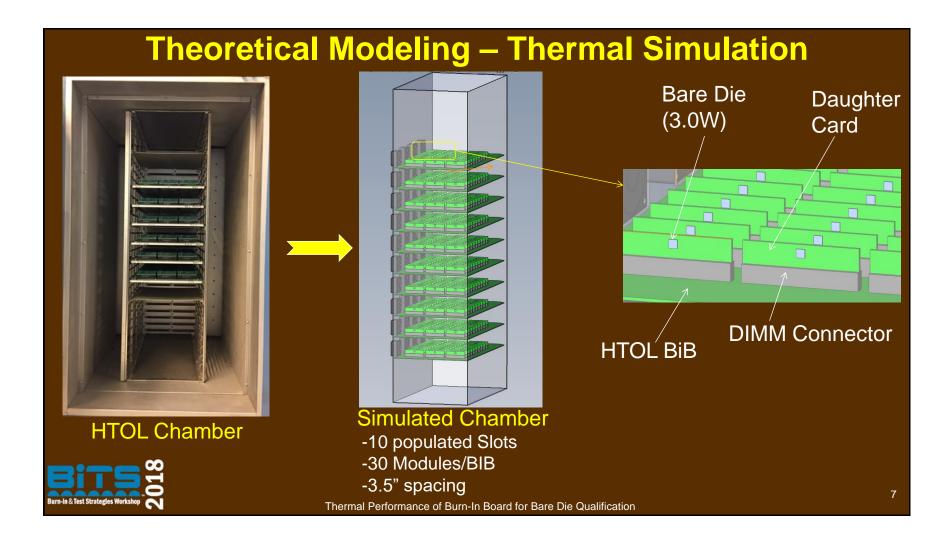

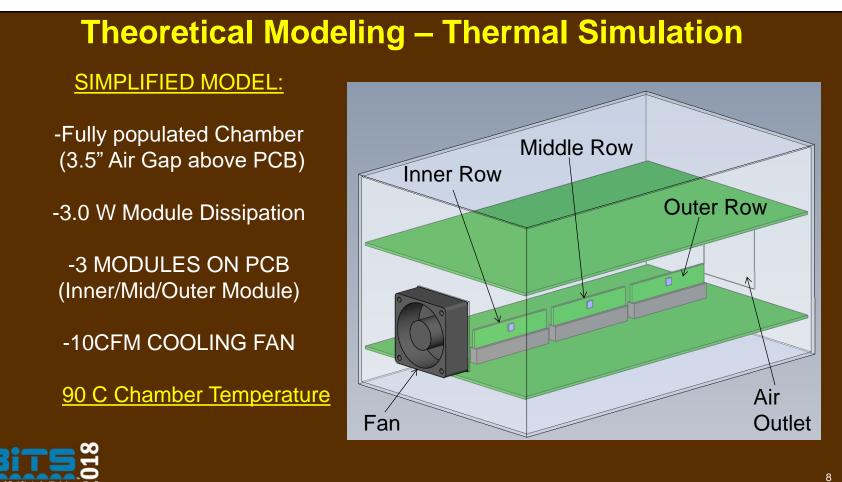

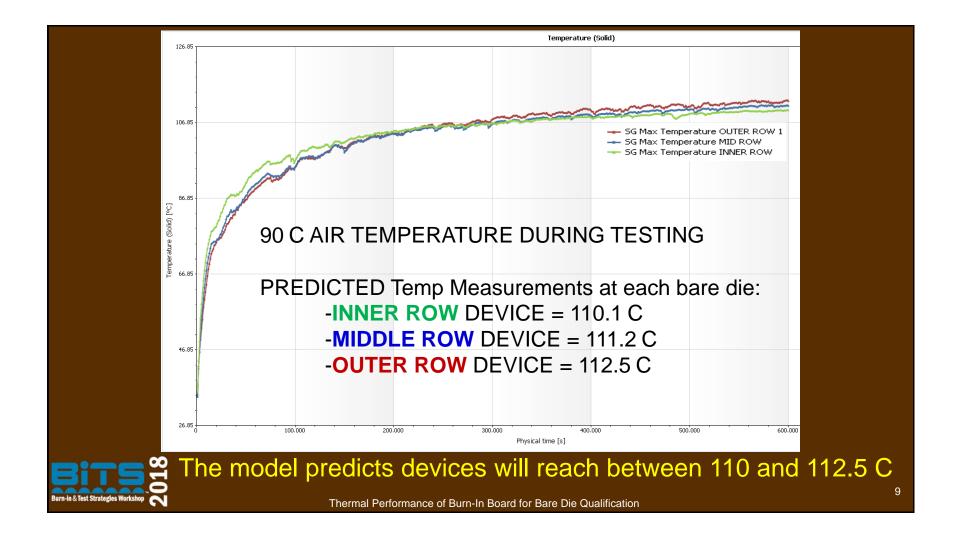

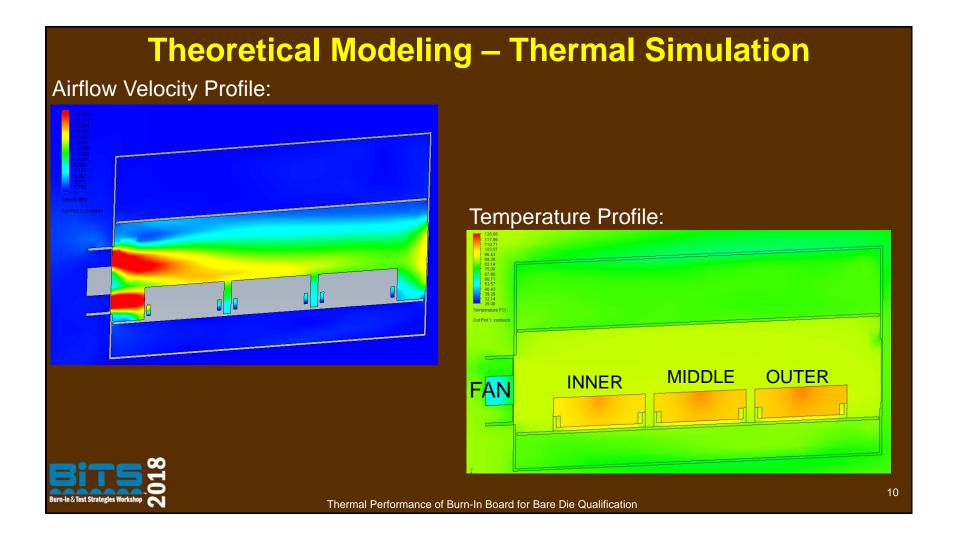

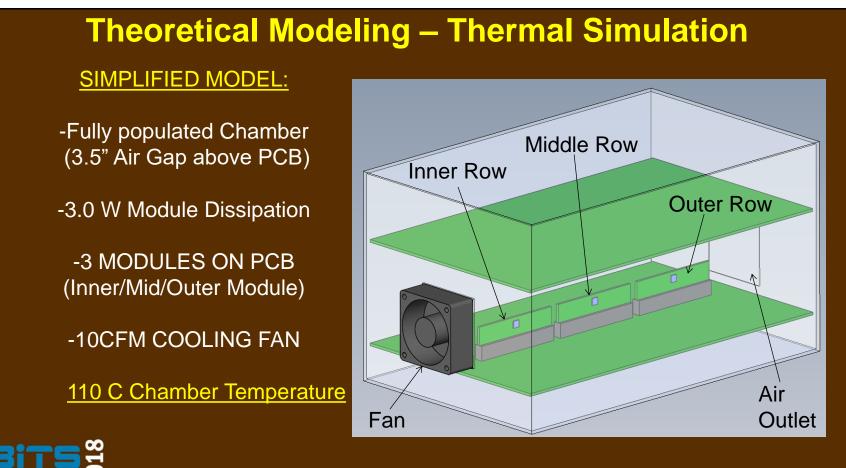

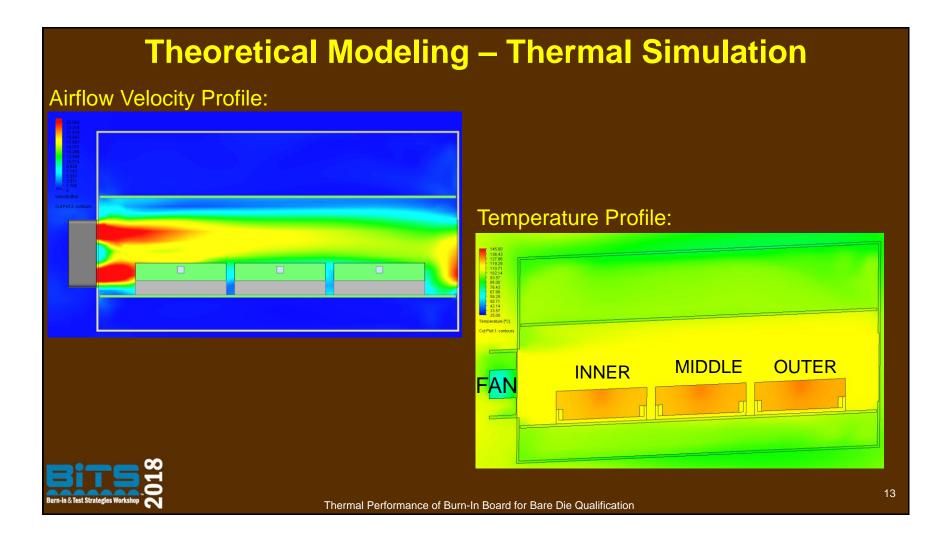

#### **Theoretical Modeling – Thermal Simulation**

#### Since 2016, the HTOL BIB has changed: -Larger profile to accommodate 30 modules (was 16). -3 x 10 Configuration

Thermal Performance of Burn-In Board for Bare Die Qualification

6

**Bits 2018**

Session 6 Presentation 2

Making Certain - Debug and Validation

# **Bits 2018**

Making Certain - Debug and Validation

Thermal Performance of Burn-In Board for Bare Die Qualification

**Burn-in & Test Strategies Workshop**

Making Certain - Debug and Validation

Session 6 Presentation 2

Making Certain - Debug and Validation

Burn-in & Test Strategies Workshop

Making Certain - Debug and Validation

Making Certain - Debug and Validation

Burn-in & Test Strategies Workshop

Session 6 Presentation 2

Making Certain - Debug and Validation

**Burn-in & Test Strategies Workshop**

Making Certain - Debug and Validation

#### **Real-World Testing – Thermal Measurements**

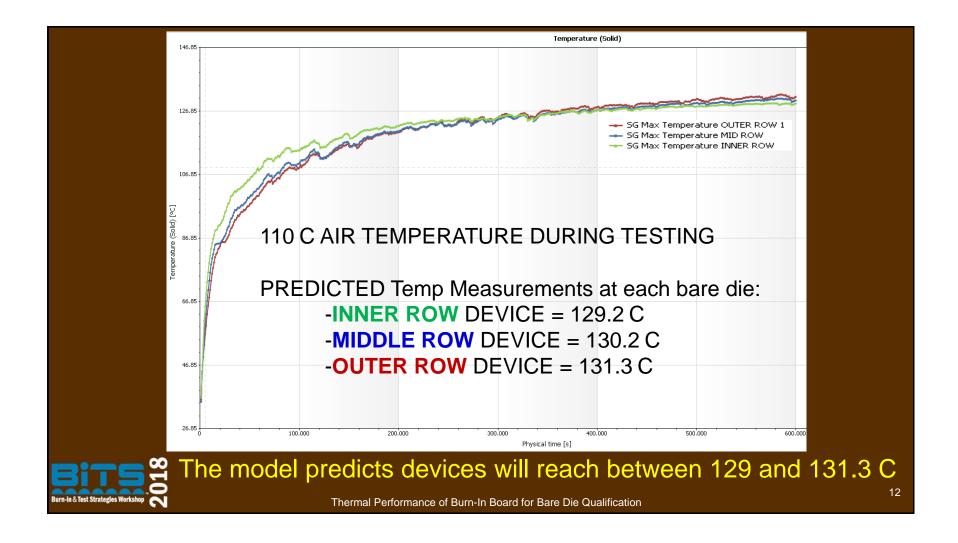

-Measurements recorded with thermocouple at bare die surface Die Location ID: Inner Row = A ; Middle Row = B; Outer Row = C

| Oven temp set to 90C |       |                         |       |       |  |     |

|----------------------|-------|-------------------------|-------|-------|--|-----|

|                      | 4     | 4 parts to collect temp |       |       |  |     |

| POSITION             | A1    | A8                      | B6    | C10   |  | PO  |

| DIE TEMPERATURE      | 103.5 | 103.9                   | 102.6 | 101.9 |  | DIE |

| SIMULATION VALUE     | 110.1 | 110.1                   | 111.2 | 112.5 |  | SIN |

|                      | 6.4%  | 5.9%                    | 8.4%  | 10.4% |  |     |

| Oven temp set to 110C |                         |       |       |       |  |

|-----------------------|-------------------------|-------|-------|-------|--|

|                       | 4 parts to collect temp |       |       |       |  |

| POSITION              | A1                      | A8    | B6    | C10   |  |

| DIE TEMPERATURE       | 124.4                   | 125.3 | 123.3 | 122.8 |  |

| SIMULATION:           | 129.2                   | 129.2 | 130.2 | 131.3 |  |

|                       | 3.8%                    | 3.2%  | 5.6%  | 7.0%  |  |

| Oven temp set to 100C |                         |       |       |       |  |

|-----------------------|-------------------------|-------|-------|-------|--|

|                       | 4 parts to collect temp |       |       |       |  |

| POSITION              | A1                      | A8    | B6    | C10   |  |

| DIE TEMPERATURE       | 112.9                   | 114.8 | 112.9 | 112.5 |  |

| SIMULATION:           | 119.8                   | 119.8 | 121.1 | 122.3 |  |

|                       | 6.1%                    | 4.4%  | 7.2%  | 8.7%  |  |

Thermal Performance of Burn-In Board for Bare Die Qualification

**Burn-in & Test Strategies Workshop**

Making Certain - Debug and Validation

### Conclusions

- Simulated results were between 3.2% and 10.2% higher than actual measured values.

- The difference could be attributed to modeling of the Daughter Card (Negligible heat transfer to BIB) and/or the airflow inlet/exhaust values.

- Simulation results on the high side of temperature protect from a possible thermal runaway condition.

- (i.e. Initial Chamber Setting)

- Simulation is still not a full substitute for real-world testing, but it is a valuable starting point!