**Burn-in & Test Strategies Workshop**

March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

## Archive

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

### www.bitsworkshop.org

# Path to First Boot and Volume Validation: Challenges and Opportunity

Vikas Kumar Intel

BiTS Workshop March 4 - 7, 2018

#### **Agenda**

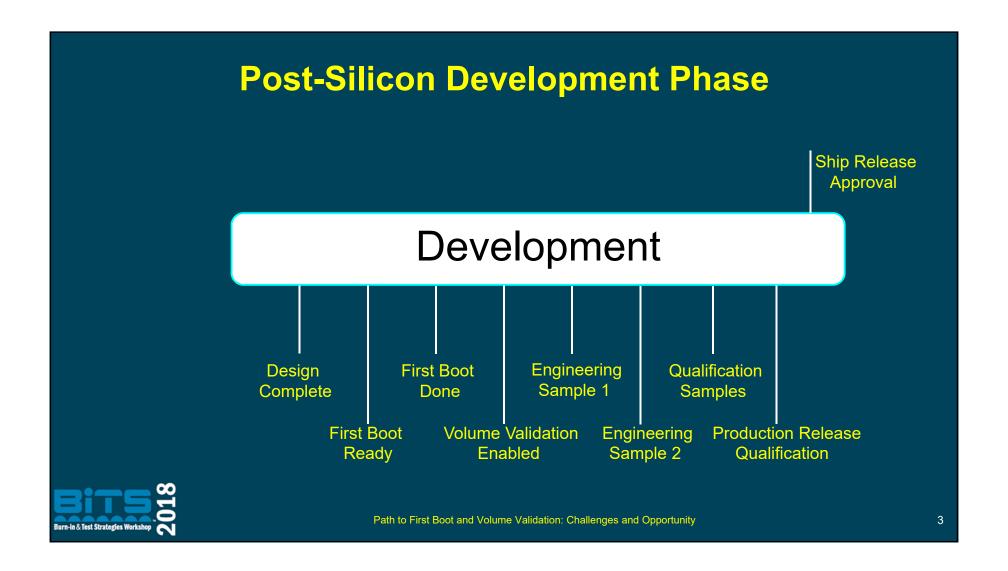

- Post-Silicon Development Phase

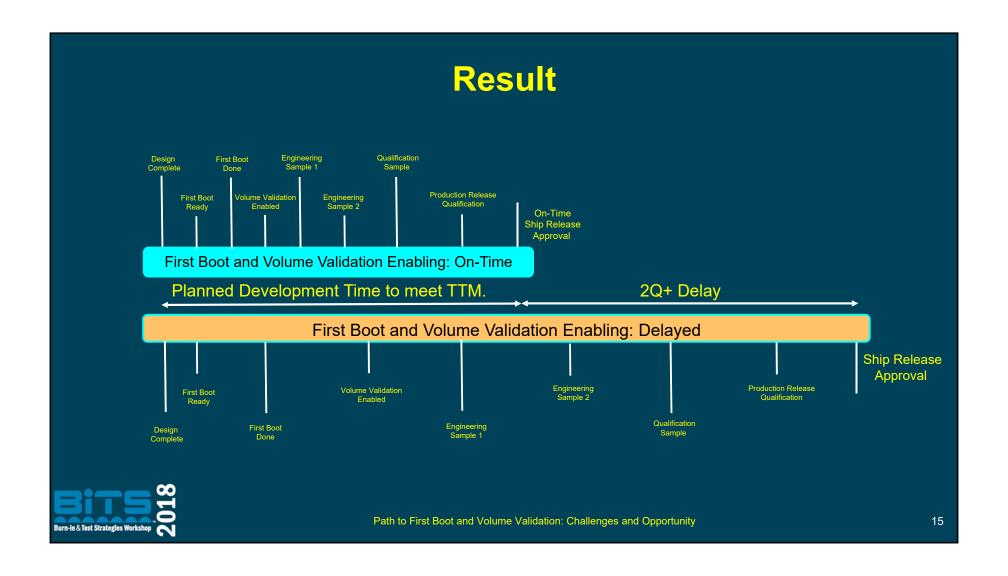

- Importance of First Boot and Volume Validation Enabling of SoC.

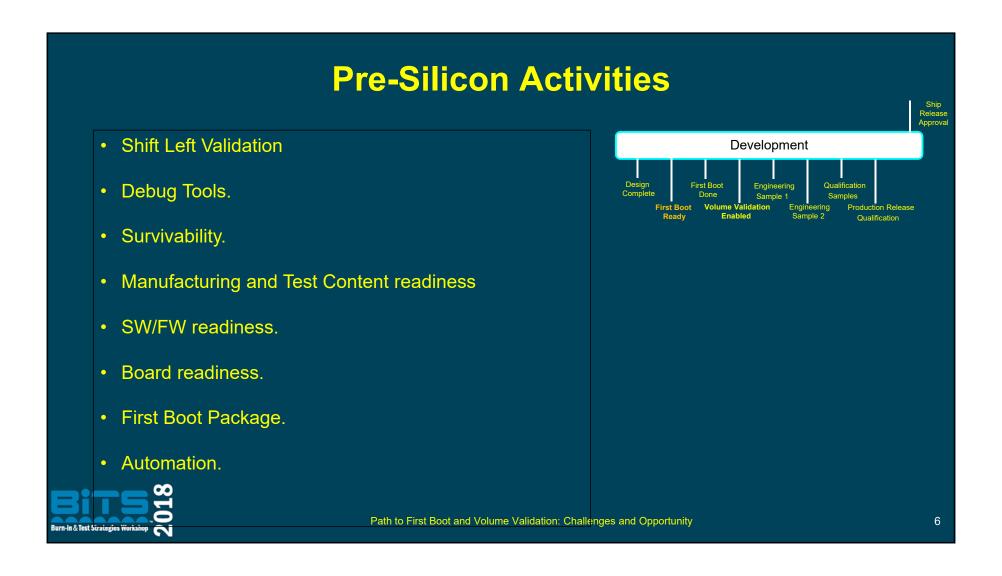

- Pre-Silicon Challenges and Opportunity.

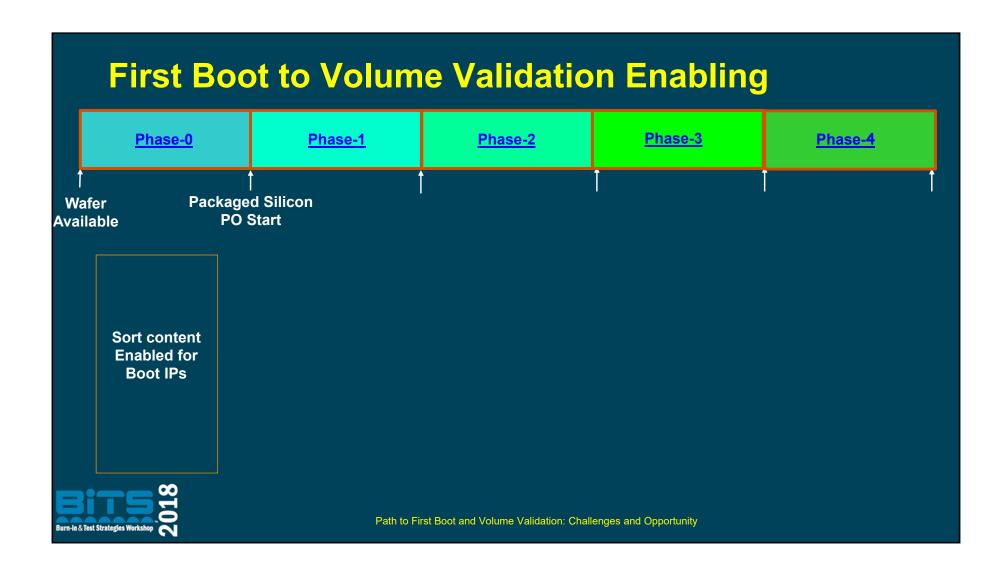

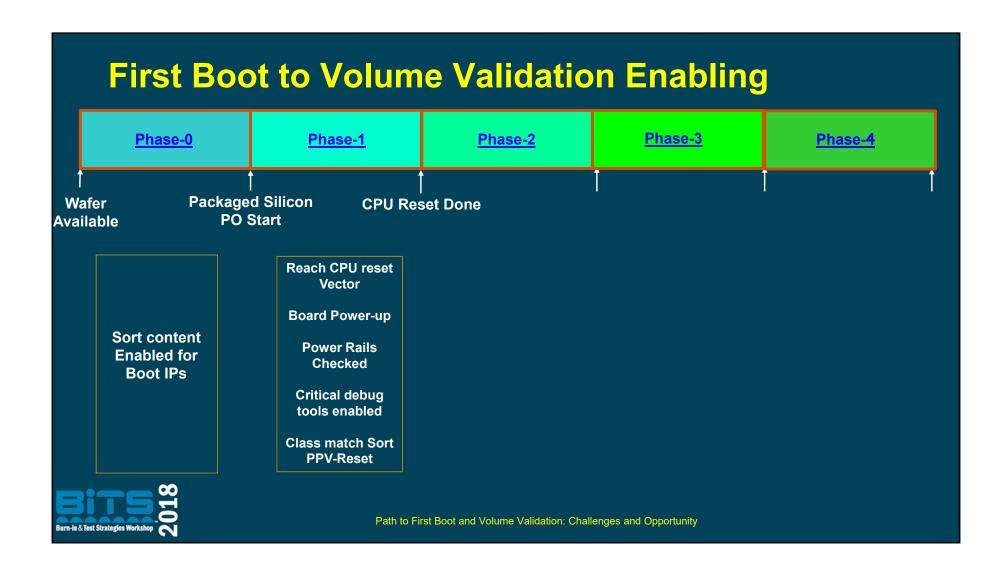

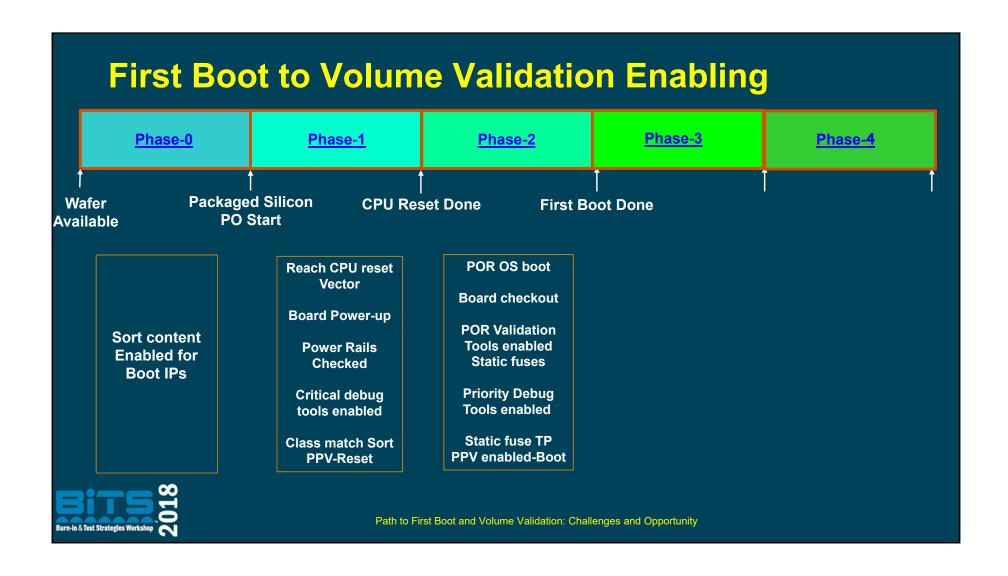

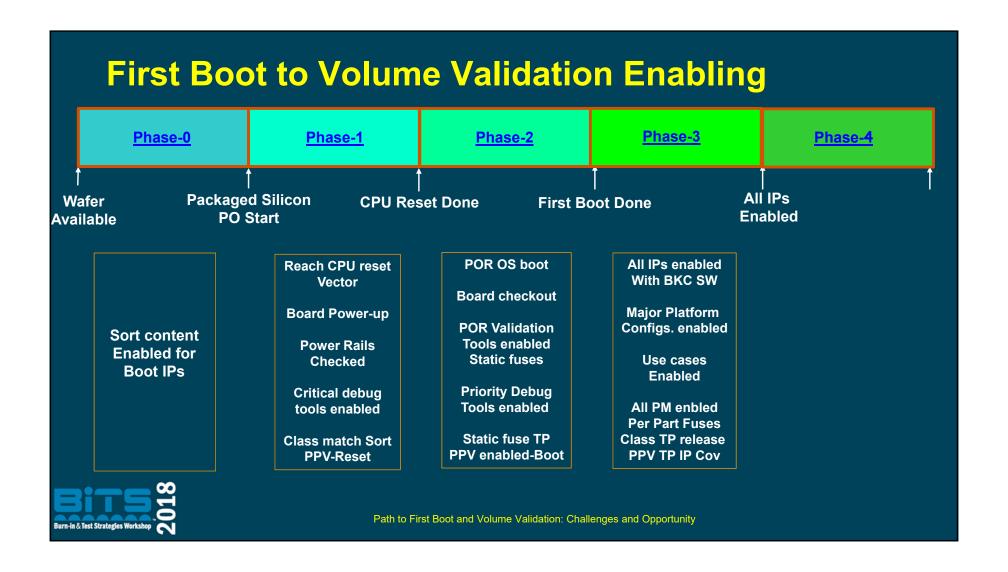

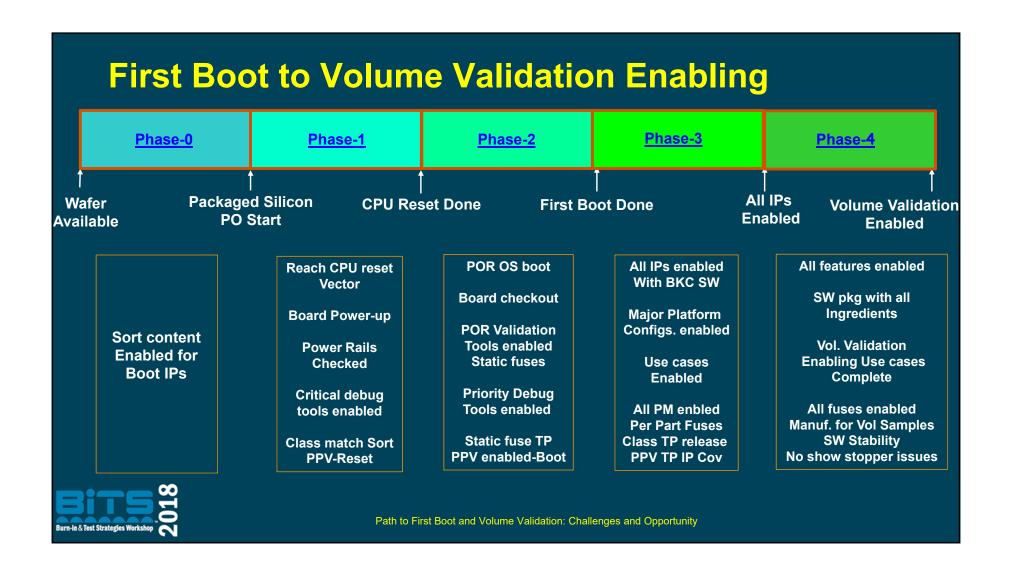

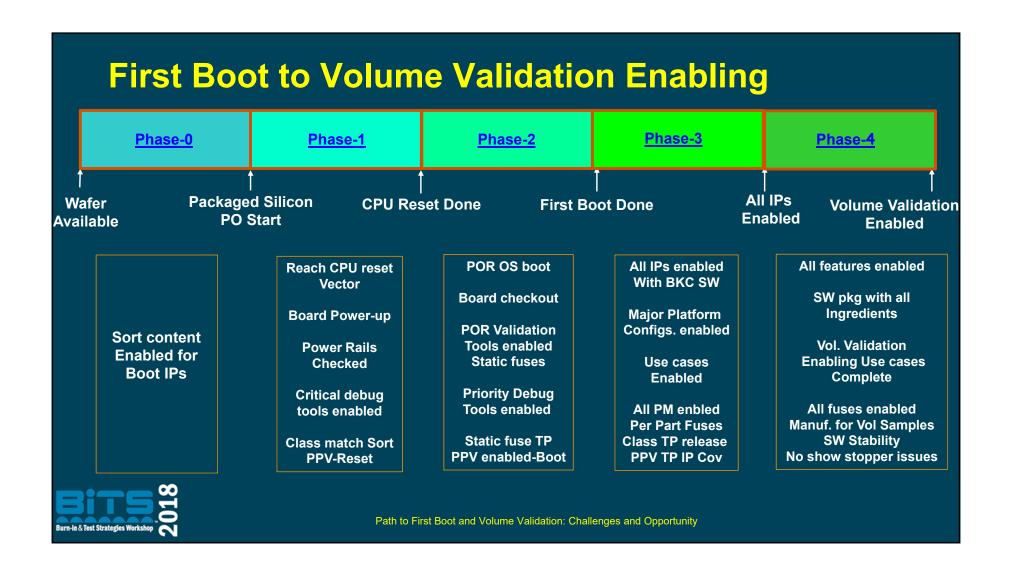

- First Boot and Volume Validation Enabling Stages.

- Post-Silicon Challenges and Opportunity.

- Call for Action.

#### **Importance of First Boot**

•Boot is most critical flow and gross indicator of silicon health.

•Unblocks validation.

Path to First Boot and Volume Validation: Challenges and Opportunity

4

#### **BiTS 2018**

Making Certain - Debug and Validation

#### Importance of Volume Validation Enabling

#### Volume Validation Enabling indicates

- •All features enabled.

- •Validation and Test Content enabled.

- •Silicon/Platform/Software/Firmware Ready for Volume Deployment.

- Volume Validation can start.

- •Can not be done without first boot done.

Path to First Boot and Volume Validation: Challenges and Opportunity

5

#### Post-Silicon Challenges and Opportunity ...

- Multiple variables plays simultaneously

- Health of the Validation Board.

- Unfused silicon.

- Enabling DFX features.

- Uncharacterized analog circuits/IOs.

#### Post-Silicon Challenges and Opportunity ..

- Part to Part variation.

- Silicon health without manufacturing screen.

- Identifying, Localizing, Root causing and Fixing problem.

- Using Survivability and DFX features to bypass issues.

- Enabling system level content in manufacturing screen.

Session 6

#### **BiTS 2018**

Making Certain - Debug and Validation

#### **Call For Action**

- Techniques for Faster root cause of a silicon bug.

- How to avoid re-spin of silicon to fix a problem.

- Resilient System Design.

Session 6 Presentation 1

#### **Disclaimer**

Intel technologies' features and benefits depend on system configuration and may require enabled hardware, software or service activation. Performance varies depending on system configuration. No computer system can be absolutely secure. Check with your system manufacturer or retailer or learn more at www.intel.com.

Intel, the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.