**Burn-in & Test Strategies Workshop**

March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

## Archive

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

## www.bitsworkshop.org

# Test Challenges Faced with System in Package

**Gerard John Amkor Technology, Inc.**

BiTS Workshop March 4-7, 2018

#### **Agenda**

- 1. System in Package (SiP) Introduction

- 2. Testing SiP Devices

- 3. Case Study: Testing 5G SiP Radio Module

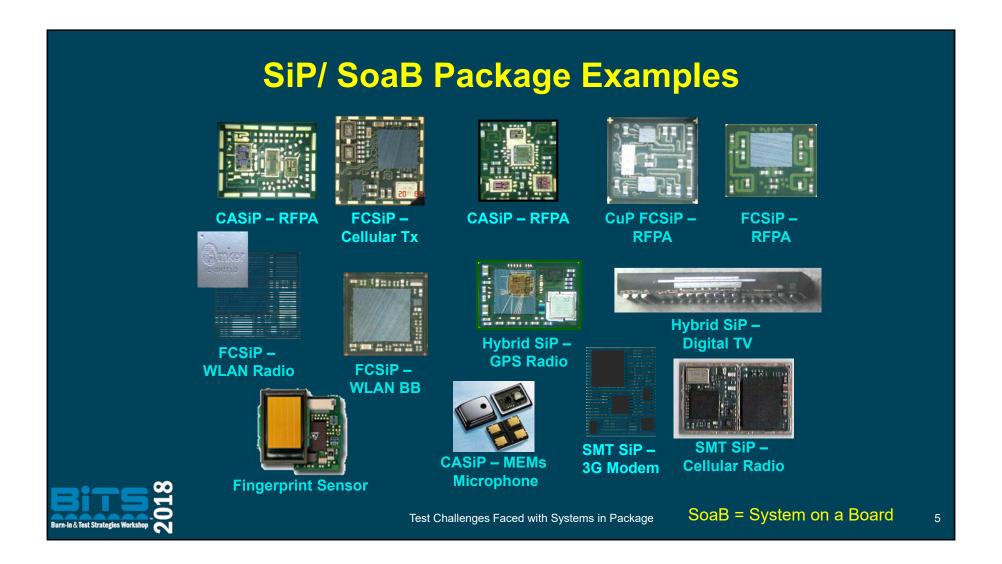

#### What is a System in Package (SiP)?

- Characterized by any combination of

- One or more ICs of different functionality

- May include passive components and/or MEMS sensors

- Spans multiple test expertise domains

- Hardware

- Analog/Mixed Signal, Digital, RF

- Software

- Firmware, Register Control, Device Drivers

- Assembled into a single package that performs as a system or sub-system

Test Challenges Faced with System in Package

#### **SiP/SoaB Reality**

- OSATs have the advantage of advanced assembly tools. By leveraging heterogenous integration they create the best systems in package

- OSATs have an extensive range of low cost test capabilities that can be applied to provide competitive solutions

- The few large, vertically integrated companies have an early advantage in terms of system design, architecture and DFT

## **Product Design/Perfect World**

- SiP ready EDA design & manufacturing tools

- Extensive DfT

- Die level, die-to-die and across system

- Redundancy, self repair and reconfiguration

- Easy physical test access

- Until then let's look at

- Existing test technologies

- Test strategies

- Industry gaps

#### **Design for Test**

- Cannot be an afterthought too late then

- Many SiP(s) are a collection of ICs without overall DfT

- Use a blend of individual chip test patterns, functional & system level test. Requires BIST structures

- Other practical physical design aids allow/plan for

- Test structures, test pads and sacrificial pads

- Reduced pin count (RPC) test modes for probe and strip test

- Keep out zones for contacting

#### Forming a Test Strategy

- Time to market?

- Data sheet will be guaranteed by:

- Design or characterization or production test

- Permissible defect level?

- Budgeted cost of test?

- Needs over product lifecycle?

- What actions will result from the testing?

Test Challenges Faced with Systems in Package

- T

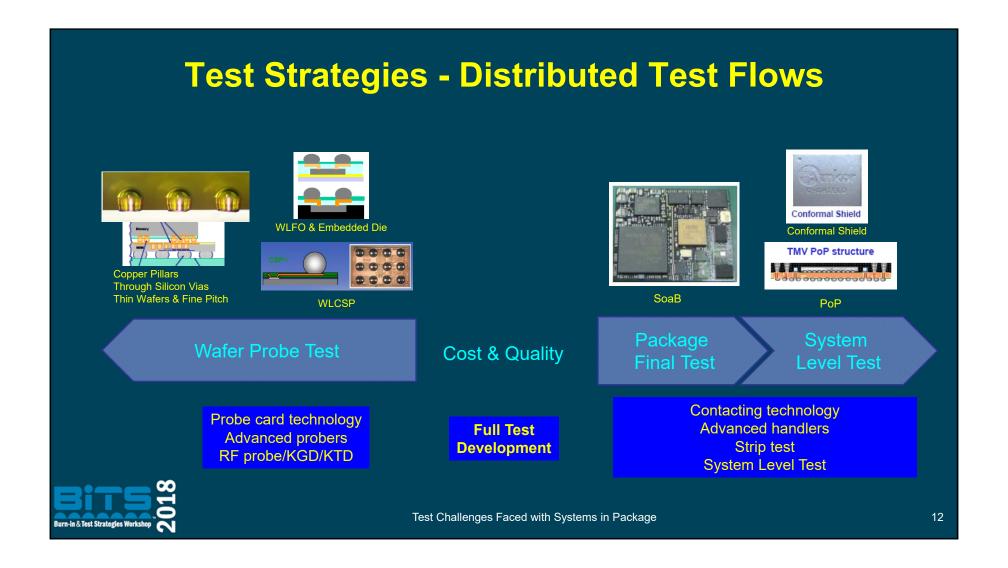

## **Multiple Test Insertion Points**

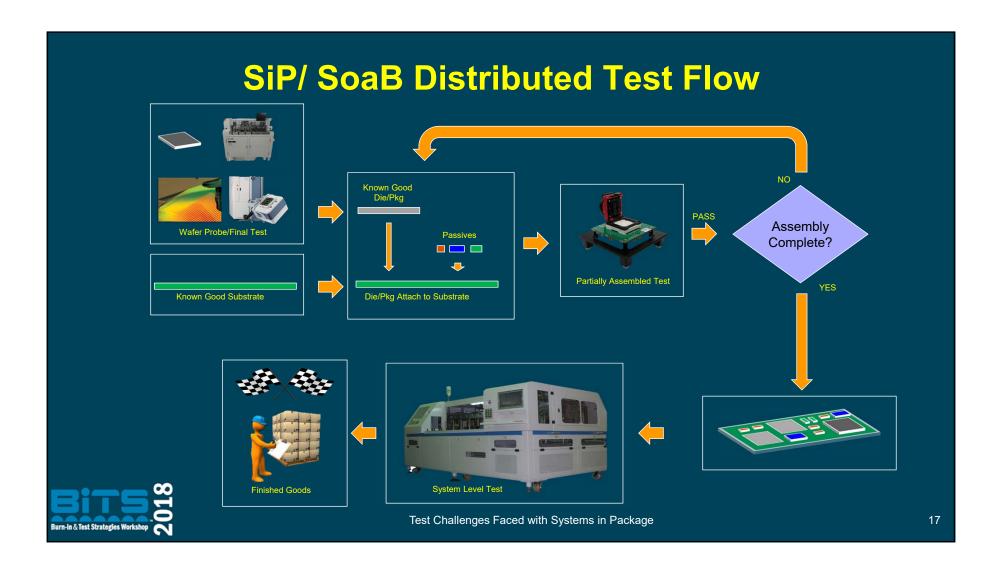

- Vital to have distributed test flows

- Fast feedback

- Scrap avoidance

- Protects the customer

- Over test, over characterize early on

- Phase out tests as DPPM levels drop

## **Key Points of SiP Test**

- Use appropriate, cost effective tester for the type of ICs

- RF probe when needed, technology is mature

- Testing myriad power management schemes

- Early over-testing

- Are the ICs mature and well characterized?

- Correlation to end product/application

- Final test trending to system level/one box test

- Cost! Cost!!! Cost!!!

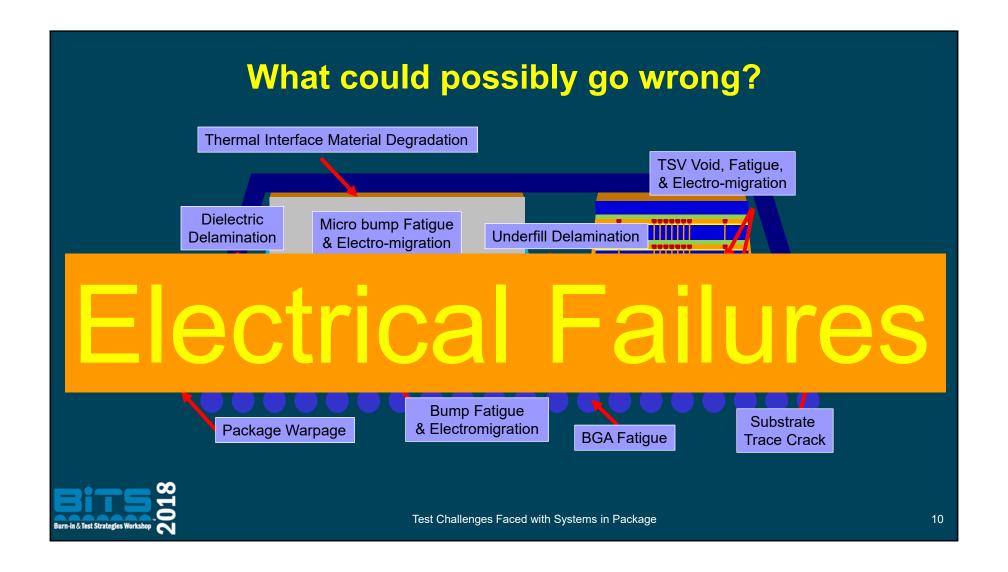

#### SiP w/TSV, SoaB Test considerations

- Check every single TSV?

- Impractical but a risk area

- Understand failure modes & mechanisms

- Sample & use variable test patterns within a lot

- Surface mount devices: PCOLA & SOQ

- Presence, correct value, orientation, live, alignment,

- Joints: Short, open, quality

- Understand the physics & causes of failure

- Need not use big iron ATE at all steps

Test Challenges Faced with Systems in Package

-18

#### **Contacting & Handling Considerations**

- Final test hardware

- Precise electrical contacting, thermal management

- Gentle handling that doesn't induce damage

- High volume sockets: long lifetimes, easily performed cleans & maintenance

- Smaller pad/bump sizes, tighter pitch

- 22 μm bump, 45 μm pitch

- At speed WS

- Sub-zero testing

Test Challenges Faced with Systems in Package

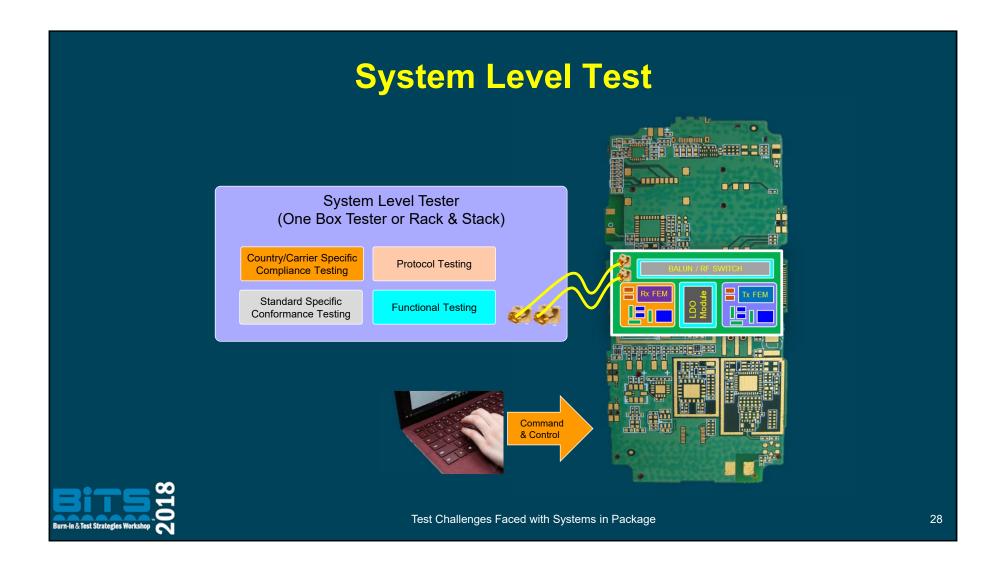

#### **Final Test Considerations**

- Apply right combination of tests

- Functional

- Map system level tests into ATE patterns

- Avoid complex "tester on load board" hardware

- Parametric

- System level

- If ICs in the SiP have already been ATE tested (\$\$\$)

- Don't spend more (\$\$\$) on ATE test if system level test (\$) can work

#### **Actions to take after Test?**

- Re-work very unlikely

- Scrap avoidance yes with PAT

- Huge opportunities for adaptive test

- On the fly test program adaptation

- Feed forward data downstream decisions

- Feed back data correlate/improve earlier tests, designs

- 2D barcode and traceability

- Link test, bill of materials, machine/manufacturing data

Test Challenges Faced with Systems in Package

#### **Low Cost System Level Test**

- System level test need not be manual load / x1

- One can take advantage of pick and place handlers

- SiP automated system level tester placed under a pick and place robotic handler: M-WeST

- Four 802.11 OBT integrated with handler & Station controller

Test Challenges Faced with Systems in Package

## **SiP Test State of the Art & Approaches**

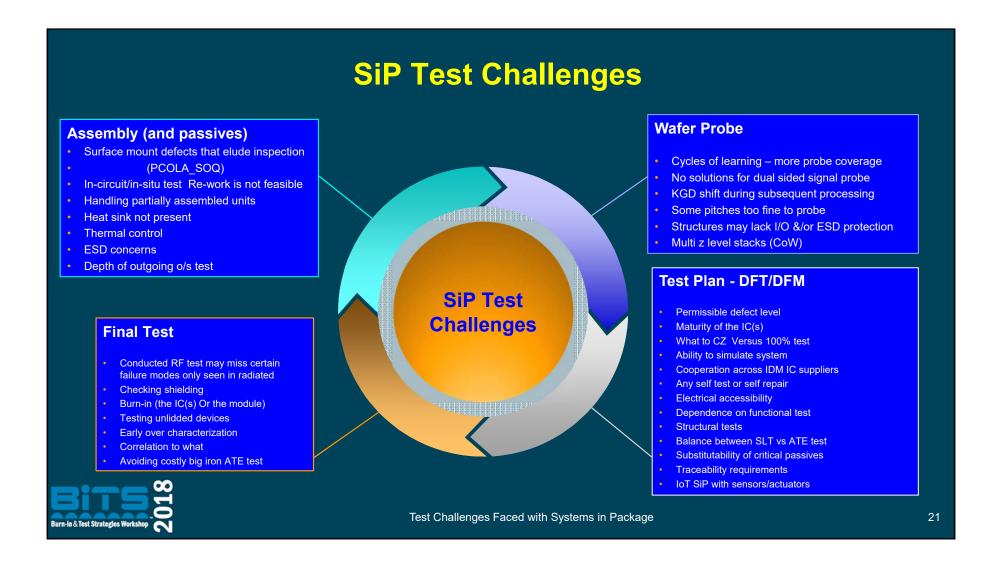

#### **Assembly (and passives)**

- Use in-situ distributed test flow at key points for scrap avoidance (don't add more value to the module if already defective)

- Use handler active thermal control as needed if the heat sink(s) are not present yet

- Analysis of what belongs in outgoing o/s test versus what belongs in final test

#### **Final Test**

- Unlidded devices involve socket & handler makers

- Continuous feedback to assembly and probe

- Adaptive test & feed forward, feed back

- Correlation to what

- Avoiding costly big iron ATE test

- SLT start LVM on standard handlers, can map a path to semi-custom massively parallel SLT handlers

#### **Wafer Probe**

- Dual height (2 level) probe cards available for CoW

- Pick the appropriate ATE tester (RF, MS, memory)

- Aim for KGD, beyond KTD

- Use of RF probe, use of direct dock

- Move cold test from FT to probe

- Get feedback from final test and continually improve probe coverage

- Leverage adaptive test & feed forward, feed back

#### **Test Plan - DFT/DFM**

- Plan for early over characterization

- Extra room add test access!

- Do a test FMEA of the BoM

- Cost model the SLT vs. ATE tradeoffs

- CZ & Qual multiple suppliers of critical passives

- Leverage 2D codes for traceability

- Stimulus test for IoT with sensors/actuators

Test Challenges Faced with Systems in Package

| SiP Test – by Module Type                              |                                                            |                                                                |                                                  |                                                                      |

|--------------------------------------------------------|------------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------------------------|

|                                                        | Wafer Probe for SiP                                        | PAT                                                            | SiP Final Test ATE                               | SiP Final Test SLT                                                   |

| Radio<br>(PA, Xcvr, FEM, FES)                          | ATE<br>RF KGD direct dock                                  | Sub-Modules                                                    | Custom or<br>Commercial<br>Rack n Stack          | Have seen sampling before using R&S or Agilent base station emulator |

| Sensory<br>(Biometric, Si microphones)                 | Typically at IDM fab                                       | Uncommon                                                       | Stimulus + Simple<br>ATE                         | Custom by application/customer                                       |

| Companion<br>(WLAN, WiMax, GPS, TV)                    | RF ATE                                                     | Uncommon for simple modules                                    | Skipped                                          | One box testers                                                      |

| Automotive<br>(Infotainment, ECU, Sensors/Actuators)   | Cold probe to avoid tri temp final test                    | Some frequency for scrap avoidance                             | Most complex<br>modules get no ATE<br>final test | Customer board                                                       |

| Baseband<br>(Digital, Memory, PMU, Audio, Digital+RFA) | Cold probe, direct dock<br>Two level probe card<br>(CoCoW) | More common –<br>hdgh end GPU - for<br>scrap avoidance.<br>ATC | MS/SoC<br>PMU<br>Memory                          | Asynchronous handlers                                                |

|                                                        |                                                            |                                                                |                                                  |                                                                      |

Session 3A Presentation 3

Section 3

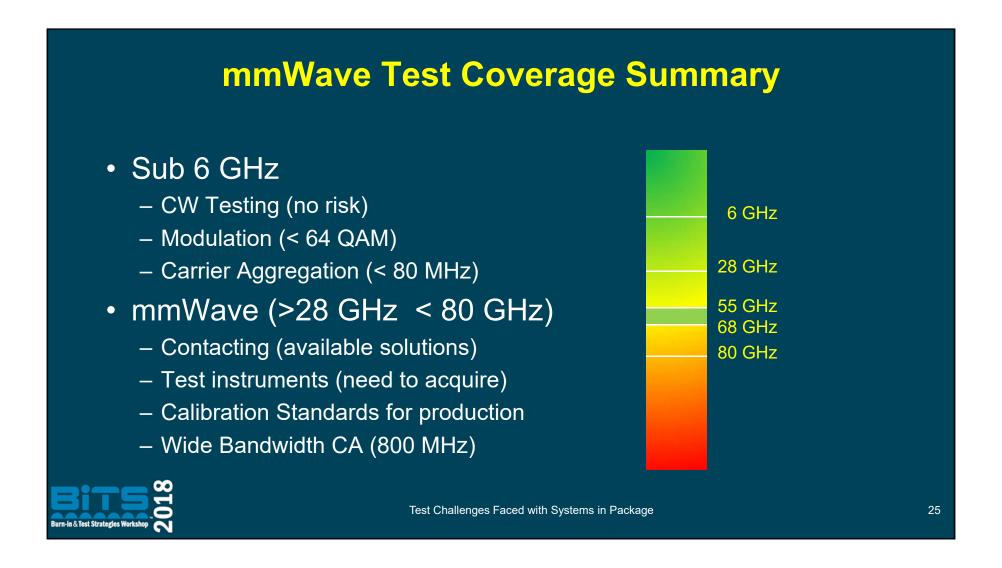

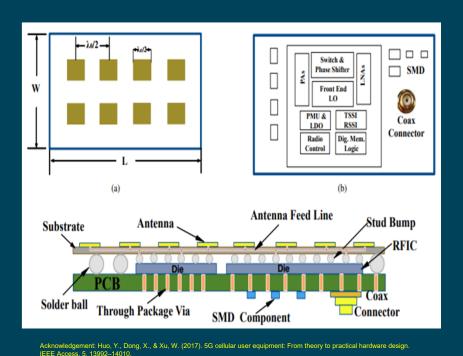

## **CASE STUDY – TESTING 5G SIP RADIO**

Test Challenges Faced with Systems in Package

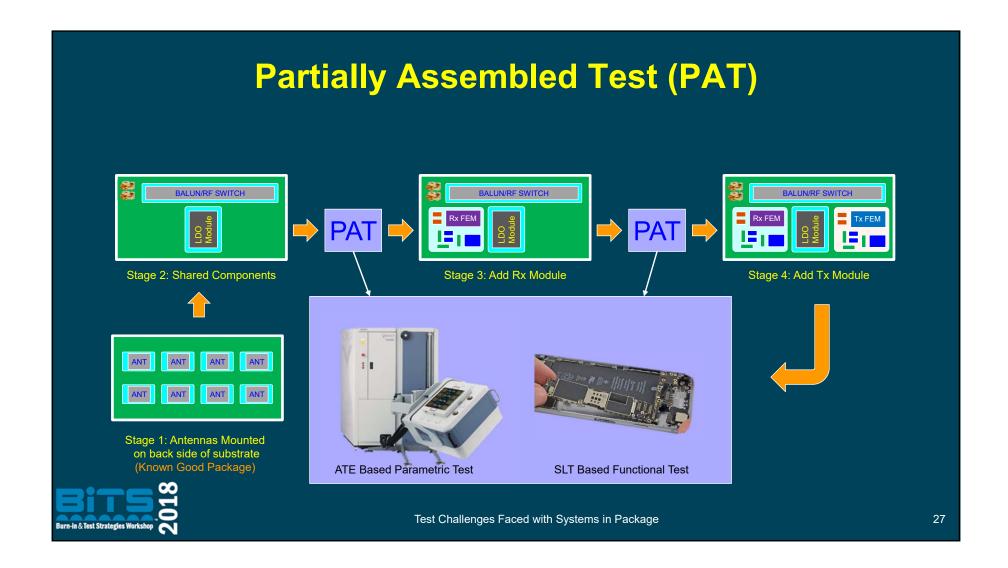

## **Testing 5G Hypothetical Radio Module**

- All individual components are tested before assembly

- Antenna assembly is built and tested before die/package attach

- Partially Assembled Test (PAT) of the module is performed as system is being built

Test Challenges Faced with Systems in Package

26

#### **Conclusion**

From the outside System

Level Test gives the

impression that is built up of

the same set of pieces.

However, system level testing

for SiP or SoaB products

require solutions that are as

unique as the product line.

https://play.google.com/store/apps/details?id=com.appgame7.jigsaw.free

Test Challenges Faced with Systems in Package