# NINETEENTH ANNUAL Burn-in & Test Strategies Workshop

## March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Session 3A Presentation 2

Really? - System Level Test

**Burn-in & Test Strategies Workshop**

Really? - System Level Test

#### Agenda

- What is System-Level Test (SLT)?

- How is SLT done today?

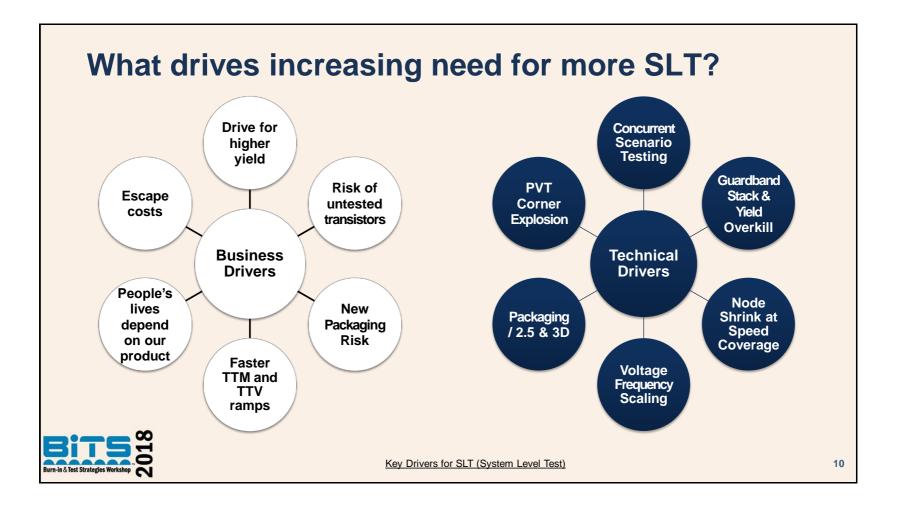

- What are the trends driving need for more SLT?

- What are the key challenges and opportunities?

Key Drivers for SLT (System Level Test)

Really? - System Level Test

### What is System-Level Test (SLT)?

- Application-specific functional tests that are performed

- on an IC Device Under Test (DUT)

- which is temporarily placed in a socket while SLT tests are applied

- to help "guarantee" that a device will meet its targeted specs and performance goals when it is ultimately used in the final system.

#### System includes both hardware and software

- Hardware Device Under Test (DUT), sockets, application boards, power supplies, etc.

- Software firmware, device drivers, operating systems, applications, etc.

#### System-Level Test ensures that the device is tested similar to the end user experience

#### Key Drivers for SLT (System Level Test)

Really? - System Level Test

#### What is System-Level Test (SLT)?

#### • 2 perspectives ... component vs system

- Component perspective does the device meet its specs?

- System perspective does the "system" work when all the DUTs are combined with software at the board level?

#### System-Level Test ensures that the device is tested similar to the end user experience

Key Drivers for SLT (System Level Test)

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

Really? - System Level Test

**Burn-in & Test Strategies Workshop**

Really? - System Level Test

Really? - System Level Test

Burn-in & Test Strategies Workshop

Session 3A Presentation 2

Really? - System Level Test

**Burn-in & Test Strategies Workshop**

Really? - System Level Test

#### Agenda

- What is System-Level Test (SLT)?

- How is SLT done today?

- What are the trends driving need for more SLT?

- What are the key challenges and opportunities?

Key Drivers for SLT (System Level Test)

Session 3A Presentation 2

Really? - System Level Test

**Bits 2018**

Really? - System Level Test

Session 3A Presentation 2

Really? - System Level Test

**Burn-in & Test Strategies Workshop**

Really? - System Level Test

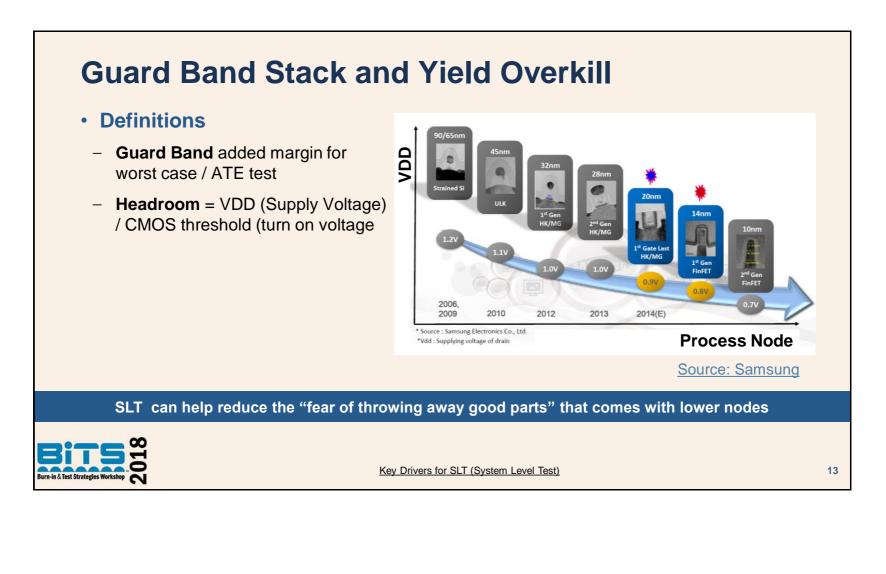

#### **Guard Band Stack and Yield Overkill**

With lower nodes, Guard Band becomes a higher percentage of VDD, "eating into the headroom"

| Technology<br>Node<br>(nm) | Vdd<br>(V) | 100 mV<br>Guardband as a<br>% of Vdd | CMOS<br>Threshold<br>(V) | Headroom<br>Vdd- Threshold<br>(V) | 100mV<br>Guardband as<br>% of headroom |

|----------------------------|------------|--------------------------------------|--------------------------|-----------------------------------|----------------------------------------|

| 90                         | 1.4        | 7.1%                                 | 0.5                      | 0.9                               | 11.1%                                  |

| 65                         | 1.2        | 8.3%                                 | 0.5                      | 0.7                               | 14.3%                                  |

| 45                         | 1.1        | 9.1%                                 | 0.5                      | 0.6                               | 16.7%                                  |

| 28                         | 1          | 10.0%                                | 0.5                      | 0.5                               | 20.0%                                  |

| 20                         | 0.9        | 11.1%                                | 0.45                     | 0.45                              | 22.2%                                  |

| 14                         | 0.8        | 12.5%                                | 0.4                      | 0.4                               | 25.0%                                  |

| 10                         | 0.7        | 14.3%                                | 0.4                      | 0.3                               | 33.3%                                  |

Assume: 100mV Guard Band (could also be ~100MHz Guard Band)

SLT can help reduce the "fear of throwing away good parts" that comes with lower nodes

Key Drivers for SLT (System Level Test)

Really? - System Level Test

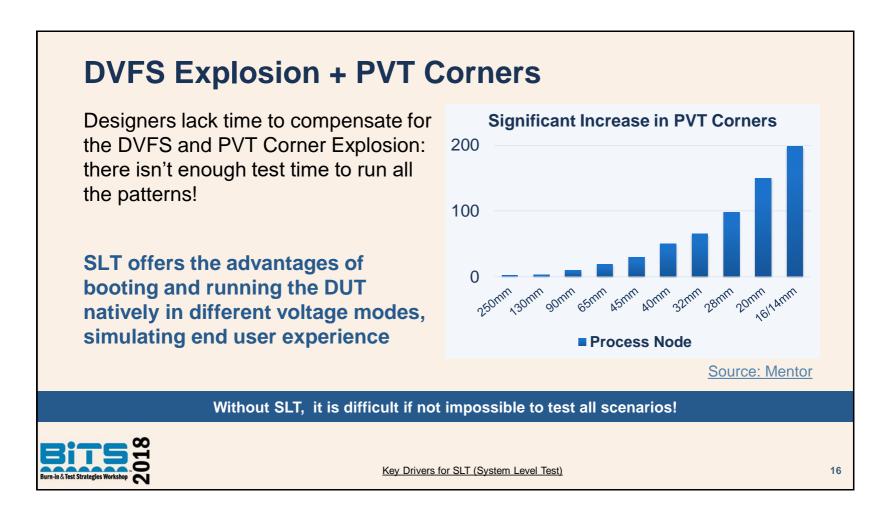

#### **DVFS Explosion + PVT Corners** Dynamic Voltage Frequency Scaling (DVFS) Nominal Ensures the DUT works at different Mode power conditions by simulation and Frequency testing of each power situation **Hi-speed** Process Voltage Temperature Mode (PVT) Corners Sleep Mode Addresses process and temperature variations with simulation and testing Voltage Without SLT, it is difficult if not impossible to test all scenarios! Key Drivers for SLT (System Level Test) 15 urn-in & Test Strategies Works

**Burn-in & Test Strategies Workshop**

**Burn-in & Test Strategies Workshop**

Really? - System Level Test

#### **Conventional Test Methods No Longer Catch Fails**

Source

Silicon Substrate

Oxid

**FinFET Cross Section**

Source: Cadence

Wire-bonding

**3D process geometries** are driving new defect types that aren't covered by static ATPG\*, at speed ATPG (TDF\*\*), and other test methods

**IPs from different vendors**: coverage was easier with one IP.

High speed, bidirectional interfaces have faster read/write turnaround times than the latency of ATE

\*ATPG – Automatic test pattern generation for structural test

#### System-Level Test screens for these fail mechanisms

Key Drivers for SLT (System Level Test)

17

TSV

**Discrete Passives**

SiP Module Cross Section Source: ASE Group

Conformal Shieding

Elin Chin

Die Stacking

4~6 layers laminate substrate

#### **Challenges and Opportunities**

#### Challenges

- Lack of fault coverage metric to assess

SLT effectiveness

- Complex nature of System-Level Test Failures makes it difficult to diagnose root cause of failures

- SLT Equipment Challenges

- No "one size fits all"

- Correlation between SLT and ATE

- Cost to add SLT

- Limited throughput

- Large form factors

- Being Addressed with Massively Parallel SLT

#### **Opportunities**

- More systematic approaches to create "commonality"

- Ecosystem of standards, tools, and equipment for efficient SLT flow

- Close the loop with Data Analytics

Key Drivers for SLT (System Level Test)

Burn-in & Test Strategies Workshop

Really? - System Level Test

Burn-in & Test Strategies Workshop