# NINETEENTH ANNUAL Burn-in & Test Strategies Workshop

#### March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Session 3A Presentation 1

Really? - System Level Test

# Challenges for accurate platform power measurement

#### Bernard Tam, Estanislao Aguayo, Aymen Abdo and Christopher Kinney Intel Manufacturing Validation Engineering

BiTS Workshop March 4 - 7, 2018

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 4-7, 2018

Session 3A Presentation 1

Really? - System Level Test

#### **Contents**

- Problem statement

- Current sense resistor calibration

- Current sense resistor placement (separating platform power from motherboard power); optimized placement can minimize IR drop

- Software (benchmark) dependency on power measurement accuracy

- Temperature (close to Tj max.) of measurement

- Routing of current sense planes (voltage drop)

Challenges for accurate platform power measurement

Session 3A Presentation 1

Really? - System Level Test

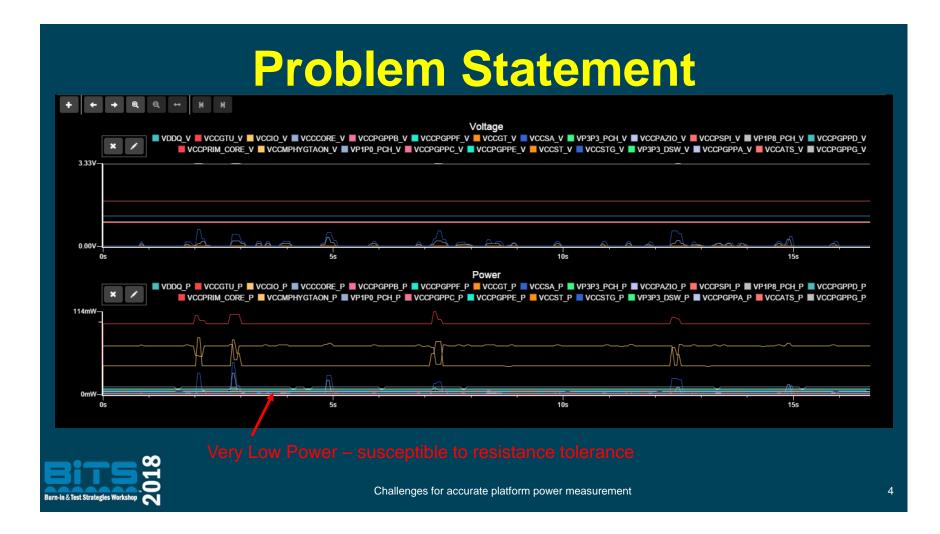

## **Problem Statement**

Accurate (1%) power measurement of complex circuit systems, operating in a dynamic environment (changes in µs) with 10's of voltage rails, in order to make accurate battery life estimation and enabling a more accurate binning of parts.

Challenges for accurate platform power measurement

Really? - System Level Test

**Burn-in & Test Strategies Workshop**

Session 3A Presentation 1

Really? - System Level Test

#### **Problem Statement**

- $P = I^2 * R$

- Ptot = Prail1 + Prail2 ...

- If P is to be measured with a 1% accuracy, first we need to make sure that the R is known to be around 0.1% accuracy for ten power rails.

- Calibration both the current sensing resistors (CSR) and data acquisition (DAQ) together will compensate the offset at the input of the instrumentation amplifier.

Challenges for accurate platform power measurement

Session 3A Presentation 1

#### Really? - System Level Test

#### **Problem Statement**

- We can reduce the errors of the power measurements by ensuring current sensing resistors have the least tolerances and most stable (thermal and electrical)

- Typical resistor tolerance (±1%)

- Topology placement, fabrication and assembly tolerance and variation

- Typical thermal drift (± 200 ppm/°C)

- »More difficult

- »Requires temperature measurement in addition

**Bits 2018**

Really? - System Level Test

# **Resistors everywhere**

- Current sensing resistors induce a voltage drop → need to keep that to a minimum

- Board routing of the plane will also introduce a resistance.

- These current sense resistors are cumbersome to place and route and take real estate on the board

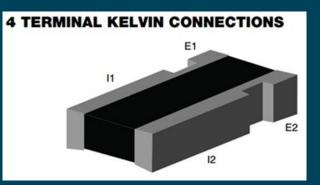

- We use 4-terminal current sensing resistors with Kelvin sense to reduce IR drops for better precisions.

Challenges for accurate platform power measurement

Session 3A Presentation 1

Really? - System Level Test

# **Current sense resistors**

2-Terminal Current Sense Resistors Sense points close to resist material Low-current high-resistor value (≥ 20 mΩ typical) Low package size (e.g. 0603) and low power dissipation <u>4-Terminal Current Sense Resistors</u> Sense points at resist material High-current low-resistor value (≤ 20 mΩ typical)

Wide reverse geometry (e.g. 0612) for power dissipation

Session 3A Presentation 1

Really? - System Level Test

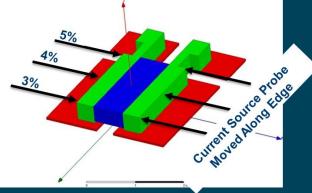

# **Current sense resistors**

Measured sense point voltage *depends* on current source probe location

- Measured Variation = 3-5%

- (60-100  $\mu\Omega$  variation on 2 m $\Omega$  CSR)

Challenges for accurate platform power measurement

Session 3A Presentation 1

Really? - System Level Test

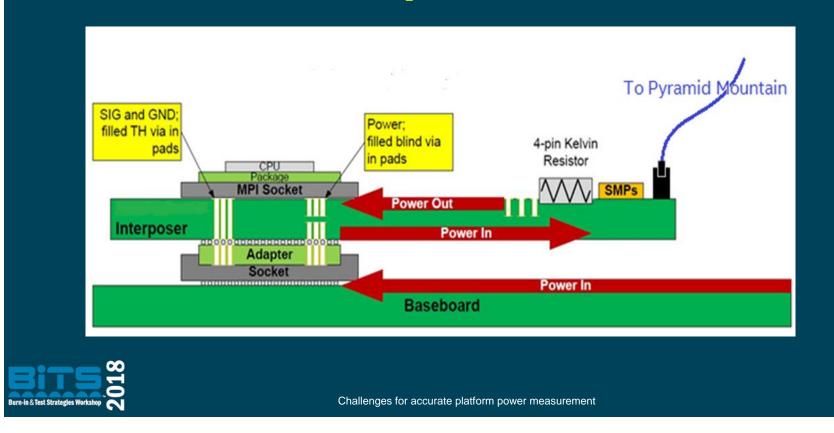

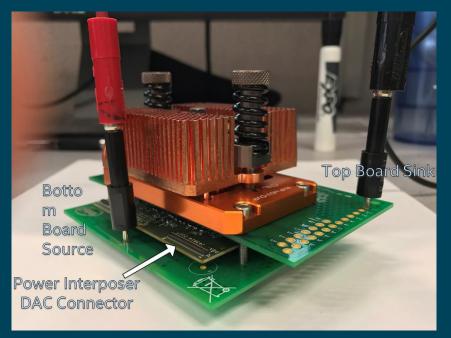

#### **Power interposer solution**

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

Session 3A Presentation 1

Really? - System Level Test

# **Power interposer solution**

Challenges for accurate platform power measurement

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 4-7, 2018

#### **Bits 2018**

Session 3A Presentation 1

Really? - System Level Test

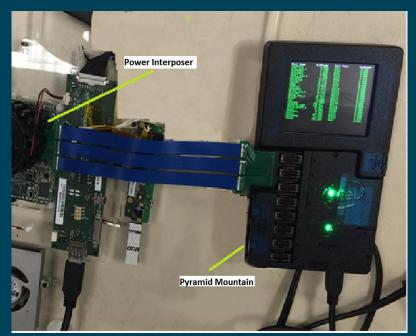

## **Power interposer solution**

Pyramid Mountain is a low-cost, highly configurable data acquisition system intended to interface between PHG power interposers and host-based software such as Powerhouse Mountain (not yet released).

It continually scans the kelvin resistors on the power interposer and reports the current, voltage and calculated power readings in real time

Challenges for accurate platform power measurement

**Burn-in & Test Strategies Workshop**

# Power interposer pros and cons

#### Pros:

- No need to accommodate current sense resistors on motherboard

- Current sense resistors close to platform

- Can be adapted to any board that uses the target platform (Mainly need mechanical holes to hold it)

- Can be calibrated unit per unit for maximum accuracy

#### Cons:

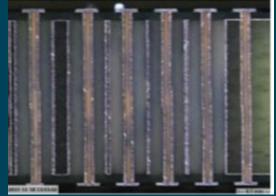

- Hard to design (14 layer microvia, with very tight spacing ~2 mils)

- Need custom retention hardware

- Assembly of interposer onto motherboard challenging

#### **Bits 2018**

Really? - System Level Test

# **Power interposer pros and cons**

- Interposer introduces a discontinuity in the signal path, for every signal path, not just power

- Can be a problem for high speed lines (PCI,DDR...) running at GHz speeds

- The coax via solves this situation, providing a shielded environment in the added length of the trace.

Session 3A Presentation 1

Really? - System Level Test

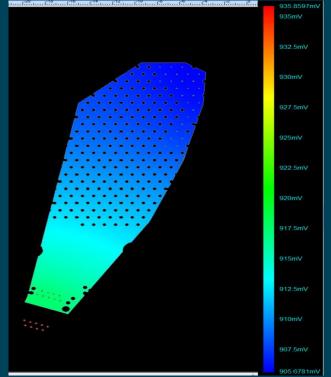

#### Power interposer pros and cons

- Power plane routings on power interposer create significant IR drop for lower voltage/high current rails.

- Special care is needed for power plane layout designs.

Challenges for accurate platform power measurement

Burn-in & Test Strategies Workshop

#### **Bits 2018**

Really? - System Level Test

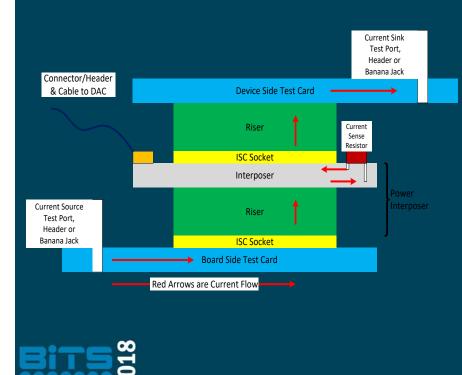

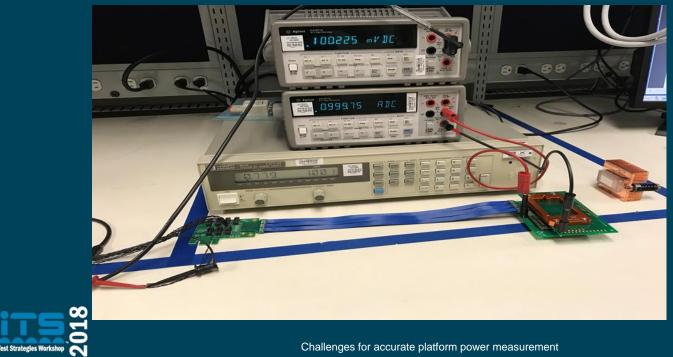

# **Calibrating the power interposer**

Apply known reference current through interposer power pins

- 1. Platform source currents are provided through substitute bottom board (blue)

- 2. Device/CPU/PCH/SoC package sink currents are provided through substitute top board (blue)

- 3. Sense terminal measurements identical to platform measurements

Session 3A Presentation 1

Really? - System Level Test

# **Calibrating the power interposer**

Challenges for accurate platform power measurement

Burn-in & Test Strategies Workshop

Session 3A Presentation 1

Really? - System Level Test

# **Calibrating the power interposer**

-Precision calibration of current sense resistors: demo set-up

Burn-in & Test Strategies Workshop

Really? - System Level Test

#### **Calibrating the power interposer**

| Resistor<br>(Ω) | Rating<br>(W) | lmax<br>(A) | Imeas<br>(A) | Vmeas<br>(mV) | R (Ω)    | Error (Ω) |

|-----------------|---------------|-------------|--------------|---------------|----------|-----------|

| 0.2             | 1/8           | 0.79        | 0.5023       | 100.945       | 0.200965 | 0.0003    |

| 0.01            | 1/8           | 3.54        | 2.9988       | 30.064        | 0.010025 | 0.000014  |

| 0.05            | 1/8           | 1.58        | 0.9996       | 50.213        | 0.050233 | 0.00007   |

| 0.022           | 1/8           | 2.38        | 1.9993       | 44.089        | 0.022052 | 0.00003   |

|                 |               |             |              |               |          |           |

Challenges for accurate platform power measurement

Session 3A Presentation 1

Really? - System Level Test

# Conclusions

- Power interposer solution allows for accurate power measurement

- Measurements can be done in the customer board

- Challenges with this technology have been identified

- Assembly of interposer

- PCB fabrication

- Signal integrity

- Component accuracy (current sense resistor)

Session 3A Presentation 1

Really? - System Level Test

#### **Future work**

- Improve precision and bandwidth of power measurements

- Frequency measurements instead of voltage measurements

- 1 ms gate for frequency measurement

- Collpitts oscillator with CSR providing frequency setting voltage

- Simplify mechanical requirements for this solution

- Thermal head conflicts with board need to be addressed

- Temperature profile in the board might bring CSR out of calibration

- Fine tune the assembly of the interposer

**Bits 2018**

Challenges for accurate platform power measurement

Session 3A Presentation 1

Really? - System Level Test

# Acknowledgements

Estanislao Aguayo, Ayman Abdo, Christopher Kinney, Tu Cao and Mike Chombeau, Emir Mesanovic, Hayley Klug, and Stuart Burman

"New Possibility with Coax Via Risers" Matthew Priolo et al. BiTS 2017

"Current Gradients in Power Delivery" Christopher Kinney et al. DesignCon 2017

"PCB Via Technology Limitations & Optimization" Vothy Heang et al. BiTS 2018

Challenges for accurate platform power measurement

22

**Burn-in & Test Strategies Workshop**