# NINETEENTH ANNUAL Burn-in & Test Strategies Workshop

## March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

Archive

# **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

# www.bitsworkshop.org

## **BiTS 2018**

#### Coaxial IC Socket for PAM4 & High Power Specification Requirement

Tatsumi Watabe, Makoto Kawamura, Hiroyuki Yamakoshi

#### Abstract

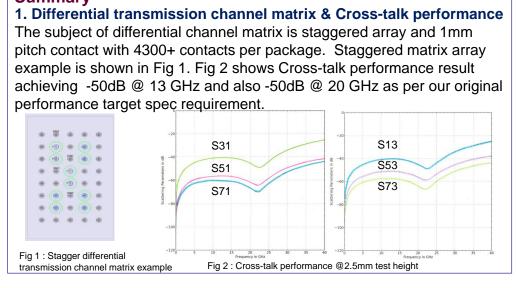

Significant signal integrity improvement is required for IC socket in application of Gbps transmission and receiving IC. PAM "Pulse Amplitude Modulation" especially PAM4 : 52 Gbps transmission performance is configured with base band : 13 GHz, and differential signal transmission channel. For system performance achievement with signal integrity, the IC socket must keep up its own specification for Cross-talk performance between channel to channel under -50dB by signal transmission of PAM4 (52 Gbps). LSI Circuit needs large number of differential SerDes channel resulting in huge power consumption such as 400 watts or over per IC package. The IC socket has been given two different duties to solve all at once. The solution was simple, return to engineering base. And answers were "keep transmission line Zo =  $50 \Omega$  without signal leakage" and "keep pure thermal transfer path on the top of IC package".

#### Summary

#### 2. Base socket height design vs 1/4 wave length at 52 Gbps

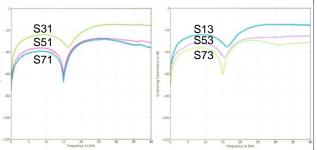

Due to 13 GHz base band frequency, performance verification was extended up to 20 GHz for design allowance. The wave length corresponding to transmission line in base socket is 15.0 mm. 1/4 wave length is 3.75 mm at 20 GHz. In case of 52 Gbps, base band is 26 GHz. 30 GHz is chosen for design allowance. Wavelength is 10 mm, and 1/4 wave length is 2.5 mm. Based on this reason, transmission line length in IC socket (test height) was decided to be 2.5 mm.

Fig 3 is Cross-talk performance of 3.8 mm transmission line length by same design concept for IC socket, but cross talk performance was -30dB @ 20 GHz. Result did not meet the requirement.

Fig 3 : Cross-talk performance @3.8mm test height

### **3.** Characteristic impedance control for transmission line in IC socket base

Signal contact probe and connection must be pure transmission line as  $Zo = 50 \Omega$ . So, complete coaxial contact technology was chosen, and transmission connection was from surface pad of mother board to IC terminal. Probe and coaxial line ground hole was designed simply as  $Zo=138*\log(D/d)/\sqrt{\epsilon}$ , which means coaxial line everywhere in socket.

## 4. Full speed transmission signal process causes large power consumption in LSI

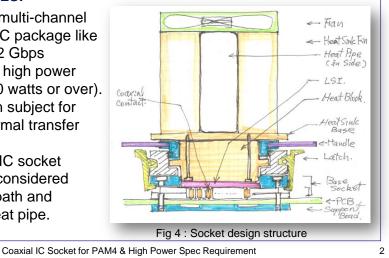

High speed and multi-channel SerDes function IC package like 65x65 mm and 52 Gbps operation causes high power consumption (400 watts or over). One of the design subject for this socket is thermal transfer and Tj control.

Fig 4 is High Pd IC socket design structure considered thermal transfer path and heatsink using heat pipe.

**BiTS 2018**

## **Bits 2018**

The socket was designed with handle operation cap, and thermal block (Cu) in the cap is on top of the package surface. Heat sink with fan has been set on top of the thermal block. Thermal resistance (conductivity) of thermal block must be calculated by (1)  $\theta ch = Block height (m)/Area (m)/Material thermal conductivity(W/m K).$ Thermal equation must be  $(2)Tj = Pd^{*}\theta ja + Ta = Pd^{*}(\theta jc + \theta ch + \theta ha) + Ta$ Here, Tj : Junction temperature of IC, may set to 110 °C Pd : Power dissipation of IC, 400 watts θja : Thermal resistance from junction to air, 0.1913 °C/W θjc : Thermal resistance from junction to case, 0.055 °C/W θch : Thermal resistance of thermal block, 0.021318 °C/W θha : Thermal resistance of heatsink and fan, 0.115 °C/W Ta : Ambient temperature(air) 30 °C Tj(110°C)>Pd(400)\*(θjc(0.055)+θch(0.0213)+θha(0.115))+Ta(30)=106.5 °C 5. Fig 5 is simulation confirmation Overheating confirmation for thermal transformation of 400 watts verified by Tj. Tj=107.3 °C is in the border safety line (assumption of 110 °C junction temperature). Max = 107.348 \*0 Fig 5 Temperature simulation 6. Fig 6 is for example of IC socket IC Package : 67.5 x 67.5 mm, 4,356 balls, Differential pair channel 132 IC Socket : 124 x 120 mm, Handle cap operation with 400 watts IC Fig 6 : Design example Conclusion Transmission line be 1/4 waveform length and complete coaxial Zo line for no signal leakage in connector are key factors to reach best Cross-talk performance for PAM signal transformation. For PAM4 results shown -50dB at 13 GHz, 52 Gbps or over. Thermal control for very high power dissipation IC due to high speed and large number of multichannel transmission must be solved by careful design of thermal transfer path using best thermal conductivity and heatsink system design by heat pipe or similar application.

BiTS 2018

Coaxial IC Socket for PAM4 & High Power Spec Requirement

3