**Burn-in & Test Strategies Workshop**

March 4 - 7, 2018

Hilton Phoenix / Mesa Hotel Mesa, Arizona

# Archive

#### **COPYRIGHT NOTICE**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2018 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2018 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2018 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

# www.bitsworkshop.org

# Marketplace Report Challenges of Today & Tomorrow

Ira Feldman Feldman Engineering Corp.

BiTS Workshop March 4 - 7, 2018

#### **Overview**

- Today's Challenges

- Non-electrical

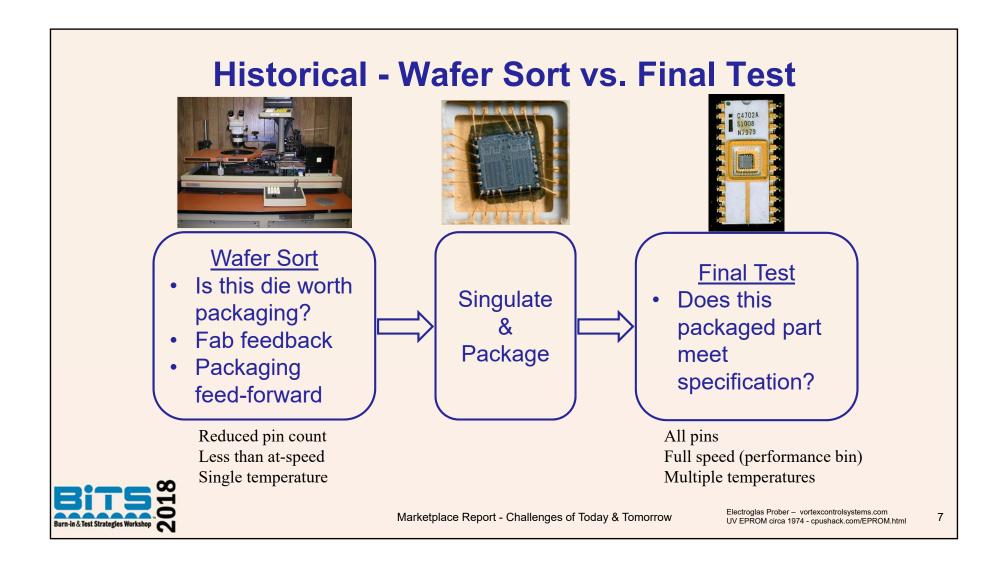

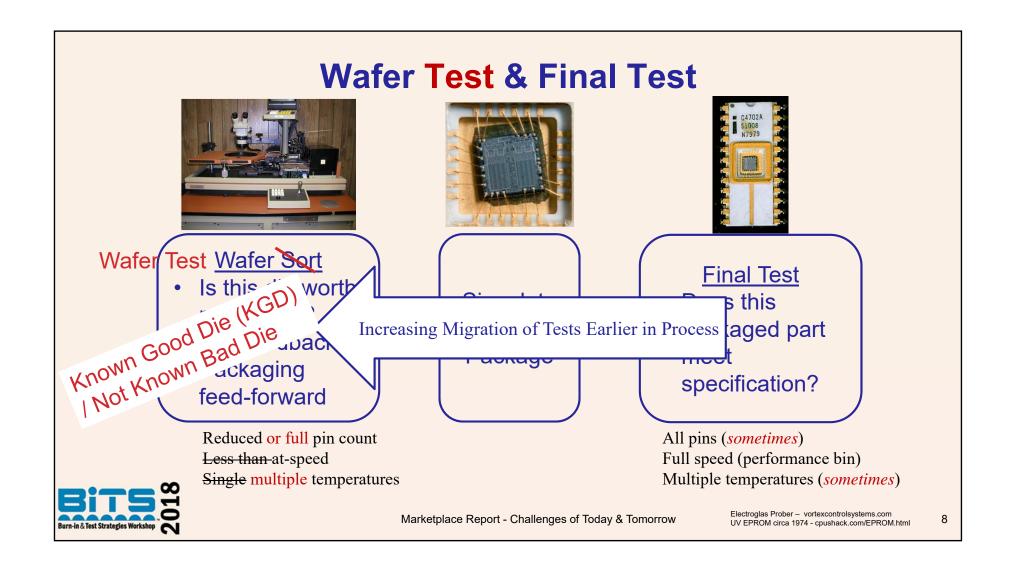

- Final vs. Wafer Test

- System Level Test

- Impending Challenges

- Internet of Things (IoT)

- Mobile Devices

- Tomorrow's Challenges

- Socket Market

Marketplace Report - Challenges of Today & Tomorrow

#### **TODAY'S CHALLENGES**

Marketplace Report - Challenges of Today & Tomorrow

#### How are electronics tested?

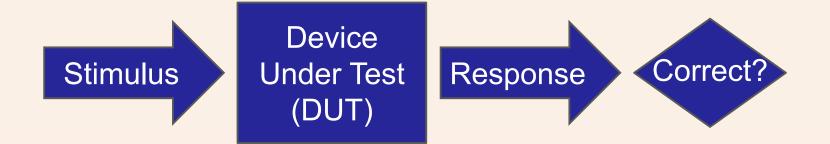

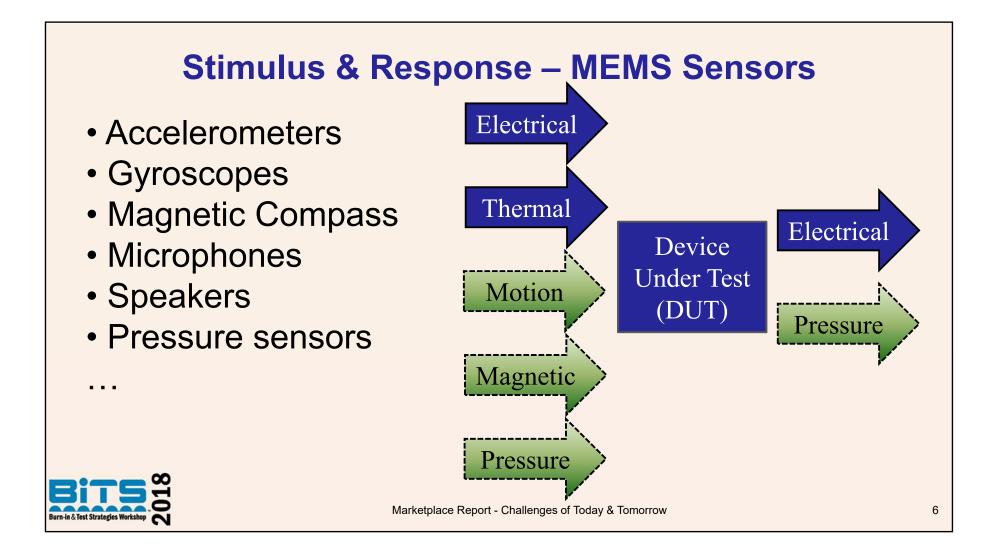

Stimulus – Response used on Device Under Test (DUT)

Marketplace Report - Challenges of Today & Tomorrow

#### **Advanced / Chip Scale Packaging**

Wafer Level Chip Scale Packaging

Fan Out Wafer Level Packaging

(Chip Scale ≤ 1.2x Die Size)

Heterogeneous Integration – System in Package (SiP)

→ Disruptive to entire supply chain – including test

Marketplace Report - Challenges of Today & Tomorrow

ASE / IFTLE 295 - Phil Garrou - July 2016 9

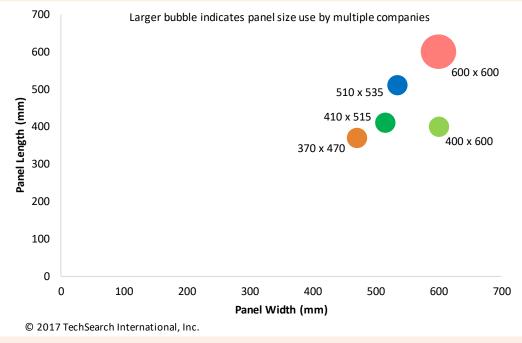

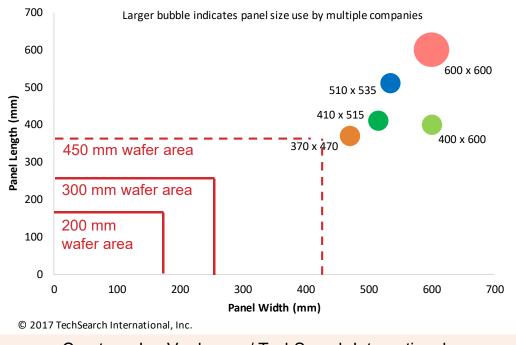

#### **Panel Level Processing**

#### No Consistent Panel Size for Large Area FO-WLP

Courtesy Jan Vardaman / TechSearch International

Marketplace Report - Challenges of Today & Tomorrow

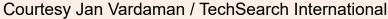

### **Panel Level Processing**

in wafer diameter results in 2.25x the area

600 mm sq. panel is 5x area of 300 mm wafer

Marketplace Report - Challenges of Today & Tomorrow

#### **Future Panel Test Handler?**

Marketplace Report - Challenges of Today & Tomorrow

### **System Level Test – Wide Range of Solutions**

Nvidia GPU

(AnandTech)

Chroma ATE

**Astronics Test Systems**

Marketplace Report - Challenges of Today & Tomorrow

#### Why SLT?

- Lower cost of test

- For some devices vs. automated test equipment (ATE)

- Typically microprocessors (MPU) / application processors (SoC),

graphical processors (GPU), and field programmable gate arrays (FPGA)

- Full 'stress' of device

- Can uses 'operating system' or diagnostic code in 'mission mode'

- Multi-Device interdependency

- Extended test times

- Burn-in 'lite'

Marketplace Report - Challenges of Today & Tomorrow

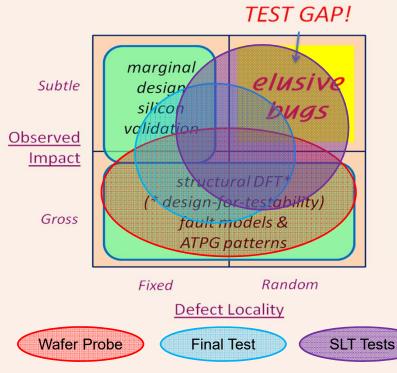

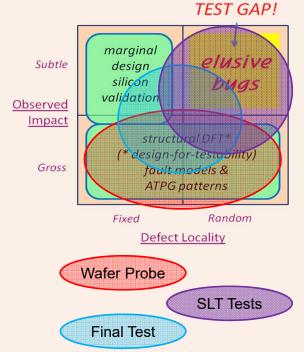

# **System Level Test (SLT)**

#### Today . . .

- Structural test techniques find most silicon defects

- Rise in random/subtle defects defected by SLT

- Redundant testing for faults

#### Tomorrow . . .

Expanded fault dictionary to ensure faults are only tested once in manufacturing flow

Courtesy Dave Armstrong / Advantest & HIR Test TWG

Marketplace Report - Challenges of Today & Tomorrow

Marketplace Report Challenges of Today & Tomorrow

#### **IMPENDING CHALLENGES**

Marketplace Report - Challenges of Today & Tomorrow

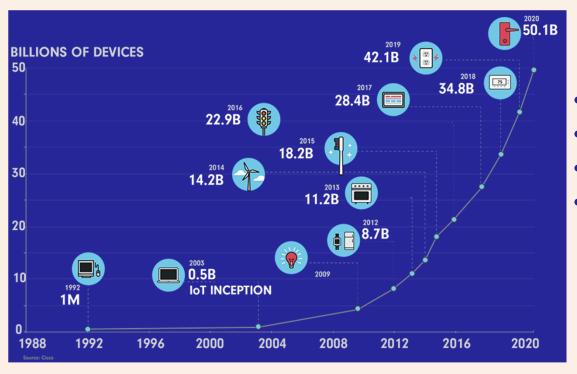

#### **Internet of Things**

- Billions of devices

- Exabytes/month data

- Typically wireless

- Cost sensitive

Marketplace Report - Challenges of Today & Tomorrow

NCTA / Cisco 18

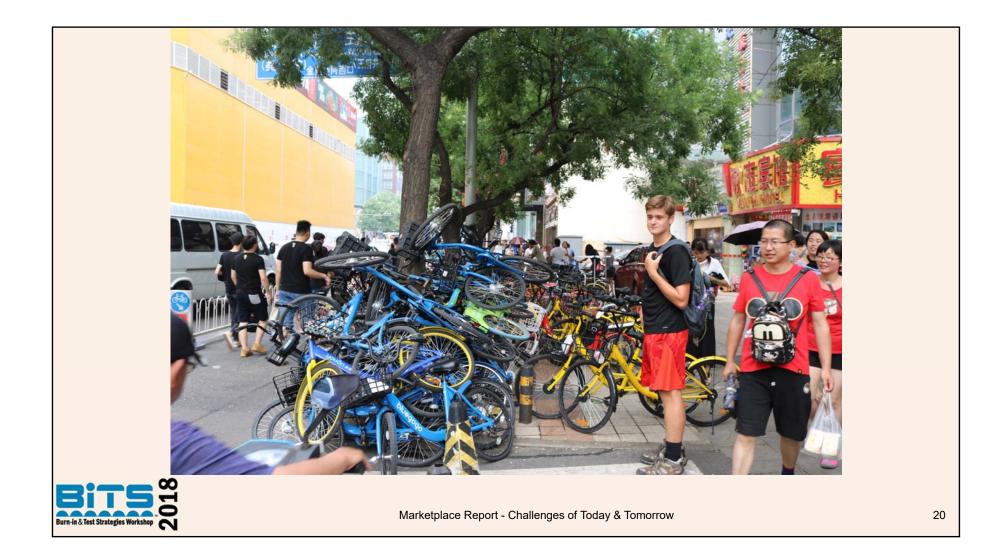

#### IoT – Bicycle Sharing

At the right price, IoT applications become ubiquitous.

Outside Beijing Wangfujing Hilton Hotel

Marketplace Report - Challenges of Today & Tomorrow

ofo 19

# **Mobile Applications**

- Low Latency

- Power Management

Marketplace Report - Challenges of Today & Tomorrow

Qualcomm, Waymo, Amazon 21

Marketplace Report Challenges of Today & Tomorrow

### **TOMORROW'S CHALLENGES**

Marketplace Report - Challenges of Today & Tomorrow

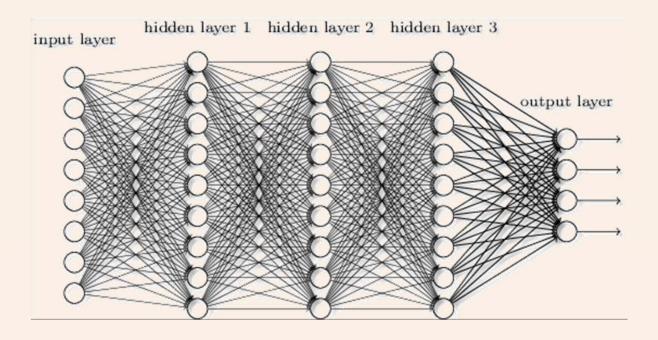

#### **Neural Networks**

Marketplace Report - Challenges of Today & Tomorrow

TheWindowsClub.com / Mathworks 23

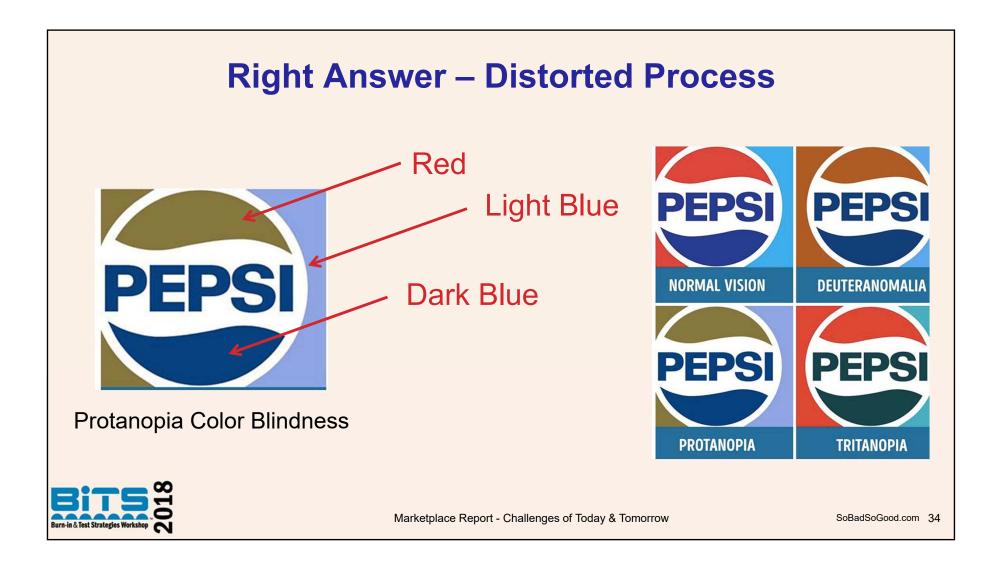

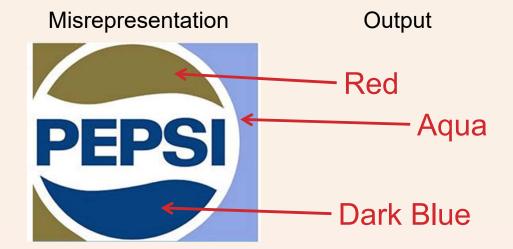

Do we care? What if not consistent?

Protanopia Color Blindness

Marketplace Report - Challenges of Today & Tomorrow

SoBadSoGood.com 24

Marketplace Report Challenges of Today & Tomorrow

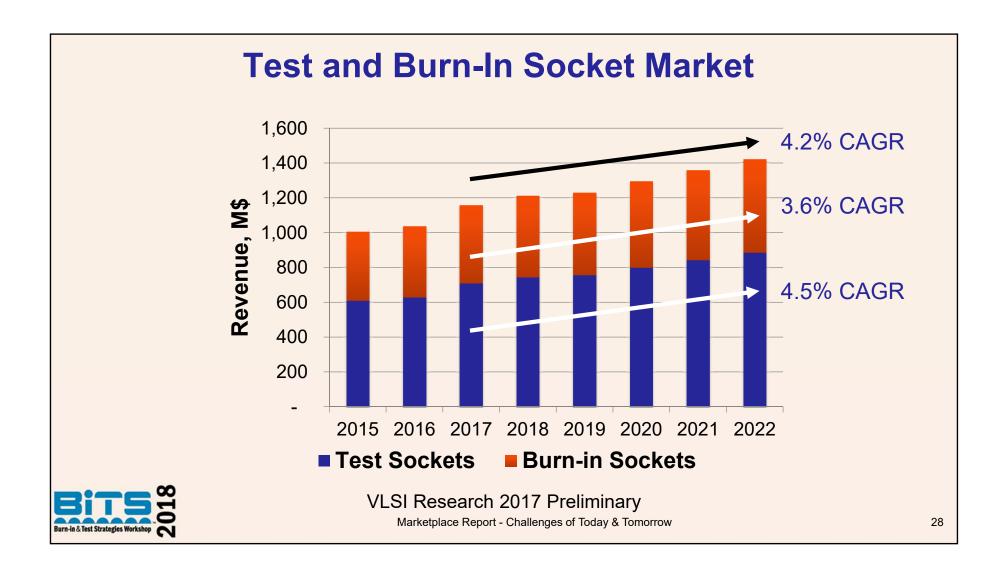

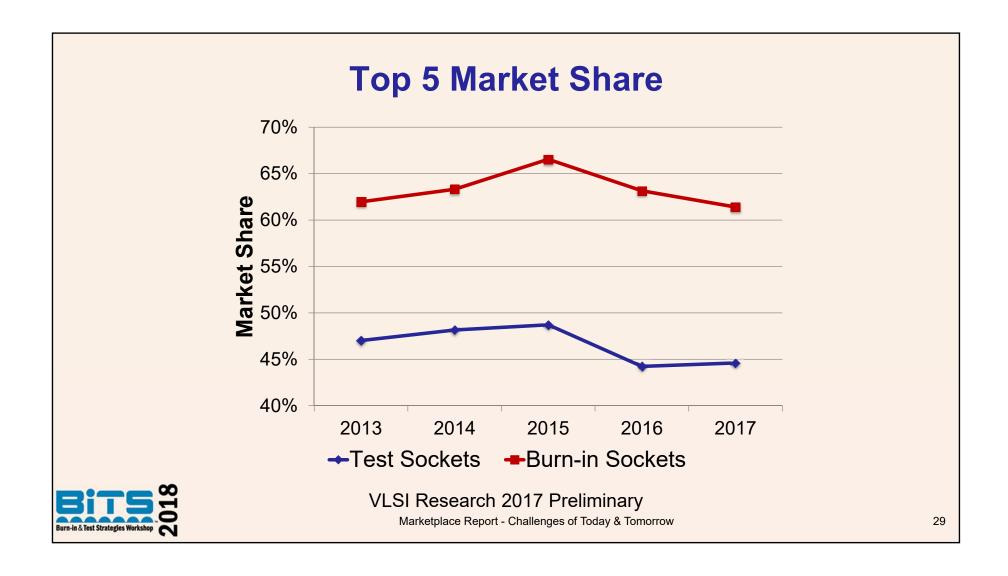

#### **SOCKET MARKET**

Marketplace Report - Challenges of Today & Tomorrow

### **Top Test & Burn-in Vendors**

| Rank | 2015                    | 2016                    | 2017 Preliminary        |

|------|-------------------------|-------------------------|-------------------------|

| 1    | Yamaichi<br>Electronics | Yamaichi<br>Electronics | Yamaichi<br>Electronics |

| 2    | Enplas                  | Enplas                  | Enplas                  |

| 3    | Smiths Connectors       | ISC                     | ISC                     |

| 4    | ISC                     | Smiths Connectors       | Smiths Interconnect     |

| 5    | Sensata<br>Technologies | LEENO Industrial        | LEENO Industrial        |

VLSI Research 2017 Preliminary

Marketplace Report - Challenges of Today & Tomorrow

#### **Acknowledgements**

- Lin Fu and John West VLSI Research

- Dave Armstrong Advantest / HIR Test TWG Leader

- Jan Vardaman TechSearch International

- Roger Sinsheimer Teradyne

Marketplace Report - Challenges of Today & Tomorrow

Marketplace Report Challenges of Today & Tomorrow

Marketplace Report - Challenges of Today & Tomorrow

#### System Level Test (SLT)

#### Today . . .

- 1. Structural test techniques find most silicon defects.

- The industry is seeing a rise in random/subtle defects. (those found by SLT)

- Multiple test steps are resulting in many faults being re-tested multiple times over again.

#### Tomorrow . . .

- We will better understand the faults identified in SLT testing.

- 2. We will expand the test content at wafer probe to cover more of these issues.

- 3. We will manage an expanded fault dictionary to ensure that faults are only tested once during the manufacturing flow.

Courtesy Dave Armstrong / Advantest & HIR Test TWG

Marketplace Report - Challenges of Today & Tomorrow