#### **BiTS 2017**

Making Contact - Contact Technology - 1 of 2

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

## **Copyright Notice**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2017 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2017 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2017 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Making Contact - Contact Technology - 1 of 2

### **BiTS 2017**

Session 6 Jason Mroczkowski

Session Chair

#### **BiTS Workshop 2017 Schedule**

## Frontier Day

Tuesday March 7 - 1:30 pm

#### Making Contact

#### "High Current Final Test Contactor Development"

Thiha Shwe, Hisashi Ata – Texas Instruments

Kenichi Sato – Yokowo

#### "Customers Are the New Team Member for Board to Board Connectors"

**Derek Biggs – Plastronics**

#### "WLCSP Contacting Technologies for 0.2 mm Pitch and Below"

Valts Treibergs - Xcerra Corporation

#### "Coming to terms with Burn-In sockets"

James Tong - Texas Instruments

Burn-in & Test Strategies Workshop

#### **BiTS 2017**

## Coming to Terms with Burn-In Sockets

#### James Tong Texas Instruments

BiTS Workshop March 5 - 8, 2017

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

Making Contact - Contact Technology - 1 of 2

#### **BiTS 2017**

#### Contents

- Background

- Root cause review

- Solution selection

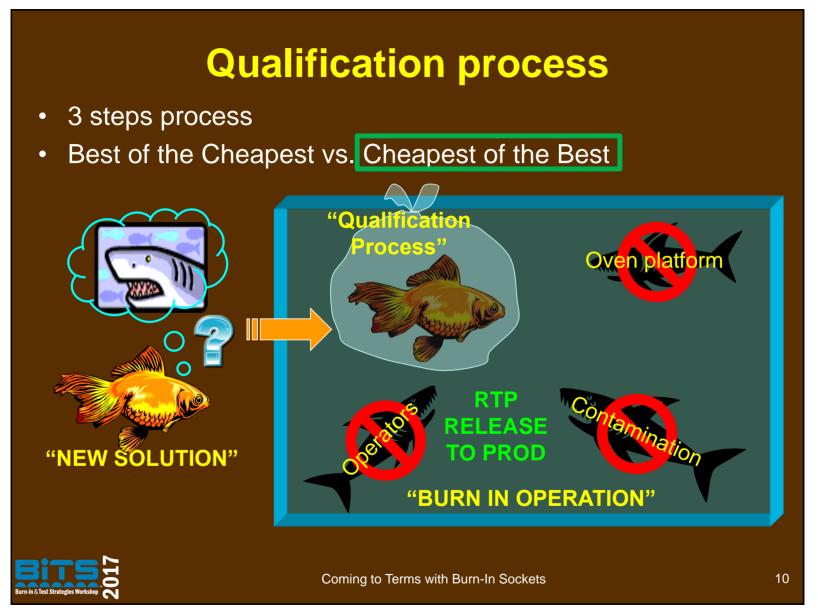

- Qualification process

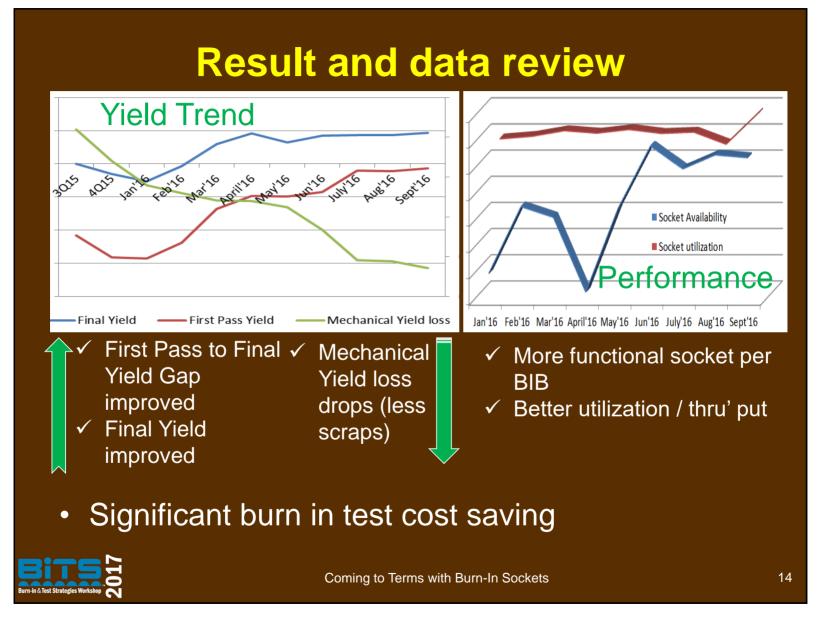

- Result and data review

- Lesson learned

- Standardization

- Future plan

Coming to Terms with Burn-In Sockets

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

#### **BiTS 2017**

#### Background

- Custom solution per device per supplier

- Solution selected base on

- good faith and experience from last project

- pricing is the main driver

- Engineering hardware for device checkout/qualification gets propagated to production burn in

Coming to Terms with Burn-In Sockets

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

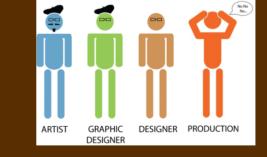

#### **Root cause review**

- Historically used solution was inferred to be the best solution

- Ball damaged due to stuck pin

- Plastic socket housing around the pin melted with Tj >200°C

- High current

- Contact resistance failure

- Housing material

- Defective device

- 5Ws => Ball deformation → stuck pin → melted housing → heated spring → current flows thru the spring

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

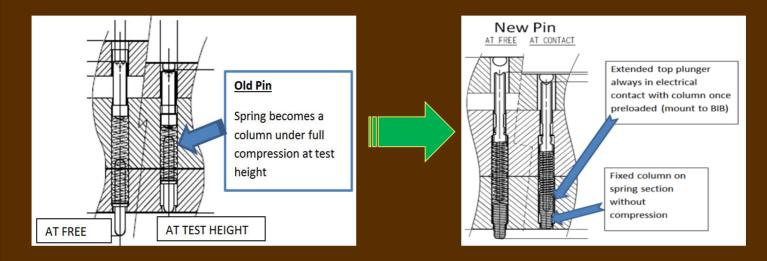

# Solution selection – pick the right pin structure

Considering the possible root causes of failure

Plan checkout DOEs

Burn-in & Test Strategies Workshop

Your Paper Title Here:

BiTS Presentation Guide & Template 1.0

8

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

#### **Solution selection – decision matrix**

| Selection Matrix     |           |          |          |          |          |      | Parameter Units |                    | Units        |

|----------------------|-----------|----------|----------|----------|----------|------|-----------------|--------------------|--------------|

| Supplier             | Weightage | Vendor A | Vendor B | Vendor C | Vendor D | 1    |                 |                    | Manufacture  |

| Cost                 | 3         | 4        | 5        | 3        | 4        | 2    | s               | Pin Model #        |              |

| Design Robustness    | 5         | 4        | 2        | 3        | 4        | 3    | dass            | Package            |              |

|                      | -         | -        | ~        |          |          | 4    | _               | Pin Use            |              |

| Responsiveness       | 3         | 2        | 4        | 3        | 4        | 5    |                 | Status             |              |

| A/T site Support     | 3         | 3        | 2        | 4        | 4        | 6    | Cost            | Price/pin          | US\$         |

| Dallas Dev. Support  | 3         | 4        | 3        | 4        | 4        | 7    |                 |                    | Pin Drawing# |

| Pin Design           | 5         | 3        | 4        | 3        | 4        | 8    | Mechanical      | Working CPH        | mm           |

| 5                    | -         |          | -        |          | -        | 9    |                 | Force @ cph        | grams        |

| Engineeering Support | 4         | 4        | 3        | 3        | 4        | 10   |                 | Min Pitch          | mm           |

| Quality              | 3         | 2        | 3        | 3        | 4        | 11   |                 | PCB Pre-Load       | mm           |

| Deliverv             | 4         | 3        | 4        | 2        | 4        | 12   |                 | DUT Compression    | mm           |

|                      |           |          | •        | -        | -        | 13 💆 | Tip Shape       | (PCB Side)         |              |

| Unweigthed Average   |           | 3.22     | 3.33     | 3.11     | 4.00     | 14   |                 | rip snape          | (Dut Side)   |

| Total                |           | 102      | 100      | 92       | 120      | 15   |                 | Temp               | Deg C        |

|                      |           |          |          |          |          | 16   |                 | Kelvin F/S Pin Gap | mm           |

- Pick supplier  $\rightarrow$  matrix

- Specify pin → worst case test requirement

- Qualify selected solution → qualification plan to define roadmap solutions

| 3  | Ga S       | Package                  |                  |  |  |  |  |  |

|----|------------|--------------------------|------------------|--|--|--|--|--|

| 4  | Ŭ          | Pin Use                  |                  |  |  |  |  |  |

| 5  |            | Status                   |                  |  |  |  |  |  |

| 6  | Cost       | Price/pin                | US\$             |  |  |  |  |  |

| 7  |            | Pin Drawing#             |                  |  |  |  |  |  |

| 8  |            | Working CPH              | mm               |  |  |  |  |  |

| 9  |            | Force @ cph              | grams            |  |  |  |  |  |

| 10 | Mechanical | Min Pitch                | mm               |  |  |  |  |  |

| 11 |            | PCB Pre-Load             | mm               |  |  |  |  |  |

| 12 |            | DUT Compression          | mm               |  |  |  |  |  |

| 13 |            | Tip Shape                | (PCB Side)       |  |  |  |  |  |

| 14 |            | Tip Shape                | (Dut Side)       |  |  |  |  |  |

| 15 |            | Temp                     | Deg C            |  |  |  |  |  |

| 16 |            | Kelvin F/S Pin Gap       | mm               |  |  |  |  |  |

| 17 | Electrical | Cres                     | mOhm             |  |  |  |  |  |

| 18 |            | CCC                      | Amps             |  |  |  |  |  |

| 19 |            | Induct Self              | nH               |  |  |  |  |  |

| 20 |            | Induct Mutual            |                  |  |  |  |  |  |

| 21 |            | Cap Gnd                  | pF               |  |  |  |  |  |

| 22 |            | Cap Mutual               | P                |  |  |  |  |  |

| 23 |            | Insertion Loss (S21)     | GHz @ -1dB       |  |  |  |  |  |

| 24 |            | Return Loss (S11)        | GHz @ -20dB      |  |  |  |  |  |

| 25 |            | DUT Tip F                | Plating Material |  |  |  |  |  |

| 26 | -          | DUT Tip Base Material    |                  |  |  |  |  |  |

| 27 | li i       | PCB Tip Plating Material |                  |  |  |  |  |  |

| 28 | Chemical   | PCB Tip Base Material    |                  |  |  |  |  |  |

| 29 | 8          | Spring Matl              |                  |  |  |  |  |  |

| 30 |            | Housing Mat              |                  |  |  |  |  |  |

| 31 | Prod       | Life                     | Insertions       |  |  |  |  |  |

| 32 | E.         | Cleaning Interval        | Insertions       |  |  |  |  |  |

| 33 | Comment    |                          |                  |  |  |  |  |  |

Coming to Terms with Burn-In Sockets

Burn-in & Test Strategies Workshop

#### **BiTS 2017**

Making Contact - Contact Technology - 1 of 2

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

## **Qualification process – Step1**

Step 1: Vendor Self Qual and to submit report

- Pin Spec on Force, Cres, Lifetime (>5k)

- 2 Reliability test report up to 1000hr for Cres, Package sticking, Contact Mark and contamination check

- 3 Pin drawing

- 4 Socket design showing Z-stack up at test

- 4a Details on Z-stack up at test

- 4b Light colored or white base (good contrast to DUT for easy manual loading)

- 5 Pin to ball alignment validation (Positional analysis using RSS value or cross sectioning method)

- 6 Package wrapage simulation and other potential concern

- 7 Ra spec and report on nickle plated mirror finish Boss sample

- 8 Footprint compatability to TI std

- 9 Cabless connection for heater/thermistor if Dynamic temperatue control is applicable

- 10 CMT open top socket

- Max 2 pins designs to support all pitch in package family (BGA, QFN, QFP)

- CCC of 2 A or greater, Pin force of 15g/pin or less

- Vendor factory data on proposed pin solution

- Engineering data to support design robustness

Making Contact - Contact Technology - 1 of 2

### **Qualification process – Step2**

| Step 2: FAI checkout |                                                                                                                              |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                    | 1 to 3 BIBs FAI checkout with BU                                                                                             |  |  |  |

| 2                    | Full functionality                                                                                                           |  |  |  |

| 3                    | Die and package crack eval as needed                                                                                         |  |  |  |

| 4                    | Run 5 to 10 consecutive insertions using production test program (100% electrical yield) and visual mechanical check on ball |  |  |  |

| 7                    | damage, tool marks, bottom and top side marring, substrate damage and no damage to PCB pad on BIB                            |  |  |  |

| 5                    | Full BIS test in A/T site on sample units used                                                                               |  |  |  |

- Small sample functionality engineering checkout

- Electrical performance

- Mechanical performance

- Operation friendliness

Coming to Terms with Burn-In Sockets

12

Making Contact - Contact Technology - 1 of 2

## **Qualification process – Step3**

#### Step 3: Production Qualfication

- 1 Repeat DOE (5 insertions) in step 2 at production site for repeatability

- 2 Identify lots to begin qual in production site

- 3 Pass ALU operation with no issue if applicable

- 4 Run 100 insertions under normal production conditions

- 4a No or comparable production VM failure from inspections logpoints and BIS

- 4b No physical damage to PCB pad on the BIB

- 4c Comparable or better Frist Pass Yield

- 4d Comparable or better Final Yield

#### Production correlation

- High volume production qualification of solution

- Expose to typical production variables

#### **BiTS 2017**

Making Contact - Contact Technology - 1 of 2

Burn-in & Test Strategies Workshop

Making Contact - Contact Technology - 1 of 2

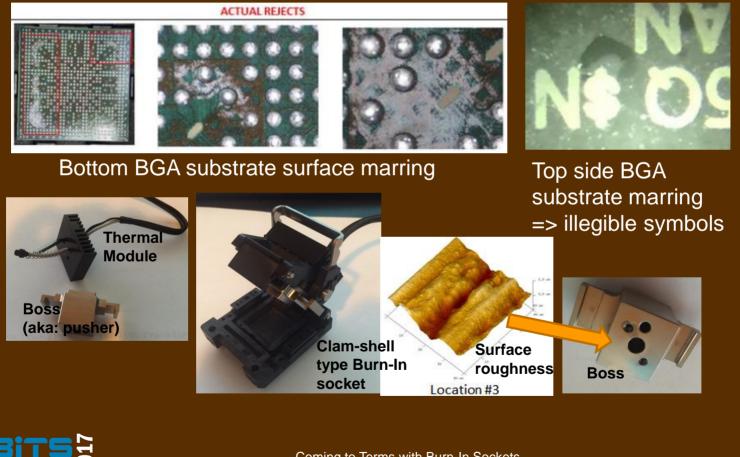

## Lesson learned – Device surface marring

Coming to Terms with Burn-In Sockets

**Burn-in & Test Strategies Workshop**

#### **BiTS 2017**

Making Contact - Contact Technology - 1 of 2

#### **Lesson learned – Pin structure**

Reproduced from BiTS workshop 2003 (Prasanth Ambady, James Forster & Jason Cullen – Texas Instruments)

- **Through hole** pinch contact pin is problematic for BGA

- Impossible to replace worn off or damage socket

Making Contact - Contact Technology - 1 of 2

#### **Standardization**

- Adopt proven qualification process

- Socket base sizes → Burn In Board (BIB) density

- Use compression mount technology (CMT) pins only

- Lock in socket mechanical design

- Minimize pin type/geometry for all device pitch

- Lower cost with best solution and volume

#### **Bits 2017**

Making Contact - Contact Technology - 1 of 2

#### **Future plan**

- Use only roadmap CMT pin solution

- Open top sockets design

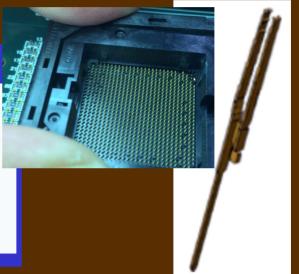

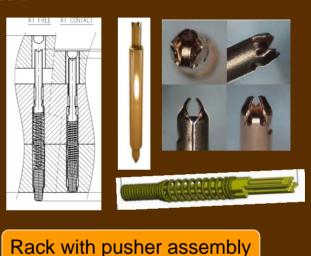

- Use rack style solution for active temperature control requirement

- Ability to use multiple socket suppliers on same device

- Collaboration to define industry standard

Open Top sockets

18

**BIB PCB**

Clam-shell socket style

Making Contact - Contact Technology - 1 of 2

#### Acknowledgement

- TI operations team

- TI management team

enplas

- Suppliers

- BiTS2017 committee and attendees

Coming to Terms with Burn-In Sockets

Burn-in & Test Strategies Workshop