### **BiTS 2017**

Reality Check - Validation & MEMS Test

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

# **Copyright Notice**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2017 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2017 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2017 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

### Reality Check - Validation & MEMS Test

### **Bits 2017**

Reality Check - Validation & MEMS Test

### **BiTS 2017**

# Augmenting Form Factor Designs with Validation and Debug Capability

# John Kelbert Intel Corporation

BiTS Workshop March 5 - 8, 2017

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

March 5-8, 2017

### **BiTS 2017**

Reality Check - Validation & MEMS Test

**Burn-in & Test Strategies Workshop**

### Reality Check - Validation & MEMS Test

**Burn-in & Test Strategies Workshop**

**Bits 2017**

Reality Check - Validation & MEMS Test

### **Reality – Many Products are Late**

"..79% of new products miss the launch date<sup>1</sup>, companies have an enormous opportunity to increase sales and profitability by improving new product time to market (TTM)<sup>2</sup>"

<sup>1</sup>CGT/Sopheon Survey

<sup>2</sup>https://www.sopheon.com/new-product-time-to-market/

Augmenting Form Factor Designs with Validation and Debug Capability

7

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

### **BiTS 2017**

Reality Check - Validation & MEMS Test

Start with this

# **Complexity Management with Multi-step Platform Approach**

Initial debug platform

- Easy to access

- Easy to debug

- Modular, reconfigure

Augmenting Form Factor Designs with Validation and Debug Capability

### **BiTS 2017**

Reality Check - Validation & MEMS Test

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

Reality Check - Validation & MEMS Test

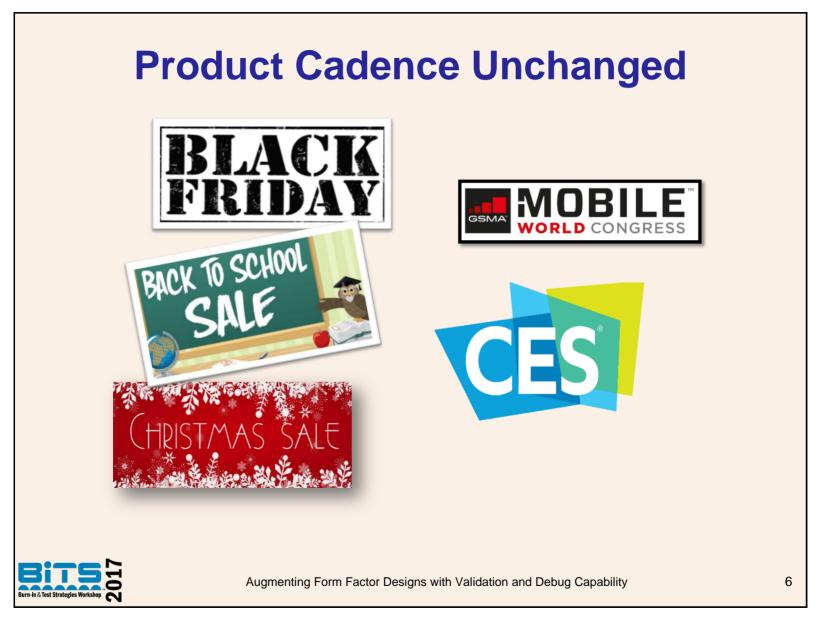

# **Complexity Management with Multi-step Platform Approach**

### Starting point: debug platform

- Easy to access

- · Easy to debug

- Modular, reconfigure

End point: product

- Difficult to access

- Challenging to debug

- Fixed configuration

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

# **Complexity Management with Multi-step Platform Approach**

All the while avoiding shortcuts that could lead to disaster

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

Reality Check - Validation & MEMS Test

# **Upside of Multi-step Platform**

- Advantages of specialized test platforms

- Flexibility, expose key interfaces, added instrumentation, capability, ...

### Initial starting point

Augmenting Form Factor Designs with Validation and Debug Capability

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

### **BiTS 2017**

Reality Check - Validation & MEMS Test

## **Downside of Multi-step Platform**

### <u>Disadvantages</u>

- PCB layers added for debug and test

- Longer routing of critical interfaces

- Connectors added to modularize

- Added test points

- Mounting holes for sockets

Initial starting point

Complexity added here...

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

### **Downside of Multi-step Platform**

Initial starting point

### Key Differences

Power and Performance Drivers, FW/BIOS Component placement PCB stackup Signal Integrity Power Integrity

End point

Complexity added here...

Compromises efforts and investment to get here.

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

# POWER AND PERFORMANCE PRODUCT TUNING

# Multi-step approach example: Designing in complexity

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

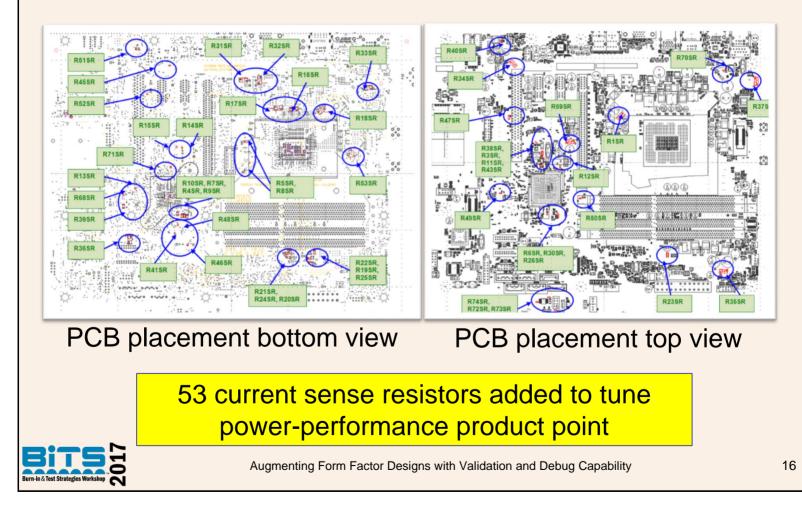

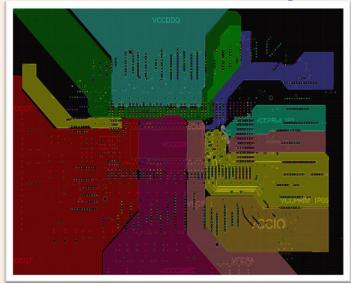

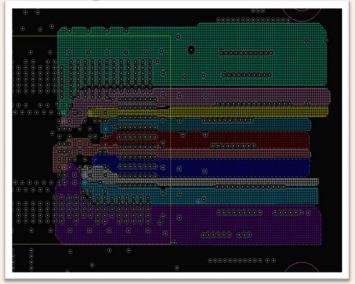

# Example: Power and Performance Board Layout

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

Reality Check - Validation & MEMS Test

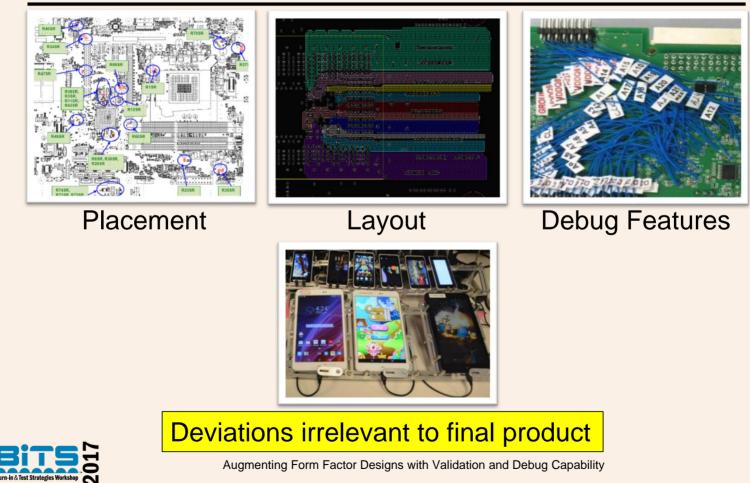

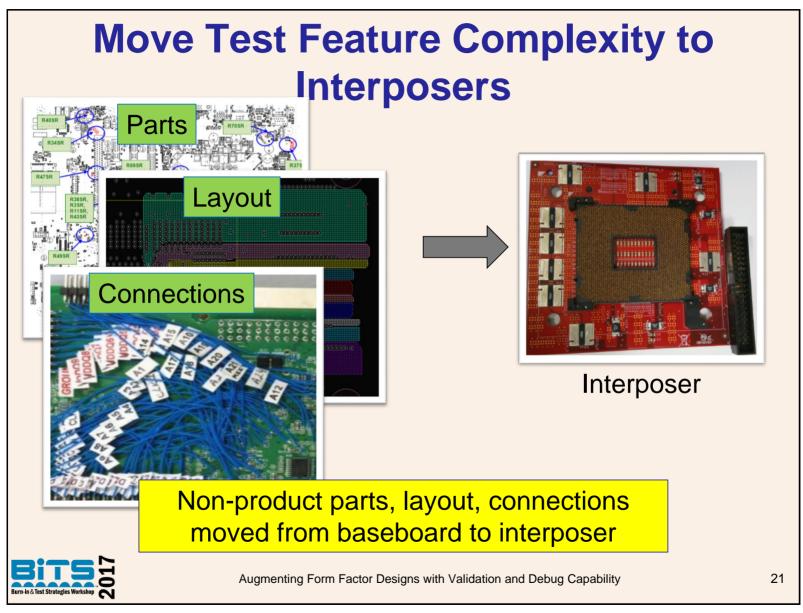

## Example: Power and Performance Power Layout Compromise

- Recommended product power shapes

- Product component placement

- Compromised power

shapes for instrumentation

- Component placement pushed out from SoC

Augmenting Form Factor Designs with Validation and Debug Capability

### **BiTS 2017**

Reality Check - Validation & MEMS Test

## Example: Power and Performance Physical Connections

Image: Best Inc.

Blue wires connections added for data acquisition equipment

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

### Consequences

### Non-product deviations

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

Reality Check - Validation & MEMS Test

# AUGMENTATION WITH INTERPOSERS

# A different approach

Augmenting Form Factor Designs with Validation and Debug Capability

### **BiTS 2017**

Reality Check - Validation & MEMS Test

### Reality Check - Validation & MEMS Test

### **BiTS 2017**

### **Interposer Possibilities**

### **Socketing Solutions**

### **Memory Configurations**

### **Power Profiling**

### **Debug Interfaces**

Augmenting Form Factor Designs with Validation and Debug Capability

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

### Reality Check - Validation & MEMS Test

### **BiTS 2017**

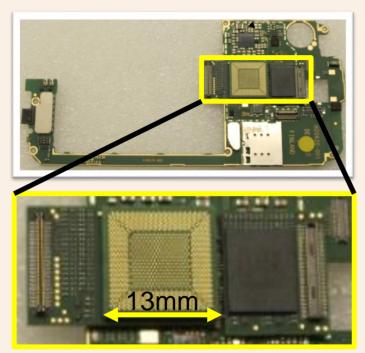

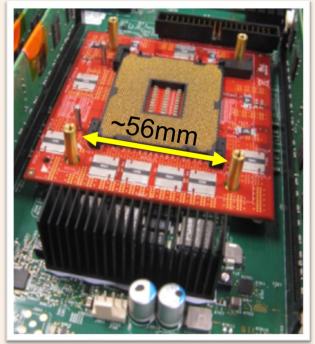

### **Interposer Extremes**

0.4mm pitch devices class debug interposer solution

1.0mm pitch server class power profiling solution

Augmenting Form Factor Designs with Validation and Debug Capability

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

### **BiTS 2017**

Reality Check - Validation & MEMS Test

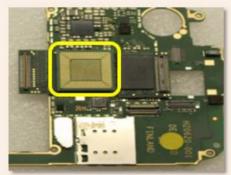

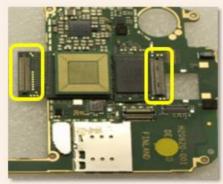

# **Socket Attach Opportunity** Socket attach site

Interposers became ideal candidates for attaching sockets without the need for additional mounting holes or keep out volume

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

# Augmentation enables a Return to Product Focus

Reduce non-product components Maintain product component placement Utilize product power plane shapes Eliminate need for added PCB layers Augmenting Form Factor Designs with Validation and Debug Capability 25

Reality Check - Validation & MEMS Test

# **Interposer Implementation Challenges and Limitations**

- Signal and power integrity impact

- Attachment of interposer to system

- Mechanical conflicts and keep out volumes

- Capability is limited to what can be exposed at component's system interface

Augmenting Form Factor Designs with Validation and Debug Capability

### Reality Check - Validation & MEMS Test

### **BiTS 2017**

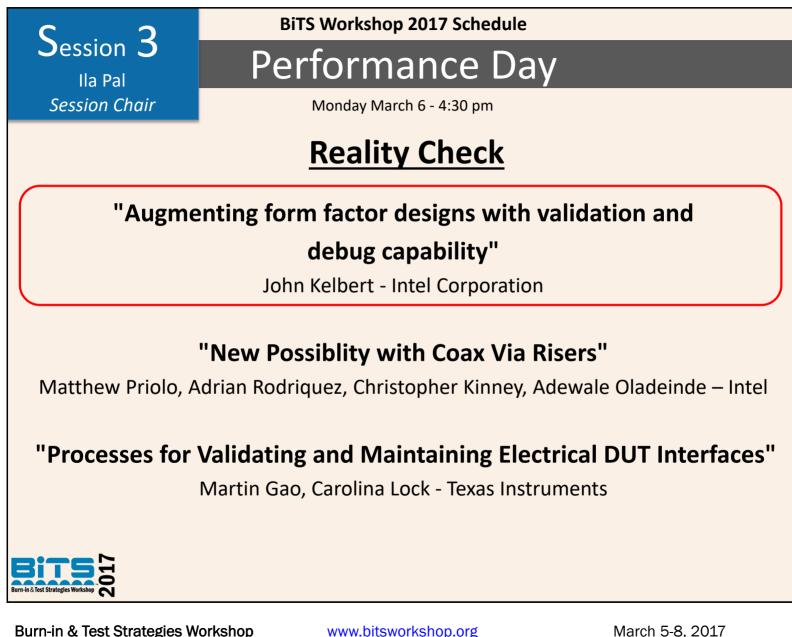

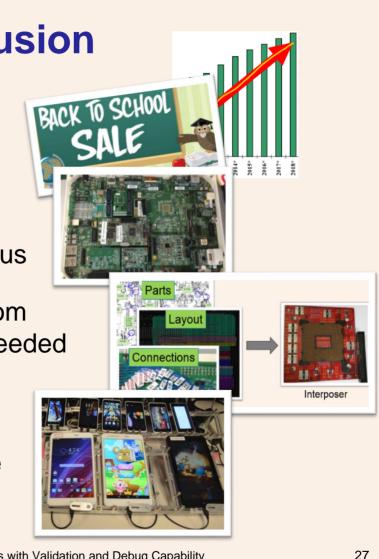

Product complexity rising

No change in product cadence

Validation and debug capability drive deviation from product focus

Interposers move complexity from target system while providing needed capability

Augmentation with interposers enables a stronger focus on the end product

Augmenting Form Factor Designs with Validation and Debug Capability

Reality Check - Validation & MEMS Test

# Acknowledgements

Interposer and riser development: Floy Campbell – Intel Corporation Ashok Kabadi – Intel Corporation (retired) Matthew G Priolo – Intel Corporation Adrian R Rodriguez – Intel Corporation

Augmenting Form Factor Designs with Validation and Debug Capability