#### **Market Session**

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

# **Copyright Notice**

The presentation(s)/poster(s) in this publication comprise the Proceedings of the 2017 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2017 BiTS Workshop. This version of the presentation or poster may differ from the version that was distributed in hardcopy & softcopy form at the 2017 BiTS Workshop. The inclusion of the presentations/posters in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation/poster content by BiTS Workshop. However, each presentation/poster is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

### **Market Session**

# **Marketplace Report**

# Ira Feldman Feldman Engineering Corp.

BiTS Workshop March 5 - 8, 2017 Feldman Engineering

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

# Outline

- Fundamentals

- How did we get here?

- Test Today

- Integrated "Ecosystems"

- Socket Market Data

Marketplace Report

#### **Market Session**

Burn-in & Test Strategies Workshop

### **Market Session**

Burn-in & Test Strategies Workshop

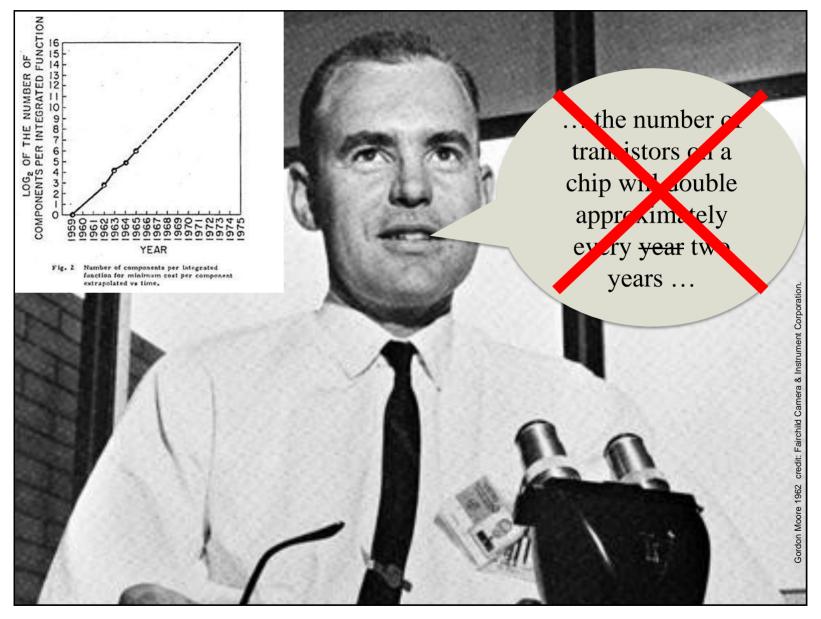

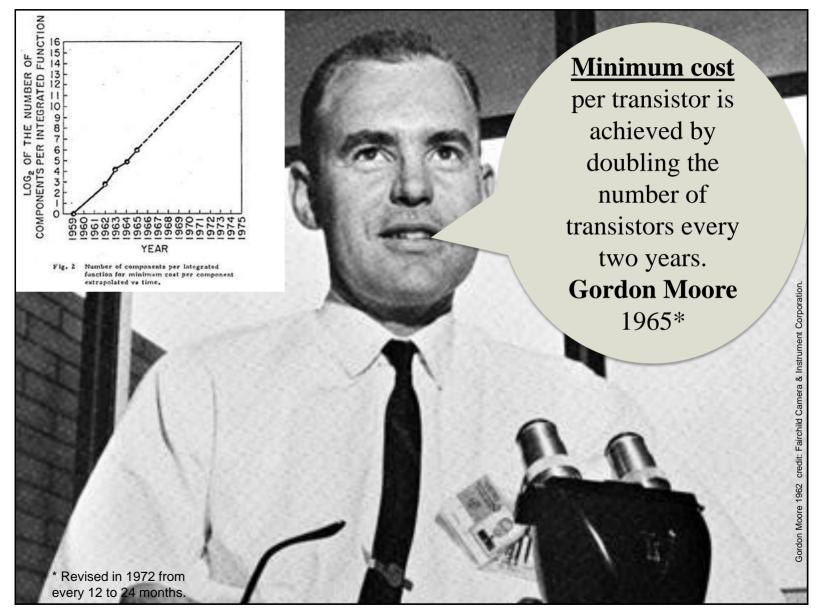

Electronics, Volume 38, Number 8, April 19, 1965

The experts look ahead

# Cramming more components

# onto integrated circuits

With unit cost falling as the number of components per circuit rises, by 1975 economics may dictate squeezing as many as 65,000 components on a single silicon chip

#### By Gordon E. Moore

Director, Research and Development Laboratories, Fairchild Semiconductor division of

Fairchild Camera and Instrument Corp.

The complexity for minimum component costs has increased at a rate of roughly a factor of two per year (see graph on next page). Certainly over the short term this rate can be expected to continue, if not to increase. Over the longer term, the rate of increase is a bit more uncertain, although there is no reason to believe it will not remain nearly constant for at least 10 years. That means by 1975, the number of components per integrated circuit for minimum cost will be

65,000.

Marketplace Report

8

### **Market Session**

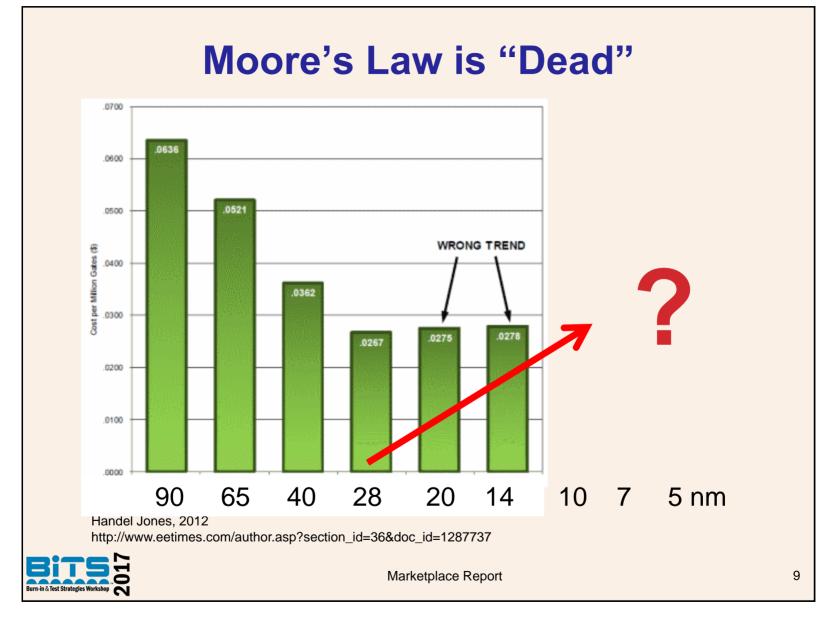

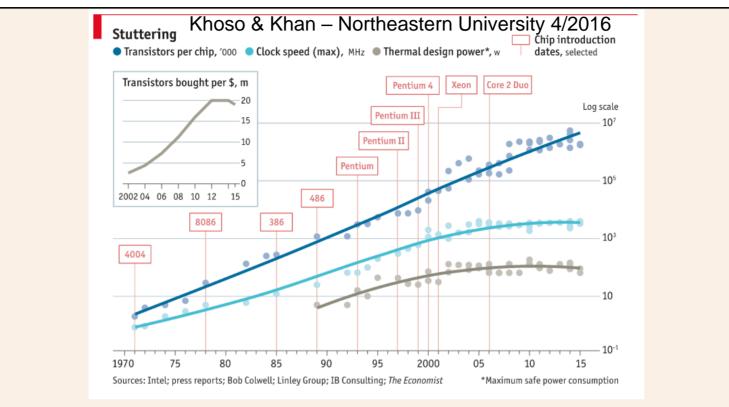

"Populist view: Any parameter related to semiconductors must form a straight line when plotted on exponential graph paper."

- Prof. Subramanian Iyer (UCLA, former IBM Fellow)

Marketplace Report

### **Market Session**

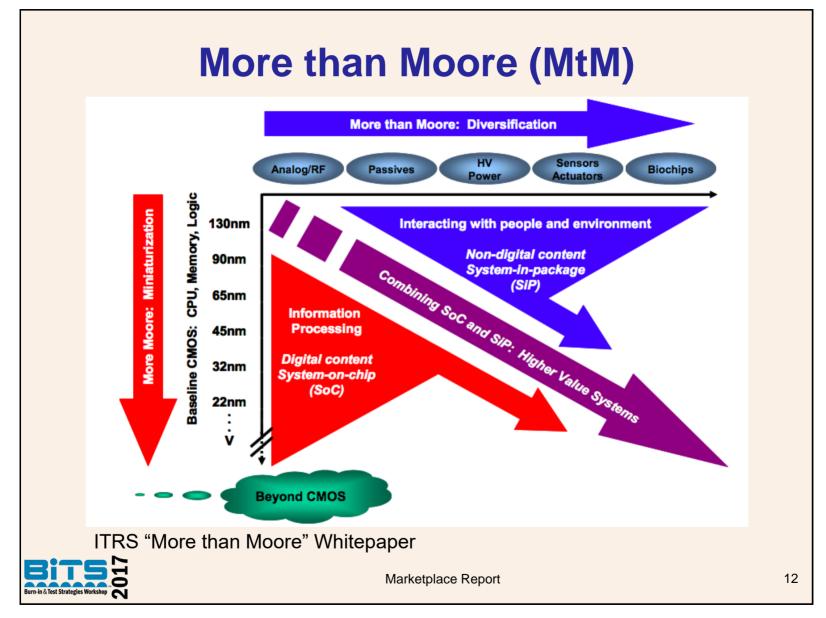

"Knobs" to reduce product cost

Transistor Scaling Materials Device Structure

Substrate Size cost / area

More than Moore Architecture Packaging

11

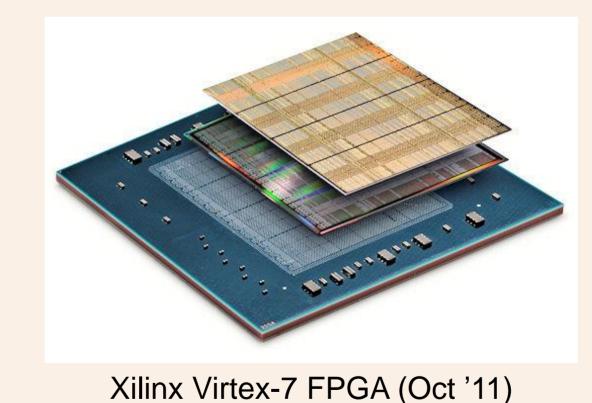

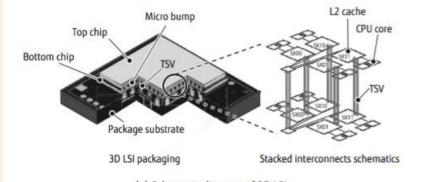

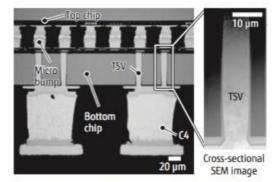

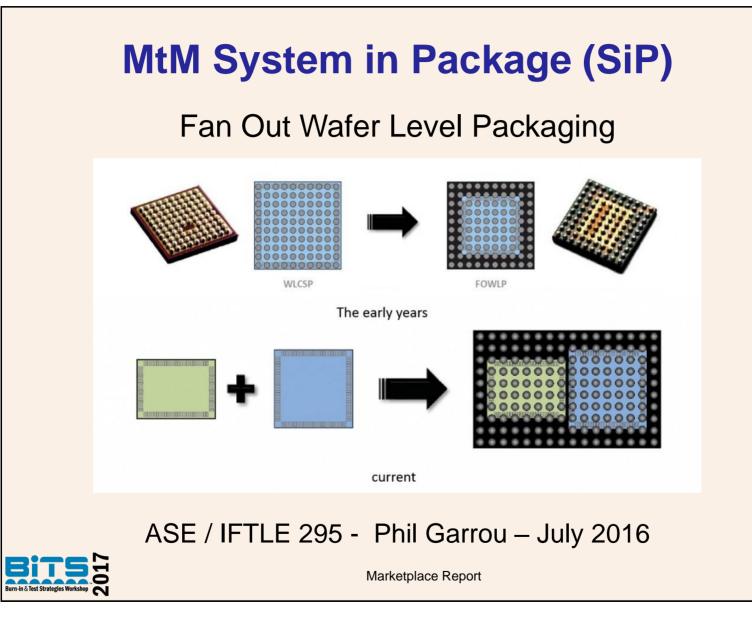

# MtM System in Package (SiP)

### 2.5D/3D/5.5D Packaging – First to Market

Marketplace Report

Burn-in & Test Strategies Workshop

(a) Schematic diagram of 3D LSI

(b) Cross-sectional image of 3D LSI

#### Table 1

Element technology items for 3D LSI and comparison of conventional technology and development target.

| Element technology items     | Conventional technology    | Development target                             |

|------------------------------|----------------------------|------------------------------------------------|

| TSV backside process         | >300 µm: 23 mm square chip | <100 µm: 23 mm square chip                     |

| C4 bump tolerable current    | 25 mA                      | >100 mA                                        |

| Micro bump material          | <10 mA/bump: SnAgmaterial  | >50 mA/bump: Intermetallic compounds junctions |

| Stacked die area             | 100 mm <sup>2</sup>        | >500 mm <sup>2</sup>                           |

| Number of micro bumps        | 150,000                    | 300,000                                        |

| TSV transmission performance | 20 GHz                     | 40 GHz                                         |

#### Kitada, et. al / Fujitsu - February 2017

Marketplace Report

**Burn-in & Test Strategies Workshop**

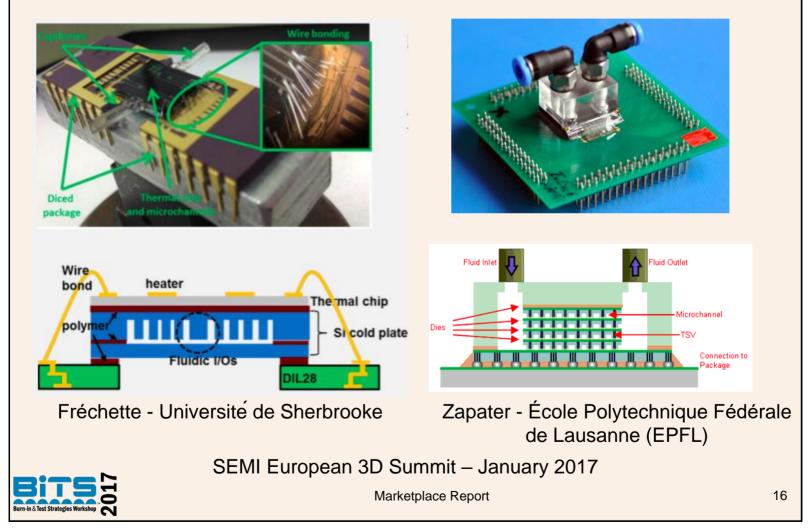

# **Microfluidics**

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

17

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 5-8, 2017

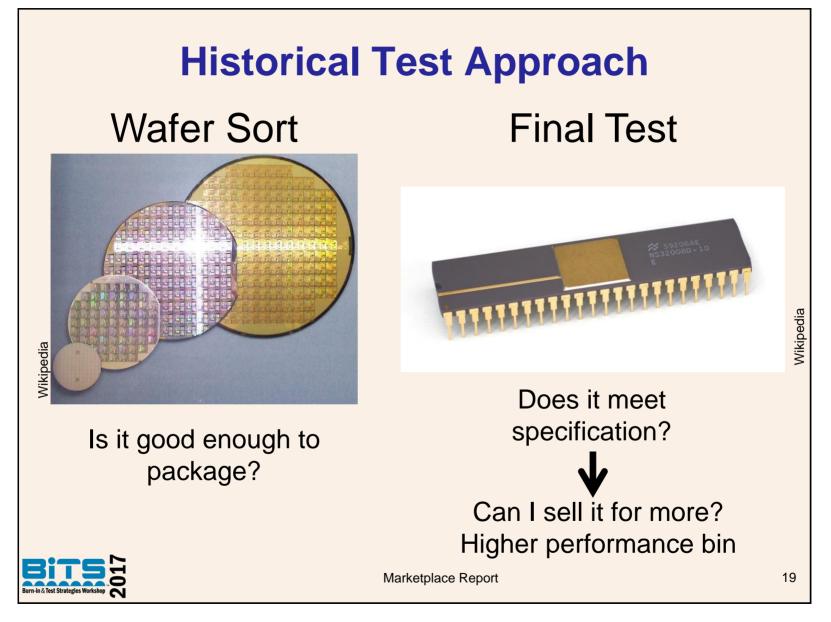

# **Paradigm Shift – Value Creation**

- Yield Management

- Process Improvement Feedback

- Die "matching"

- Repair

- Switch off defective "cores"

- Swapping in spares (memory, etc.)

- Performance Tuning

- Calibration

- Personalization

- Serialization

- Security & Keys

Marketplace Report

**Burn-in & Test Strategies Workshop**

Burn-in & Test Strategies Workshop

#### **Market Session**

**Burn-in & Test Strategies Workshop**

**Burn-in & Test Strategies Workshop**

**Burn-in & Test Strategies Workshop**

Burn-in & Test Strategies Workshop

**Market Session**

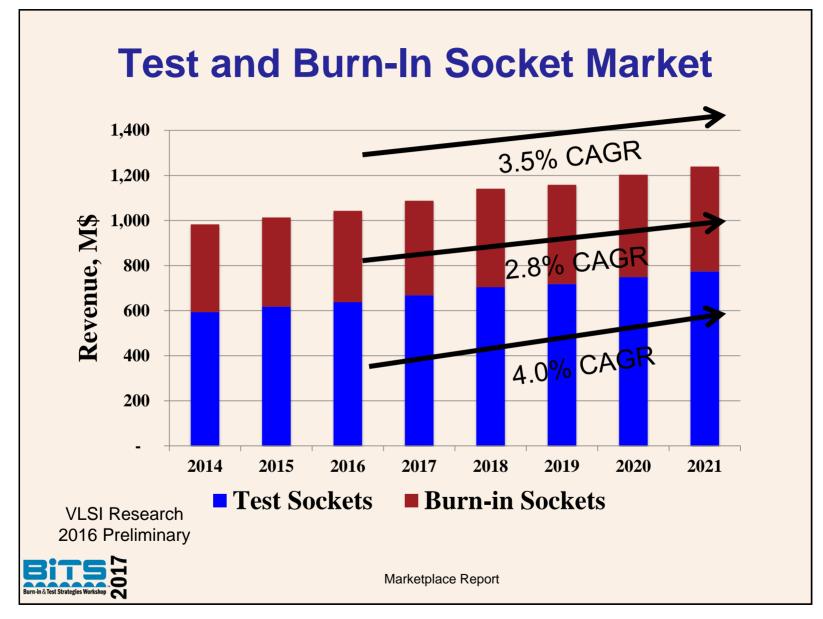

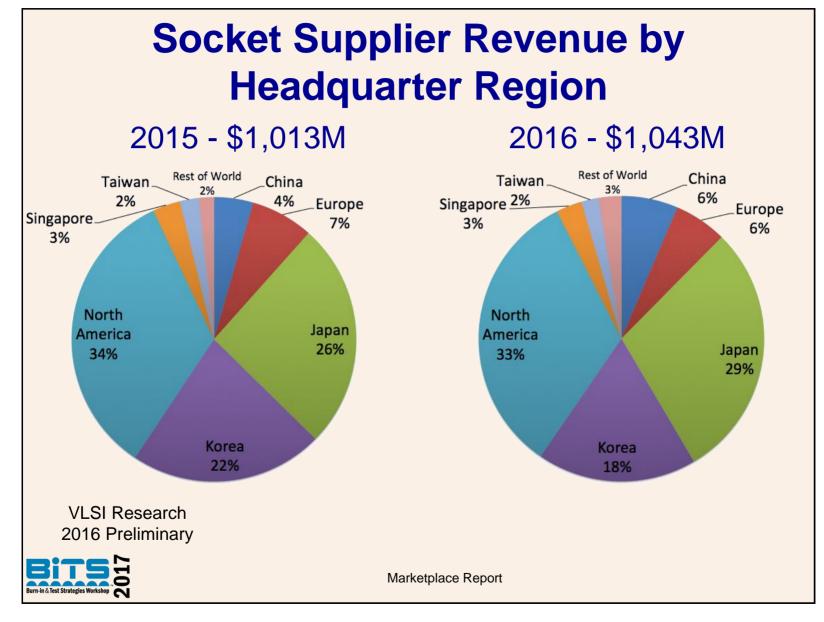

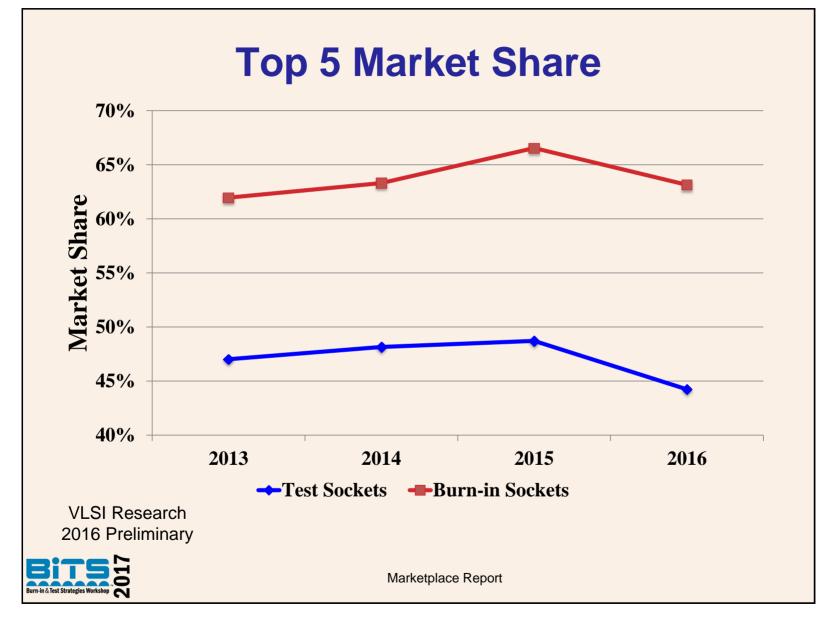

# **Top Test & Burn-in Socket Vendors**

|                                   | Rank               | 2014                    | 2015                    | 2016<br>Preliminary     |  |  |

|-----------------------------------|--------------------|-------------------------|-------------------------|-------------------------|--|--|

|                                   | 1                  | Yamaichi<br>Electronics | Yamaichi<br>Electronics | Yamaichi<br>Electronics |  |  |

|                                   | 2                  | Enplas                  | Enplas                  | Enplas                  |  |  |

|                                   | 3                  | Sensata<br>Technologies | Smiths<br>Connectors    | Smiths<br>Connectors    |  |  |

|                                   | 4                  | Smiths<br>Connectors    | ISC                     | ISC                     |  |  |

|                                   | 5                  | LEENO<br>Industrial     | Sensata<br>Technologies | LEENO<br>Industrial     |  |  |

| VLSI Research<br>2016 Preliminary |                    |                         |                         |                         |  |  |

| Birn-in & Test S                  | Marketplace Report |                         |                         |                         |  |  |

# Acknowledgements

Test Socket & Burn-in Socket data courtesy of John West at VLSI Research

Marketplace Report

Burn-in & Test Strategies Workshop