Burn-in & Test Strategies Workshop

www.bitsworkshop.org

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the BiTS China Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the BiTS China Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS China Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors. There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo, 'Burn-in & Test Strategies Workshop', 'BiTS China', and 'Burn-in & Test Strategies China Workshop' are trademarks of BiTS Workshop.

1

#### **BiTS China 2016**

#### **BiTS China 2016**

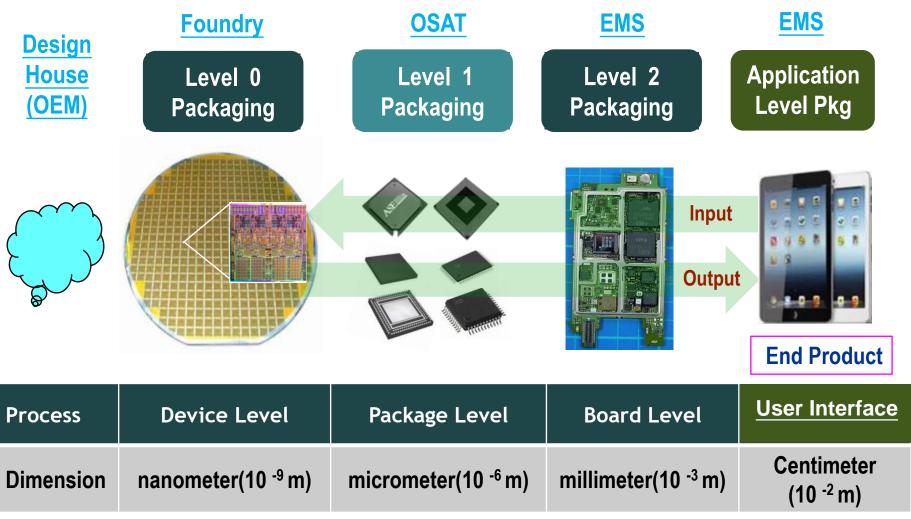

#### Keynote Address – Abstract & Biography

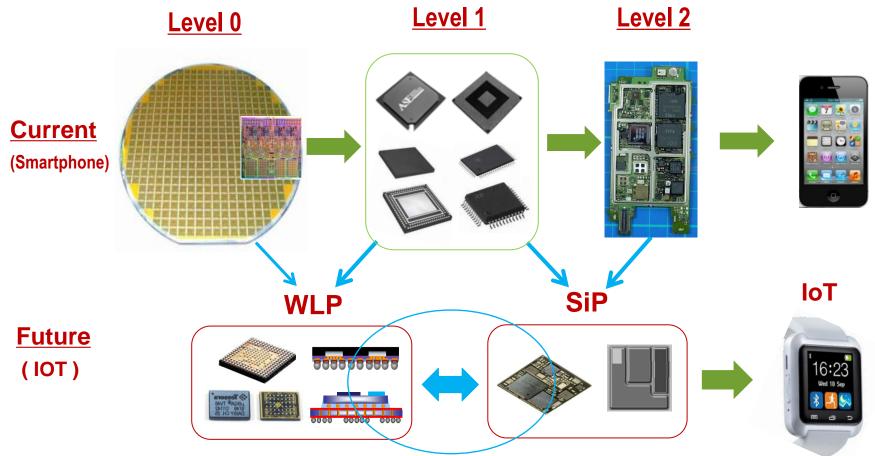

As the IoT applications become a more and more important part of people's life, packaging technologies are also evolved to meet the assembly and testing challenges for building the required semiconductor devices. In today's world, as the rapid expansions of IoT applications, typically presented by the mobile/wearable devices and networks, consumer products are high volume and low cost, small and power efficient. These applications impose requirements for highly integrated system solutions and associated new assembly and testing technologies. The SiP (System in Package) is one of the emerging technology for an effective packaging solution. In this presentation, the evolutions of packaging technologies in the IoT era is introduces. The SiP technology, assembly and testing processes and challenges are presented. The potential future packaging technology requirements and developments for IoT are discussed.

**Yifan Guo** is vice president of ASE Assembly and Test in Shanghai, ASE China. With over thirty years experience, he has performed roles in both academia and industry. He previously held positions as Professor and Adjunct Professor at Virginia Tech, State University of New York at Binghamton and University of California at Irvine. He has also worked for IBM, Motorola, Skyworks, ASE, in a variety of middle and high level management roles with responsibility for charges of R&D, engineering and operations. He holds nine patents and has published seven book chapters, and more than 50 refereed journal papers. Yifan Guo received his Ph.D degree from the Engineering Science and Mechanics (ESM) Department at Virginia Tech, and also holds an MBA from University of Redlands in California.

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

September 13, 2016

# Evolutions in IC Packaging Technologies for IoT

**BiTS China 2016**

2016.09.13

Suzhou, China

# « Agenda »

- Technology and Application Evolution

- Major Trends in Development and Demand

- Status and Challenges to Semiconductor A&T

- Summary

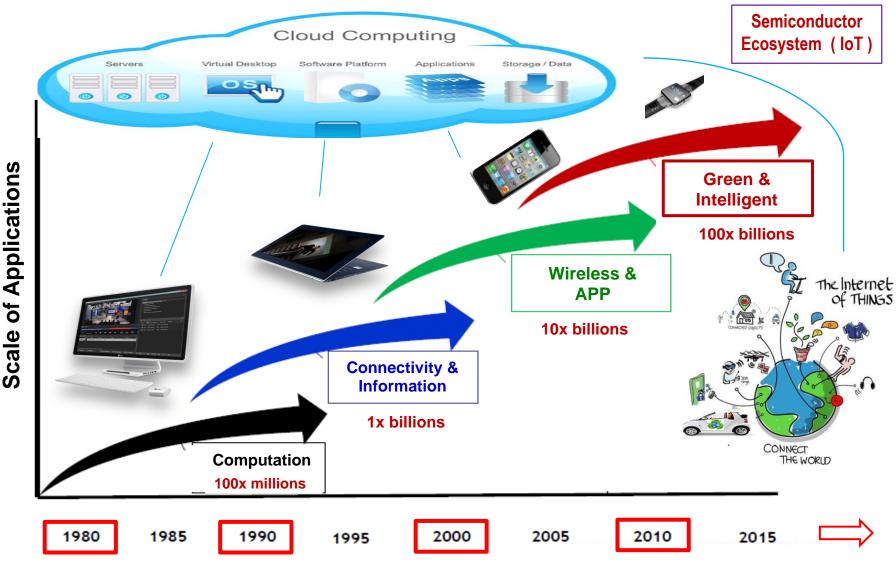

#### Paradigm Shift in Semiconductor Technology

#### Green and Intelligent are the key arears for next generations of development

3

**BiTS China 2016**

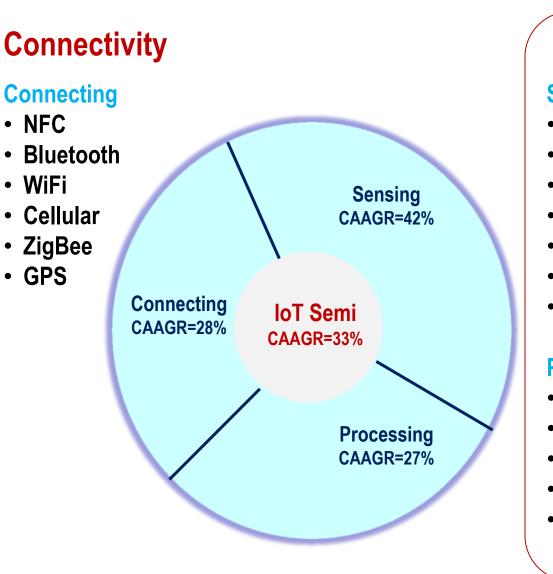

#### Semiconductor Opportunities in IoT (CAAGR)

#### Intelligent

#### Sensing

- Image Sensor

- Pressure Sensor

- Humidity sensor

- Inertial Sensor

- Magnetic Sensor

- Chemical Sensor

- .....

#### Processing

- CPU

- Application Processor

- Micro-processor

- Micro-controller

- Memory

#### **Generation of Semiconductor Technology**

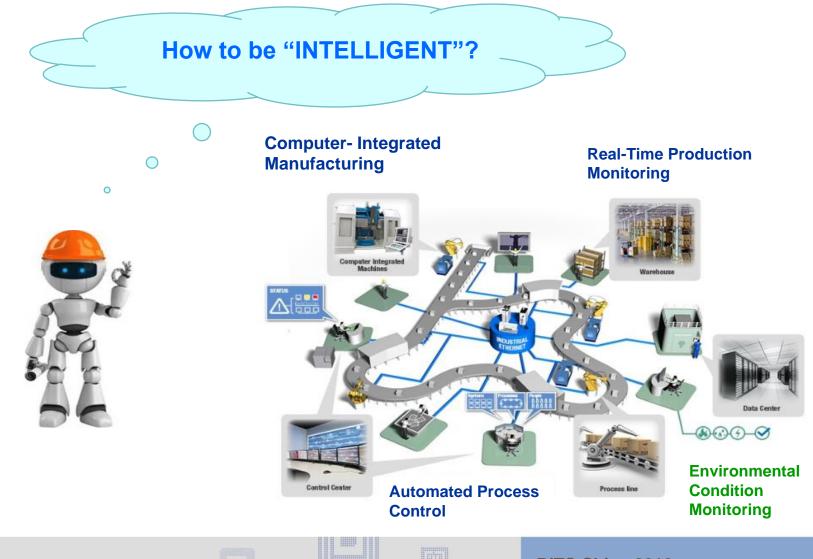

#### **Green and Intelligent are the Key Areas**

#### The Ultimate Challenge — Human Intelligence

#### **Semiconductor Technology has the Greatest Potential!**

|  | Ŕ |

|--|---|

- AlphaGo beat Lee Se-dol (李世石)

- DeepMind rises the Semiconductor Technology and Artificial Intelligence to a new level

- Integrated circuits with programs use deep neural networks

mimicking expert players and learning from games

#### Where Are We? — Competing with Human Brain

#### Human Brain

- 100B Neural Cells

- > 1M nerves (parallel connections)

- 3D structure

- ~ 20 W

#### **IBM Deep Blue**

- 500B Transistors

- ?? Interconnects (serial connections)

- 2D structure

- ~ 2000 W

- Learning and mimicking ??

#### **Understanding of Human Brain Provides Direction for Semiconductor Development**

#### We Need Breakthroughs in 3 Major Areas

- 1. Higher Speed

- 2. Better Efficiency (power)

- 3. Smaller Size

Point-contact transistor (1947) William B. Shockley AT&T Integrated circuit (1958) Jack Kilby TI

Intel 4004 CPU 1972

- 10 um process

- 2,500 transistors

Intel Xeon Phi CPU 2013

- 14 nm process

- 5 billion transistors

#### Si Technology to Address Speed, Efficiency and Size

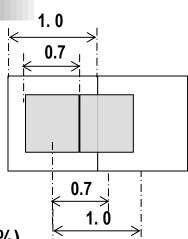

#### Moore's Law and Physical Scaling :

Every technology generation (about 2 years) :

- Density increases by 2X , # transistors increase by 2X (size)

- Reducing area by 50% and linear dimension by 0.7X (30%)

- Reducing signal delay by 0.7X (30%), increasing <u>speed</u> by 1.4X (40%)

- Reducing voltage by 0.7X (30%), improving power efficiency by 1.4X (40%)

| Generations                                                                      | 1             | 2     | 3              |     | 10    |   | 14     | 15     | 16             | 17      | 18            | 19      | 20                                             | 21            |

|----------------------------------------------------------------------------------|---------------|-------|----------------|-----|-------|---|--------|--------|----------------|---------|---------------|---------|------------------------------------------------|---------------|

| Node Size (nm)                                                                   | 10,000        | 7,070 | 4,998          |     | 441   |   | 110    | 80     | 55             | 40      | 28            | 20      | 14                                             | 10            |

| # Transistors (K)                                                                | 2.5           | 5     | 10             |     | 1,280 |   | 20,480 | 40,960 | 81,920         | 163,840 | 327,680       | 655,360 | 1,310,720                                      | 2,621,44<br>0 |

| Speed (MHz)                                                                      | 1             | 1.4   | 2              |     | 21    |   | 79     | 111    | 156            | 218     | 305           | 427     | 598                                            | 837           |

| <ul> <li>✓ Intel 4</li> <li>✓ 10 un</li> <li>✓ 2.5 K</li> <li>➢ 1 MH:</li> </ul> | n<br>Transist |       | # 749<br>INS40 | 043 |       | I |        |        | ` 1M :<br>↑ 1K |         | en de l'anace |         | Xeon Phi, 2<br>14 nm<br>5 B Transis<br>1.3 GHz |               |

After 40 years, chip is much advanced, but we still have 3 bottlenecks

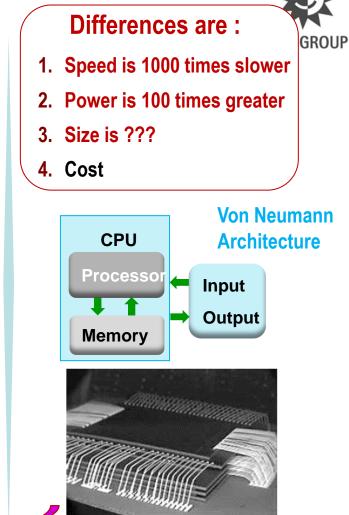

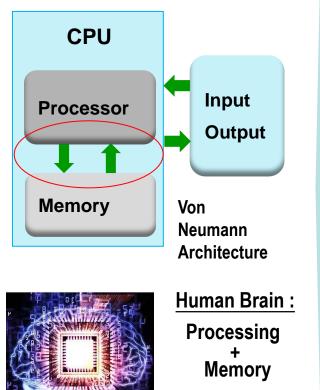

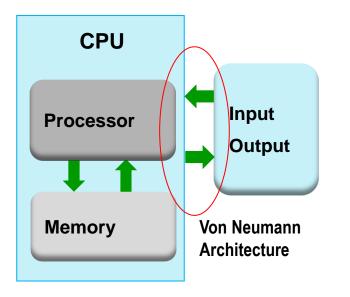

#### **Bottleneck 1 : Between Processor and Memory**

#### Von Neumann Bottleneck in Processor and Memory

**100B Neural Cells**

#### Chip Technology:

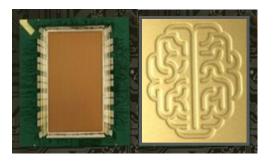

IBM SyNAPSE: Neuromorphic Chip 1 Million Neural Cells

Chip Solution: SyNAPSE : Systems of Neuromorphic Adaptive Plastic Scalable Electronics

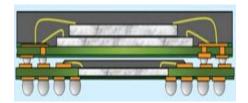

#### Packaging Tech:

- Stack / Embed

- ✓ PoP

- ✓ TSV + 3D

#### Packaging Solution:

Move processor closer to memory with more I/Os

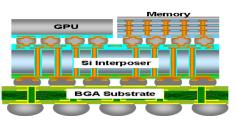

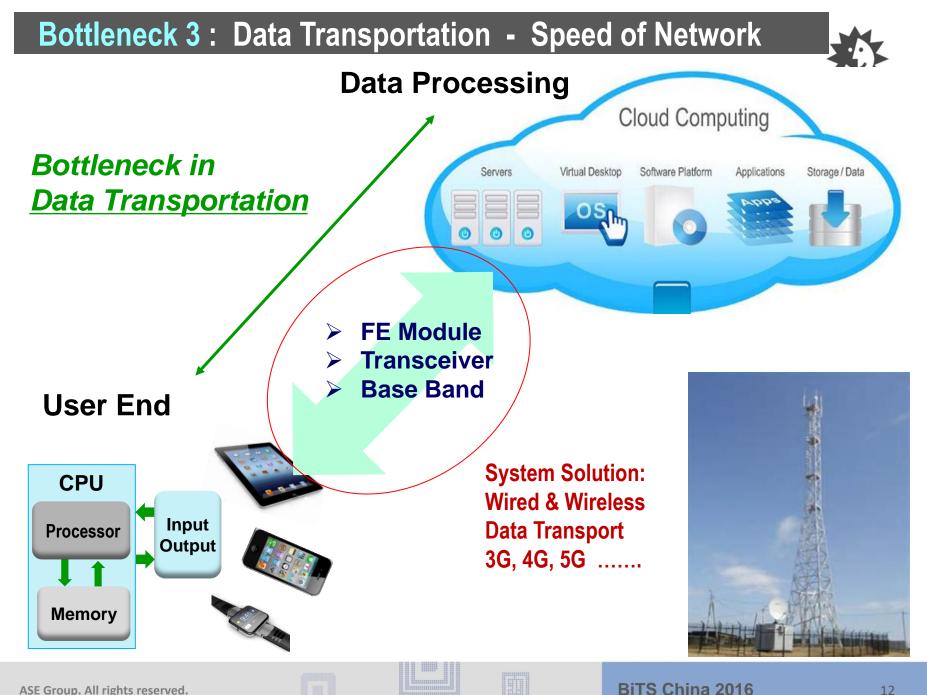

#### **Bottleneck 2 : Between CPU and Interface**

# ASE GROUP

#### Von Neumann Bottleneck in data input and output

<u>Packaging Tech:</u> Bring CPU Closer to in / output Interfaces

Chip Solution: Move CPU closer to User Interface

#### **Packaging Solution:**

- System Packaging

- Wafer Level Packaging

#### The Fan-Out Architecture of Working with the "Brain"

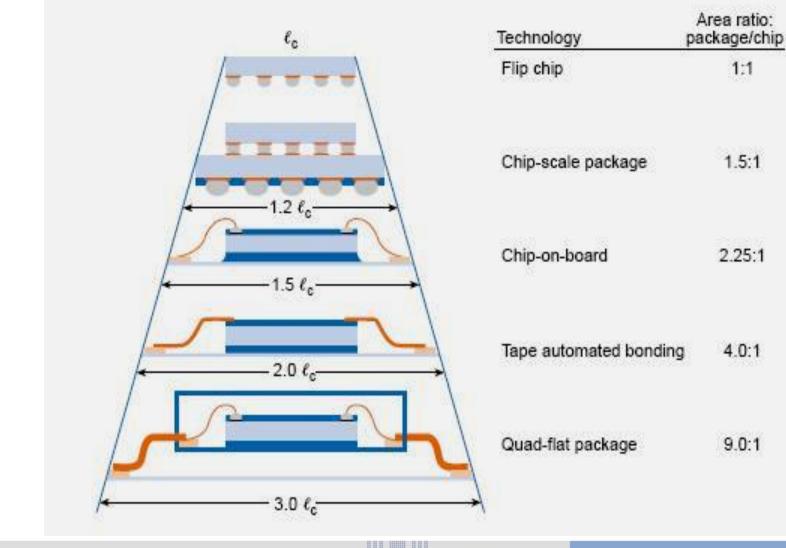

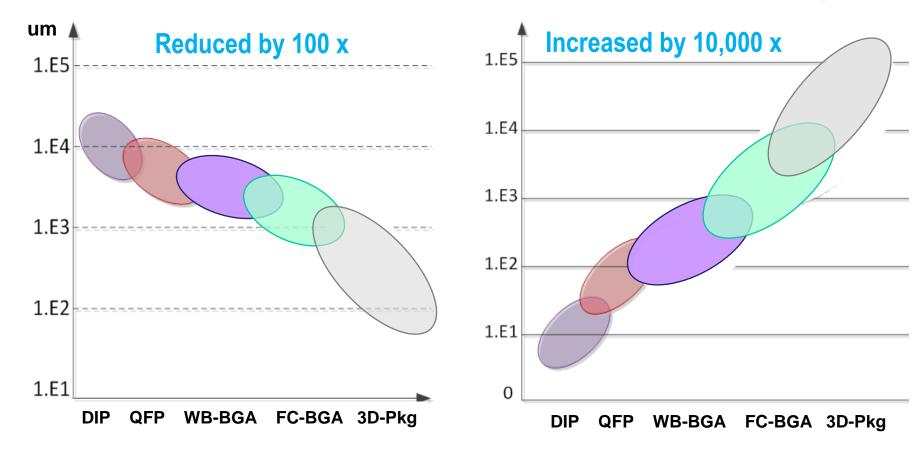

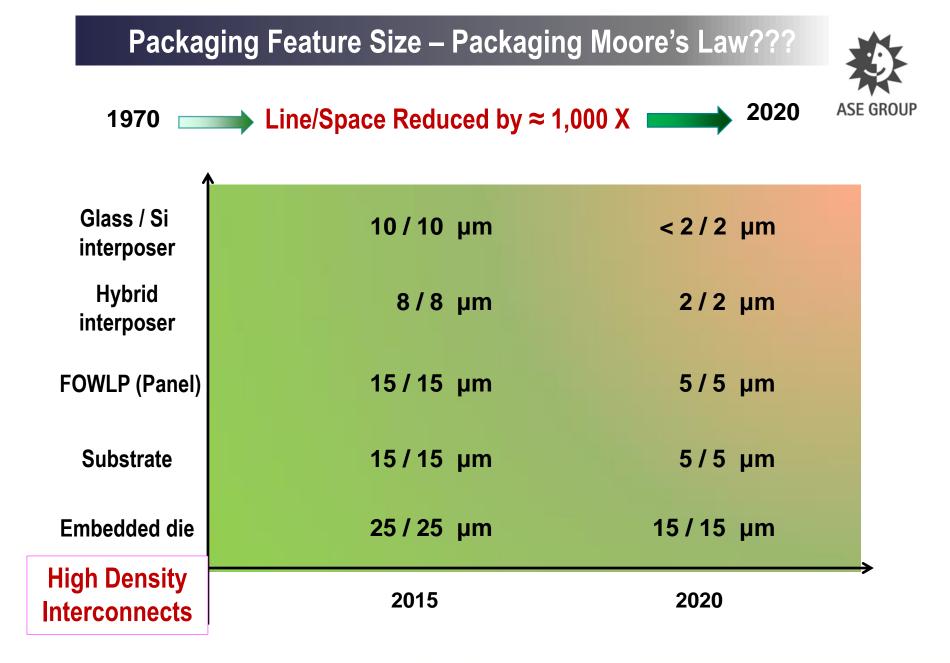

#### **Packaging Density Progression**

#### (Package Size and Signal Path Length)

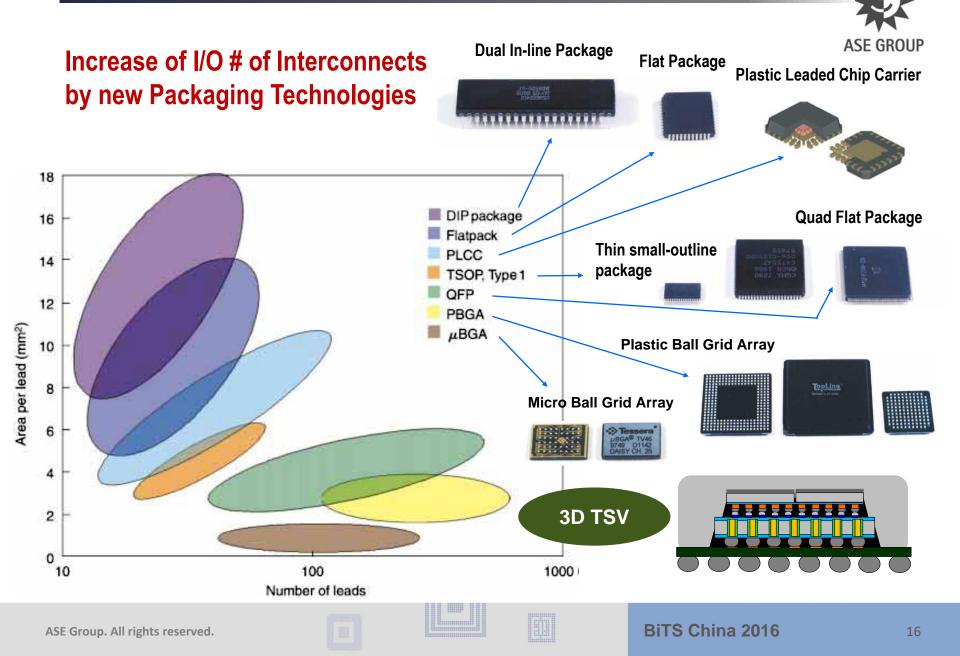

#### I/O Density Technology Improvement in Packaging

#### **Definitions of Advanced Packaging Technology**

#### Signal Path Length in Packages

# of Interconnects in Packages

#### reduces signal delay

parallel connections

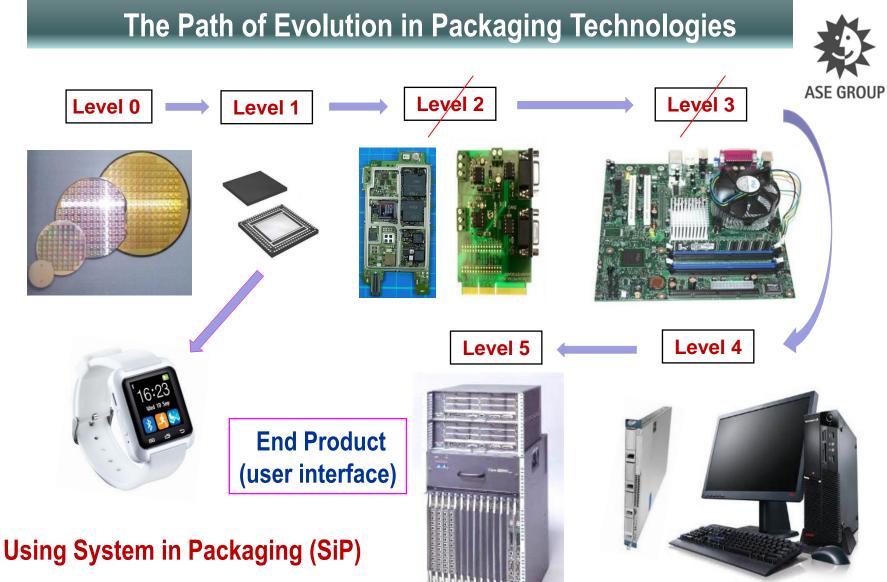

#### **3D and SiP High Density Technology Development**

**BiTS China 2016**

- Eliminating Level 2 Packaging

#### **Evolutions in IC Packaging Technology Development**

– Next System Integration ???

#### Next System Integration in Packaging Technology

#### **Heterogeneous Integration using FOWLP**

#### 2D Multi Dies FOWLP

#### **3D Multi Dies and Passives FOWLP**

#### 2D Multi Dies and Passives FOWLP

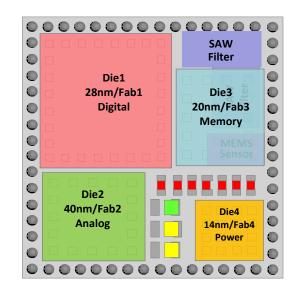

# Characteristics of IoT Solutions — Requirements to Electronic Packaging

- Holistic design and customization a complete system

- Operating SW, processor, memory, transmit, power, security ....

- Heterogeneous Integration

- Digital, analog, mixed, Si, GaAs, MEMS, optics ....

- Miniaturization and Low Cost

- WLP, SiP, IPD, stacking, embedding, shielding, CP molding ....

- Ecological System, Multi-Standards

- Regional specs, local regulations, security and reliability ....

#### Challenges

#### • Performance Challenge:

- Design and simulation becomes more complicated

- Electrical, thermal and mechanical cross-effect

- Test Challenge:

- Multi layers of functions and assembly process flow require multiple test steps, burn-in and retest

- Yield and Reliability Challenge:

- Complex design, process and materials systems affecting yield

- Higher reliability requirement for special applications and user conditions

- Tooling and Equipment Challenge:

- Verities of designs require customized tooling and equipment

- Low Cost Challenge

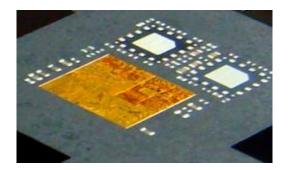

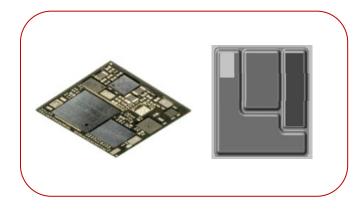

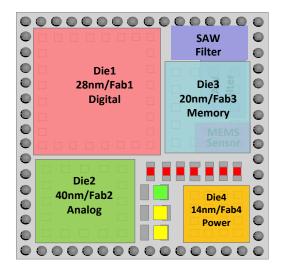

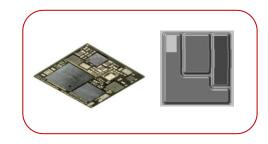

#### Advanced System in Package (SiP)

#### A big step toward IoT (wearable) applications

- Integrating Digital, Analog, RF FEM, PMIC, Memory, Sensors...

- Employed many state of art packaging technologies

- Used many new packaging processes and materials

- Very high density interconnects and L/S with many functions

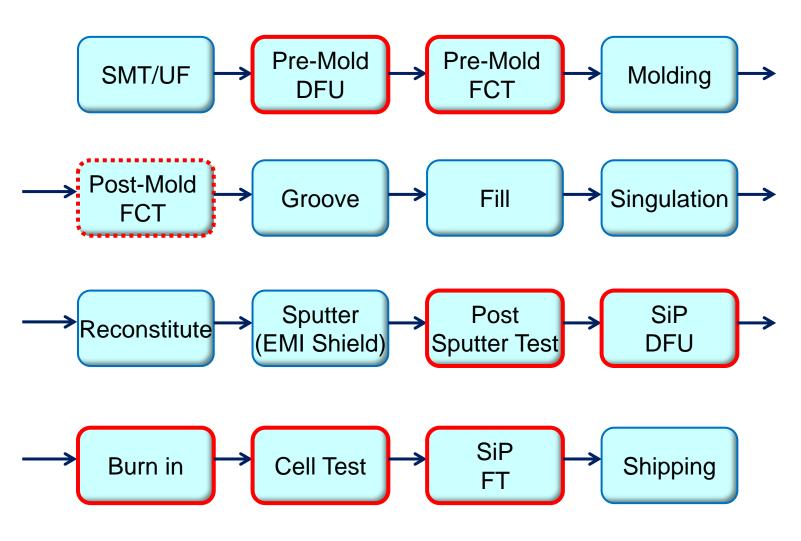

#### A Typical SiP Assembly / Test Flow (key steps)

(could be more than 50 A&T process steps)

### Challenges in Testing of SiP

- Past: BGA, QFN, SO

- CP (or blind build) + FT + (system level tests)

- Current: 3D + SiP

- PCB + CP + FCT 1,2,3...+ Burn-in + FT

Future: 3D + SiP + FOWLP - How to Test ???

# Cost Burn-in and Test will take more important role and higher cost portion in A&T for IoT applications

We know how to build it

## But how we test it ?

- Yield

- Reliability

- Cycle time

#### BITS Ch

## Next Generation of Testing Technology

#### For highly integrated systems, test becomes more critical !

#### www.aseglobal.com

#### Thank You