#### **Proceedings Archive**

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 6-9, 2016

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

2

## **Bits 2016**

## **Proceedings Archive**

**Burn-in & Test Strategies Workshop**

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

# Test Cell Thermal Solution

## Gianluca Lombardi Advantest

2016 BiTS Workshop March 6 - 9, 2016

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

March 6-9, 2016

Cell-ebrating Test - Test Cell - 1 of 2

### **Overview**

- First things first: acronyms!

- Why temperature control?

- Challenges

- Test Cell approach

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

### **Acronyms!**

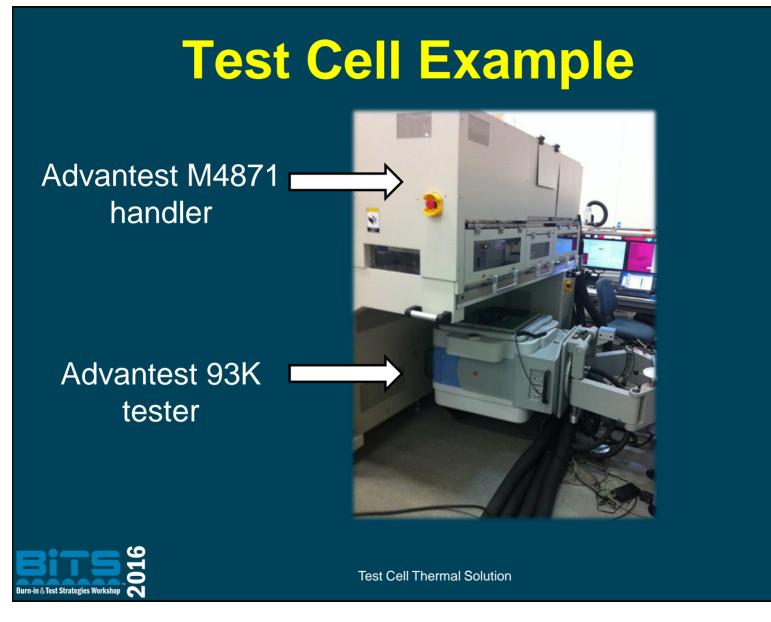

| M4871           | Advantest SoC P&P Handler        |  |

|-----------------|----------------------------------|--|

| 93K             | Advantest SoC tester             |  |

| ATC             | Active Thermal Control           |  |

| DFT             | Design For Testability           |  |

| DUT             | Device Under Test                |  |

| θ <sub>JC</sub> | Thermal resistance junction/case |  |

| TJ              | Junction Temperature             |  |

| T <sub>C</sub>  | Case Temperature                 |  |

| T <sub>P</sub>  | Pusher temperature               |  |

| T <sub>HS</sub> | Heat Sink Temperature            |  |

|                 |                                  |  |

**Test Cell Thermal Solution**

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## Why Thermal Control?

- Increasingly temp-sensitive tests

- VMIN

- FMAX/speed binning

- PMIC trimming

- IDDQ

- Deviations from desired temperature set point lead to incorrect measurements, wrong binning, resulting in either yield loss or RMAs

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **Passive/Active Thermal Control**

Passive

The control system maintains the same heat sink temperature at all times

Active

The control system changes the heat sink temperature in response to temperature variations, to more quickly supply/sink heat to/from the DUT and restore the desired temperature

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **Why Active Thermal Control?**

- Performance

- Faster response to temperature variations, everything else being equal

- Correlation

- Empirical temperature control solutions tend to lead to inconsistent yields from production site to production site

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

#### **BiTS 2016**

Cell-ebrating Test - Test Cell - 1 of 2

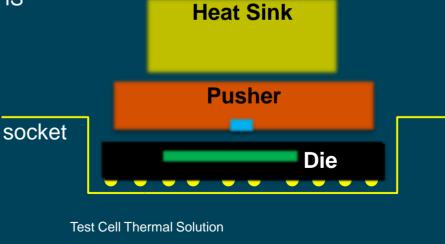

### **Thermal Stack**

Temperature control quality is the result of all the following contributors

- ATC heat sink

- Package

- Socket

- Handler change kit

- Loadboard

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **Continuity vs Thermal Contact**

Factors limiting temperature control quality w/Continuity already established

- High thermal resistance between ATC heat sink and package

- Limited or missing gimbaling

- Package --more on this in the next slide

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **Package Challenges**

- Junction/case thermal resistance,  $\theta_{JC}$

- Top side roughness/markings

- Roughness = air gaps= higher  $\theta_{JC}$

- Planarity

- Thin packages warping/flattening over  $T_J$

- Contamination

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **DUT Challenges**

- Temperature feedback availability

- Thermal diode: always

- Temp sensors: generally after initialization and ATPG

- Need additional DFT/resources

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

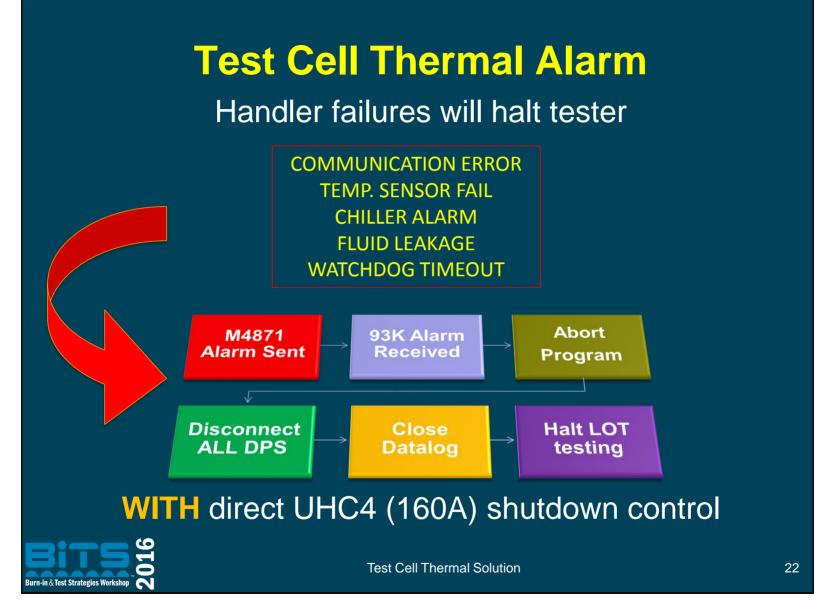

## **Test Cell Challenges**

- Socket/loadboard/DUT/tester can quickly get damaged by thermal runaways

- Must detect early signs of failure, wherever it may come from

- Even more so with high power applications, 100W and above

Test Cell Thermal Solution

11

Burn-in & Test Strategies Workshop

### **Bits 2016**

## Where to Sense DUT Temperature

- DUT thermal diode (T<sub>1</sub>) - One in the whole chip, always available DUT embedded temp sensors - Multiple available generally after init/ATPG - Temperature gradients can be quantified • Heat Sink, T<sub>HS</sub> **Heat Sink** Pusher,  $T_{P}$ ullet

- Case, T<sub>C</sub>

**Burn-in & Test Strategies Workshop**

rn-in & Test Strategies W

www.bitsworkshop.org

12

Cell-ebrating Test - Test Cell - 1 of 2

## ATC Challenges (I)

- ATC response time within milliseconds range

Limited by heat transfer time constants through stack

- Very fast DUT T<sub>J</sub> rise transients may come and go before the they get detected and corrected by best-in-class ATC

- Slow heat propagation through thermal stack

• ATC can only do so much, if the thermal stack is highly thermally resistive

– Slow to detect, slow to respond to  $\Delta T/\Delta t$

Test Cell Thermal Solution

Cell-ebrating Test - Test Cell - 1 of 2

## ATC Challenges (II)

- T<sub>HS</sub> is M4871 default T measurement source

- $T_{HS}$  may NOT follow  $T_J$  very closely

- with just 10W power being dissipated,  $T_{\rm J}$  can raise by 10-12C, while  $T_{\rm HS}$  hardly moves by 1-2C,

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

#### **BiTS 2016**

Cell-ebrating Test - Test Cell - 1 of 2

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

15

Cell-ebrating Test - Test Cell - 1 of 2

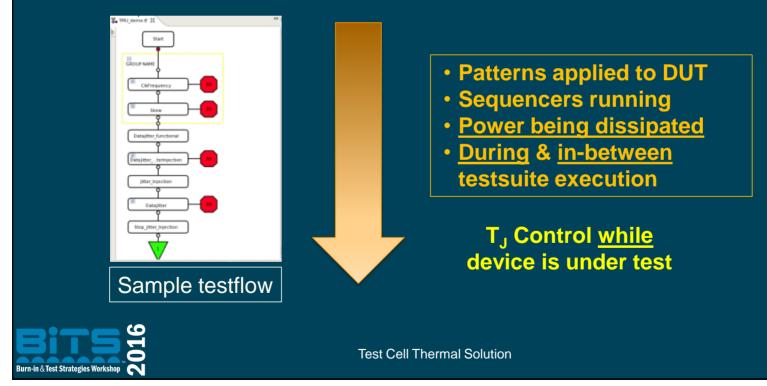

## **Real-Time Junction Control (T<sub>J</sub>)**

#### ATC CONTINUOSLY...

- Measures junction temperature T<sub>J</sub> and detects over/under shoots

- Reacts to  $\Delta T_J$  driven by <u>ALL DUT power domains</u>

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

16

Cell-ebrating Test - Test Cell - 1 of 2

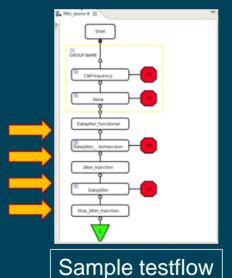

## **Supported T<sub>J</sub> Feedback Types**

93K test program controls temperature feedback signal used by M4871

- T<sub>J</sub> ANA (diff/SE)

- PWM

- I2C

Feedback mode can be changed testsuite by testsuite

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

#### **BiTS 2016**

Cell-ebrating Test - Test Cell - 1 of 2

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

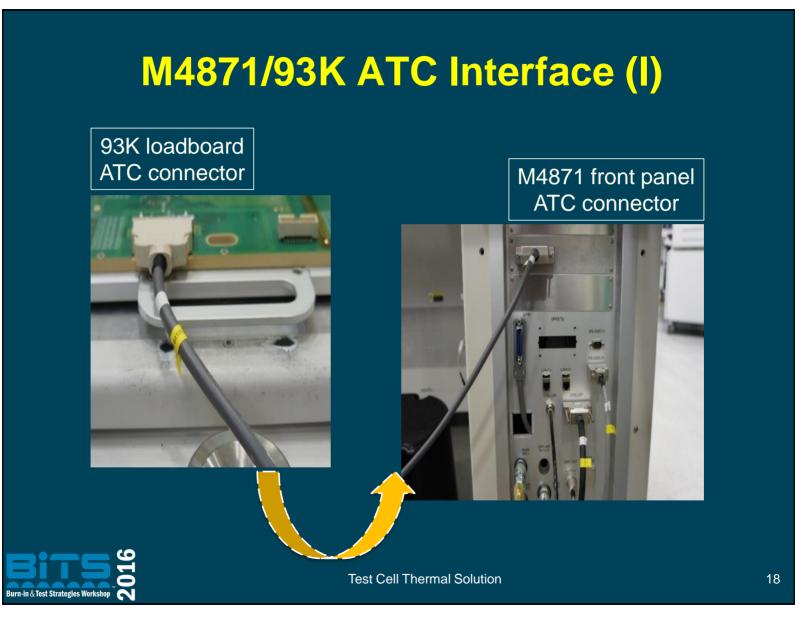

## M4871/93K ATC Interface (II)

| Signal    | Direction     |

|-----------|---------------|

| ANA_TEMP+ | Driven by DUT |

| ANA_TEMP- | Driven by DUT |

| I2C_DTA   | Driven by DUT |

| I2C_CLK   | Driven by DUT |

| PWM       | Driven by DUT |

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

## M4871/93K ATC Interface (III)

| Signal             | Direction        |

|--------------------|------------------|

| PROFILE_PRETRIGGER | Driven by 93K    |

| T-CASE_B           | Driven by 93K    |

| T-PWM_B            | Driven by 93K    |

| M4871_OK_B         | Driven by M4871  |

| UHC4_SAFETY_LINE_B | Driven by M4871  |

| CABLE_OK_B         | Monitored by 93K |

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

#### **Bits 2016**

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

**Burn-in & Test Strategies Workshop**

Cell-ebrating Test - Test Cell - 1 of 2

#### **Bits 2016**

**Burn-in & Test Strategies Workshop**

Cell-ebrating Test - Test Cell - 1 of 2

## **DUT T/V Calibration (I)**

#### Concept

- Accurate T<sub>J</sub> measurement required only during calibration

- Provided by temperature monitor IC or DUT, once per insertion

- When DUT is at set point (e.g.  $T_J = 85C$ ), thermal diode voltage  $\overline{V_{BE}}$  is measured and ATC calibrated

$\overline{V_{BE}}$  : thermal diode voltage measured when DUT @ set point

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **DUT T/V Calibration (II)**

#### Concept (cont.)

- After calibration,  $V_{BE}(t)$  is monitored by M4871

- Biasing current supplied by loadboard circuitry or tester channel

- $V_{BE}(t)$  is now the ATC feedback signal, not  $T_J(t)$

ATC will minimize  $\Delta V_{BE} = \{V_{BE}(t) - \overline{V_{BE}}\}$

Test Cell Thermal Solution

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

## **DUT T/V Calibration (III)**

#### Advantages

- Measuring is faster than calculating  $T_J(t)$

- NO add'l voltage/temp conversion required after T/V calibration

- Immune to silicon process and ESR

- Relies on accurate thermal diode ideality factor

Test Cell Thermal Solution

26

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

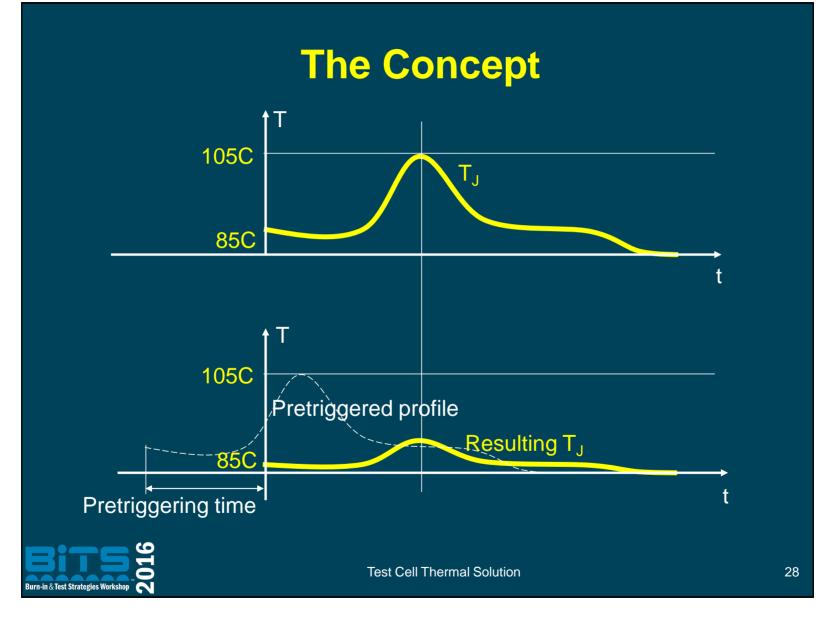

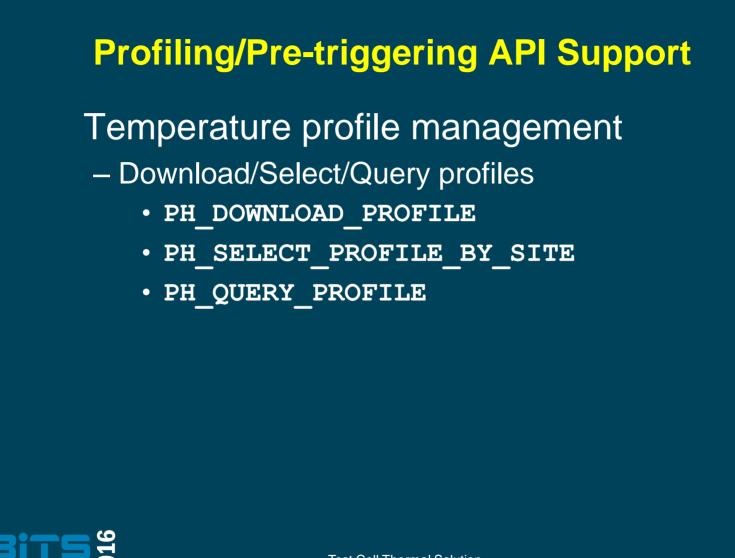

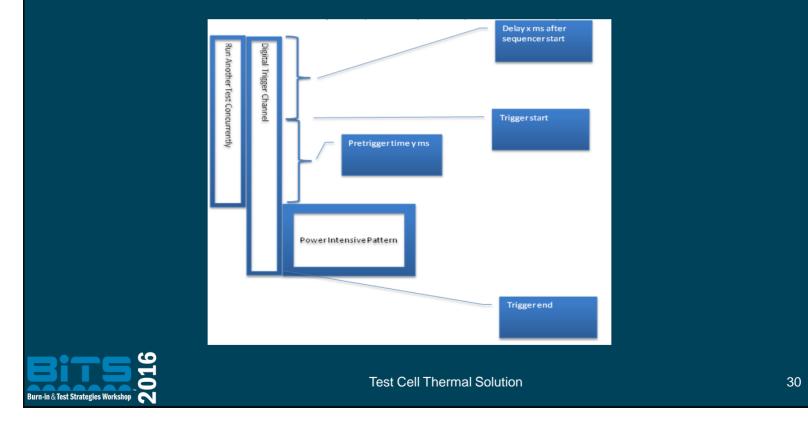

# **Profiling & Pre-Triggering**

Test Cell Thermal Solution

27

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 6-9, 2016

Cell-ebrating Test - Test Cell - 1 of 2

#### **BiTS 2016**

Burn-in & Test Strategies Workshop

Cell-ebrating Test - Test Cell - 1 of 2

urn-in & Test Strategies Works

Test Cell Thermal Solution

Cell-ebrating Test - Test Cell - 1 of 2

### **Profiling/Pre-triggering TML Support**

Zero-overhead  $\rightarrow$  hides pre-triggering time behind low power pattern

Burn-in & Test Strategies Workshop