# **Proceedings Archive**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

## **BiTS 2016**

# **Proceedings Archive**

Session 5

Ashok Kabadi Session Chair **BiTS Workshop 2016 Schedule**

# Performance Day

Tuesday March 8 - 10:30 am

## **West Meets East & Cutting Edge**

"LPDDR4 Signal & Power Performance Optimization By Hardware"

"通过测试硬件的优化来提升LPDDR4信号和电源的性能"

Yuanjun Shi - Twinsolution Technology Xiao Yao - HiSilicon Technologies Co

"Reliability Characterization of Unpackaged (bare) die for Silicon Photonics module"

Sujata Paul, Andrew Fong, Samir Alqadhy, Huy Nguyen, Zoe Conroy - Cisco Tom Elliot, Jag Jassal - Evans Analytical Group

"Advanced High Energy CO2 Spray Cleaning Technology for Burn-In Test Substrate Cleaning Applications"

Nelson Sorbo - Cool Clean Technologies

"Texas Instruments Final Test Contactor Qualification Process and Low Profile Contactor Solution"

James Tong, Hisashi Ata - Texas Instruments

# Texas Instruments Final Test Contactor Qualification Process and Low Profile Contactor Solution

James Tong, Hisashi Ata Texas Instruments

2016 BiTS Workshop March 6 - 9, 2016

## **Contents**

- What's the Problem?

- Problem Statement

- Technical Solution and Challenges

- Learning the Pin Type

- Learning the Pin Design

- Learning the BGA contactor design

- Learning the QFP contactor design

- TI contactor qualification process

- Step1: Vendor's factory evaluation

- Step2: TI technical qualification

- Step3: TI production qualification

- Step4: Qualification data review and deployment

- Summary

- Acknowledgements

## **Problem Statement**

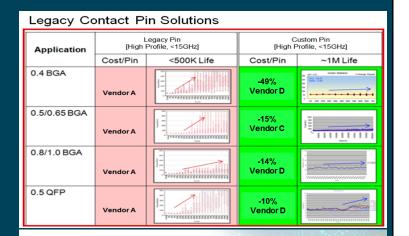

- Legacy contact technologies cannot support today's test application requirements.

- Different approach to deal with the short fall from every A/T sites

- Incompatibility performance

- Localized support to each A/T site

- yield correlation problem

- Multi-factories loading limitation.

- Resulting in customized pin design by device by user.

- Work against cost reduction model to benefit TI worldwide

#### Strategy

2014 Execute and gain share

- √ High Performance pins

- Low Cres

- High CCC (Current Carrying Capability)

- High bandwidth

- √ Common use across tester platforms, pin pitches and

#### A/Ts

- → Volume pricing

- → Sameness across A/Ts

- √ Low COO (Low Cost, Long Life > 1,000K insertions)

- ✓ PCB footprint compatibility

- √ WW TI support

Texas Instruments Final test Contactor qualification process and low profile contactor solution

# **Technical Solution and Challenges**

#### **Solution**

- Shorter pin resulting in less metal between the load-board and the Device-Under-Test (DUT)

- Lower pin inductance

- Better signal integrity

### **Challenges**

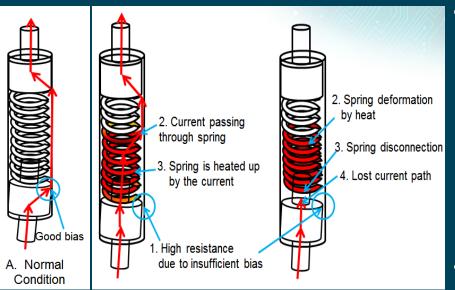

- High current carrying capability (CCC)

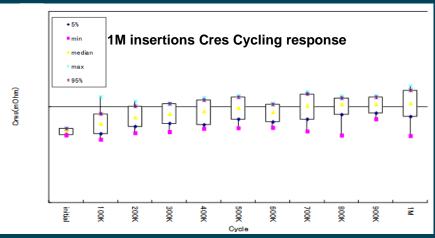

- Reliable contact resistance (Cres)

- Pin manufacturability: Low cost

Texas Instruments Final test Contactor qualification process and low profile contactor solution

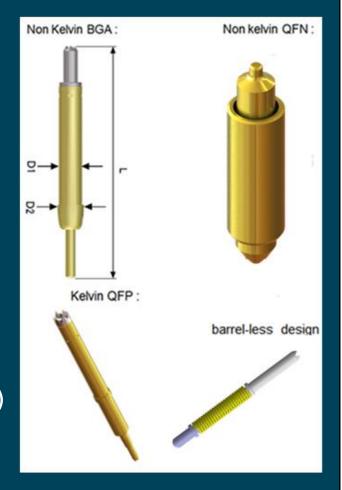

# **Learning the Pin Type**

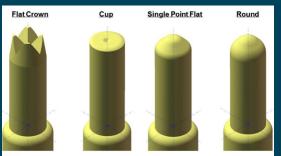

- Unlimited tip shape and design.

- Tip material: Homogenous, plated core material, etc.

- Barrel: diameter and plating thickness

- Spring design and material: Total force, life, contact reliability and temperature rating

- Biasing mechanism

- CRes, CCC, spring performance and lifetime

- Bottom Plunger design

- Material

- Unlimited Shape

- Plating recipe

- PCB pad damage

# **Learning the Pin Design**

- Top plunger design → contact reliability & DUT contact surface damage

- Shape and volume of material → Wear rate / life

- Material composition → contact reliability and life

- Bottom plunger design → reliability of the pin internal structure

- Shape

- Plating thickness / material

- Spring force / material

- Biasing method

- Define the CCC performance

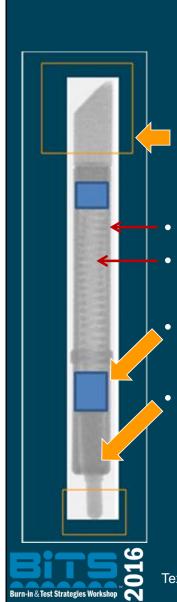

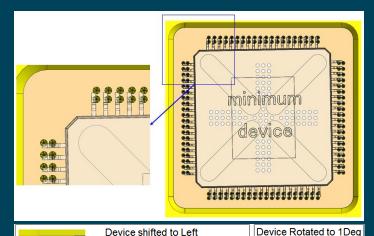

# Learning the BGA Contactor Design

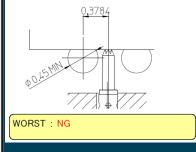

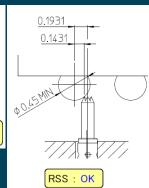

WORST: 0.3729

RSS: 0.2326

Condition 1

TFND Guide: 27.152mm MAX

Device Guide: 24.127mm MAX

NEST (Out side): 27.07mm MIN

NEST (In side): 24.15mm MAX

- Nest guide > coarse alignment

- BGA Package guide provides the final alignment

- Positional simulation –

RSS

#### Condition 2

: 0.01\*√2 1. Alignment hole of Guide true position : 0.02 2. Alignment hole of Guide VS Dowel pin : 0.01\*√2 3. Dowel pin for Plate true position : 0.01\*√2 4. Alignment hole of Plate true position : 0.0125 5.Alignment hole of Plate VS Dowel pin : 0.01\*√2 6.Dowel pin for Pin Block true position : 0.01\*√2 7.Probe hole true position : 0.0175 8. Probe tip accuracy : 0.2272 9.PKG shift length

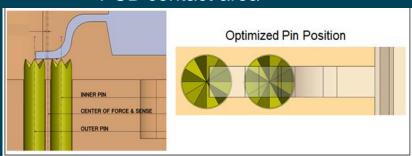

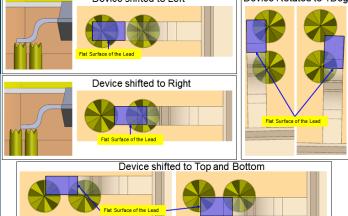

# Learning the QFP Contactor Design

- Dual pin strategy

- Common use for Kelvin and non-Kelvin application

- Kelvin Force/Sense

- Non-Kelvin Mechanical and Electrical redundancy

- Pin gap: Smaller the better

- Contact position: Optimized

- Flat area of the lead contact

- PCB contact area

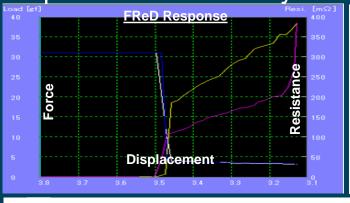

Step 1. Vendor's factory evaluation (1)

- Vendor's Pin reliability performance

- FReD chart

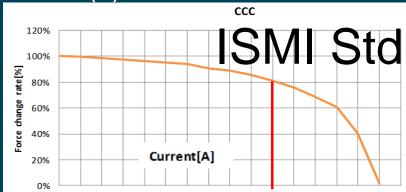

- Current capability based on ISMI test method

- Contact resistance stability

Step 1. Vendor's factory evaluation (2)

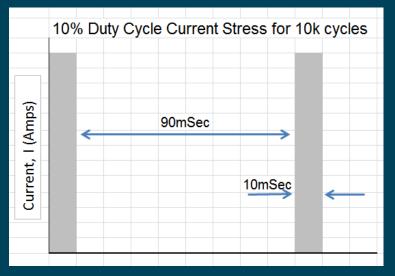

- Electrical Stress Test

- Stress pin thru high current

- ➤ Pass → Force drop less than 20% and no discoloration / burned tips

- Emulate device test application

| Current (A) | # of pulses | On time (ms) | Off time (ms) | Duty Cycle | Temp(C) | pin force (gf) | Result |

|-------------|-------------|--------------|---------------|------------|---------|----------------|--------|

| 7           | 1           | 10           | 90            | 10%        | 32.5    | 24.7           | OK     |

| 7           | 1           | 10           | 90            | 10%        | 31      | 25.3           | OK     |

| 7           | 100         | 10           | 90            | 10%        | 30.6    | 24.8           | OK     |

| 7           | 1,000       | 10           | 90            | 10%        | 40.9    | 23.3           | OK     |

| 7           | 2,000       | 10           | 90            | 10%        | 41      | 21.7           | OK     |

| 7           | 5,000       | 10           | 90            | 10%        | 39.7    | 22.9           | OK     |

| 7           | 10.000      | 10           | 90            | 10%        | 42      | 23.7           | ок     |

Texas Instruments Final test Contactor qualification process and low profile contactor solution

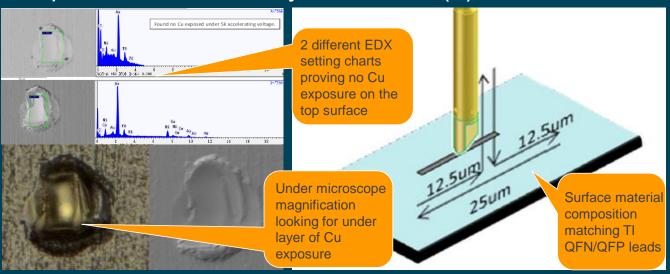

Step 1. Vendor's factory evaluation (3)

- Mechanical contact wear simulation

- Effect of tip shape

- pin wear rate

- Cu exposure / damage on DUT pads/leads

Texas Instruments Final test Contactor qualification process and low profile contactor solution

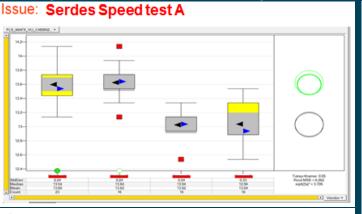

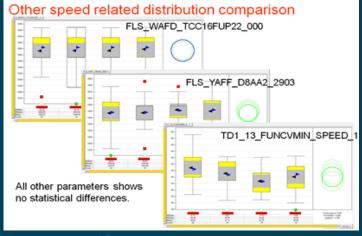

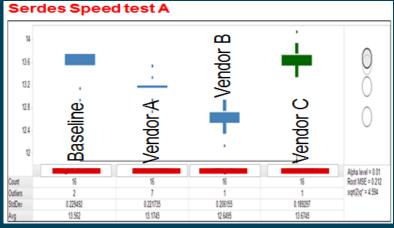

Step 2. TI technical qualification

- Serdes loop back test is a good test method to validate solution w.r.t. it's speed characteristic (High Speed Digital)

- Adopted this form of test method to ensure that qualified solution will be able to deliver the promised performance

Texas Instruments Final test Contactor qualification process and low profile contactor solution

Reduce to 1

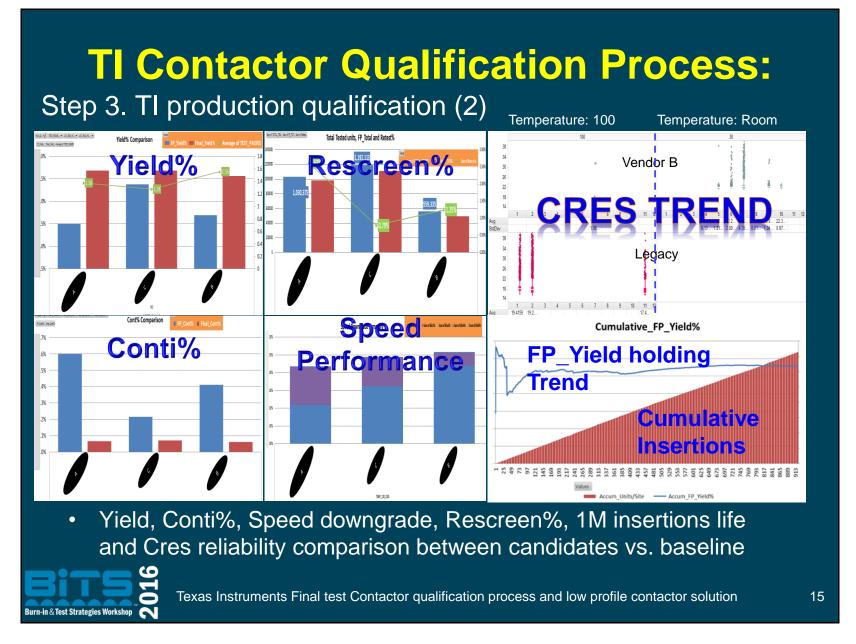

# **TI Contactor Qualification Process:**

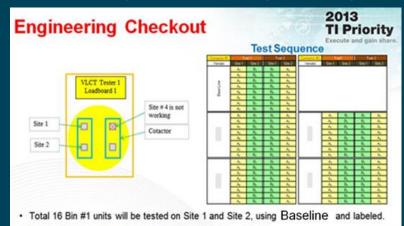

Step 3. TI production qualification (1)

- Engineering Evaluation

- Prove in using actual device

- Production qualification in A/T site (Volume data and lifetime)

- Yield, Miss-contact, lifetime, etc.

| **  |            | Parameter                | Units            |                    |        |          |                | . '           | ı voc           | iuc              | C                    | U        |             |                            |

|-----|------------|--------------------------|------------------|--------------------|--------|----------|----------------|---------------|-----------------|------------------|----------------------|----------|-------------|----------------------------|

| 1   |            |                          | Manufacture      |                    |        |          |                |               | Pin solution    |                  |                      |          |             |                            |

| 2   | SS         |                          | Pin Model #      |                    |        |          | >              | ļ '           | i ili solution  |                  |                      |          |             |                            |

| 3   | Class      |                          | Package          |                    |        |          |                | per vendor    |                 |                  |                      |          |             |                            |

| 4   | ٦          |                          | Pin Use          |                    |        |          | No             | n)            |                 |                  |                      | Τ.       |             |                            |

| 5   | 4          |                          | Status           |                    |        | A        | \_             | s 🛭 🗸         |                 |                  |                      |          |             |                            |

| 6   | Cost       | Price/pin                | US\$             |                    | P      | F        | Y              |               | Lotary          |                  |                      |          |             |                            |

| 7   | اں         | Price/DUT Pin            | US\$             |                    | II re  | a        |                | 1             | - 40 a          | 5 55             |                      |          |             |                            |

| 8   | _          | Socket Cost              | US\$ ea@ 8 pcs   |                    |        | ľ        | 0              | V             | 100             | 9 M              |                      |          |             |                            |

| 9   |            | V-U CDU                  | Pin Drawing#     |                    |        | ٠,       |                | ľ             | <b>\</b>        |                  |                      |          |             |                            |

| 10  |            | Working CPH              |                  | mm 3.30            |        | +        | 3.30           | 1             | 3.30            | +                | 3.30                 |          | ł           |                            |

| 2   | g          | Force @ cph<br>Min Pitch | grams            | 20 25<br>0.4 0.4   |        | 0.4      | 25 24.5<br>0.4 |               |                 | _                | $H^{-}$              |          |             |                            |

| 3   | Mechanical | PCB Pre-Load             | mm               |                    | 0.20   |          | 0.4            | $\rightarrow$ | <b>/</b>        | +                | 0.4                  |          |             |                            |

| 14  | 죕          | DUT                      | mm               | 0.20               |        | +        | 0.20           | $\dashv$      |                 | +                | 0.25                 | _        | t           |                            |

| 15  | ec         |                          | (PCB Side)       |                    | Radius |          | Radiu          | 5             | Flat-4          |                  | vn-roun              |          |             |                            |

| 6   | ĮΣ         | Tip Shape                | (Dut Side)       | 4 Pts Crown        |        | , †      | 4 Pts Cro      | $\rightarrow$ |                 |                  | pt cro               |          | t           |                            |

| 17  |            | Temp                     | Deg C            | -55 to 130<br>N.A. |        | _        | -40 to 1       | _             | -50 to 1        | 50               | to 155               |          | İ           |                            |

| 18  |            | Kelvin F/S Pin           | mm               |                    |        | $\top$   | N.A.           |               | NA              |                  |                      | Ť        |             |                            |

| 19  |            | Cres                     | mOhm             | 60<br>3            |        | $\top$   | 50             | $\neg$        | ~51             |                  |                      | Ť.       |             |                            |

| 20  |            | 000                      | Amps             |                    |        | $\dashv$ | 2.75           |               | 27              |                  | 2                    |          | Ť.          |                            |

| 21  | 恧          | Induct Self              | nH —             |                    | Suppli | - Pitch  | Metal C        | Pin Tes       | DUT /           | OCC Cor          | Mis-                 | t Combon | Comments    |                            |

| 22  | ĕ          | Induct Mutual            |                  |                    | Pin PN |          | er (mm)        | / Plat        | ing Height (mm) |                  | PCB TIP<br>Shape     |          |             | PPM                        |

| 23  | Electrical | Cap Gnd                  | pF               |                    |        | 0.4      | BeCu           | /Au 5.05      | Crown           | 4.75<br>1.09     | 2.9K                 | 500K     | ien Purpose |                            |

| 4   | Ē          | Cap Mutual               |                  |                    | a      |          | 10.4           | Locu          | , ,             | Crown            | 0.10                 | aJK      | SSOR        | pen r'urpose               |

| 25  |            | Insertion Loss           | GHz @ -1dB       |                    | b      | ١¥       | 0.5/.65        | BeCu          | / Au 5.2        | Crown<br>Crown   |                      | 1.24K    | K 500K      | ien Purpose                |

| 26  |            | Return Loss (S11)        | GHz @ -20dB      |                    |        | /endor A | -              |               |                 |                  | 0.10<br>3.85<br>0.94 |          |             |                            |

| 27  |            | DUT Tip                  | Plating Material | 411                | C      | \<br>e   | 0.5/.65        | Au Al         | lloy 5.2        | 2 Crown<br>Crown | 0.94<br>1.00<br>0.05 | 436      | 700K        | Low CRES                   |

| 28  | -          |                          | ip Base Material |                    |        |          | 0.61.05        | BeCu / A      | /Au 5.2         | Crown            | 8.40                 | 436      | 70016       |                            |

| 9   | Chemical   |                          | Plating Material |                    | d      |          | 0.5/.65        | веСи          | / Au 5.2        | Crown            | 0.10                 |          | 700K        | en Purpose                 |

| 30  | E          |                          | ip Base Material |                    | е      | В        | 0.5/.65        | BeCu          | /Au 5.2         | Crown<br>Crown   | 2.32<br>0.71<br>2.00 |          | 700K        | Drop In<br>Replacement     |

| 31  | ٤          |                          | Spring Matl      |                    |        |          |                |               |                 | Cionii           | 0.30<br>7.50         |          |             | Drop In                    |

| 2.7 | ٦          |                          | Housing Matl     | Va                 | f      | С        | 0.5/.65        | BeC<br>NiRh+l | u /<br>ECC 5.3  | Crown<br>Crown   | 2.20                 | 2.87K    | 1600K       | Replacement<br>(High Cycle |

Texas Instruments Final test Contactor qualification process and low profile contactor solution

14

Test unit (A1 to A8) on Site 1 and unit (B1 to B8) on Site 2.

Re-test unit (B1 to B8) on Site 1 and unit (A8 to A1) on Site 2.

Repeat the same test sequence for Vendor A and B Contactors.

#### **BiTS 2016**

Cutting Edge - Advanced Technology / New Approaches

# **TI Contactor Qualification Process:**

Step 4. Qualification data review and deployment

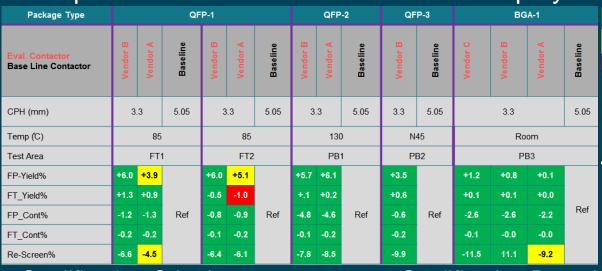

#### **Qualification Criteria**

- ✓ Cost

- ✓ Improved Performance (FP\_Yield, FP\_Conti%, Rescreen% & Pin life)

- ✓ Onsite Support

#### **Qualification Boundary**

- ✓ Temperature

- ✓ Pitch

- ✓ Test current

- √ Ω Trend (RDsOn/Cres)

- ✓ Test frequency / bandwidth

Texas Instruments Final test Contactor qualification process and low profile contactor solution

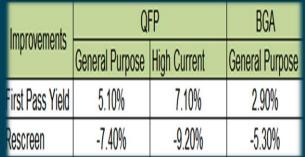

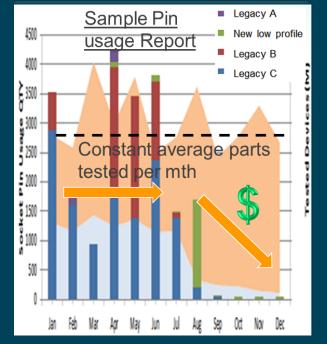

**Summary**

- Established a robust systematic qualification process

- Performance improvement

- First Pass Yield improvement of 5%

- Rescreen rate drops of 6%

- √ Capacity recovery

- ✓ Cost saving on labor and test equipment

- Achieving 1M or more insertion of Pin life

- Cost saving from pin usage

- Intangible labor cost saving

- Other intangible benefits

- Better Yield correlation

- Shorter Device start up time

- Factories loading flexibility