# **Proceedings Archive**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

#### **BiTS 2016**

### **Proceedings Archive**

Session 5

Ashok Kabadi Session Chair

**BiTS Workshop 2016 Schedule**

# Performance Day

Tuesday March 8 - 10:30 am

#### **West Meets East & Cutting Edge**

"LPDDR4 Signal & Power Performance Optimization By Hardware"

"通过测试硬件的优化来提升LPDDR4信号和电源的性能"

Yuanjun Shi - Twinsolution Technology Xiao Yao - HiSilicon Technologies Co

"Reliability Characterization of Unpackaged (bare) die for Silicon Photonics module"

Sujata Paul, Andrew Fong, Samir Alqadhy, Huy Nguyen, Zoe Conroy - Cisco Tom Elliot, Jag Jassal - Evans Analytical Group

"Advanced High Energy CO2 Spray Cleaning Technology for Burn-In Test Substrate Cleaning Applications"

Nelson Sorbo - Cool Clean Technologies

"Texas Instruments Final Test Contactor Qualification Process and Low Profile Contactor Solution"

James Tong, Hisashi Ata - Texas Instruments

# LPDDR4 Signal & Power Performance Optimization By Hardware

Yuanjun Shi / Twinsolution R&D Xiao Yao / Hisilicon Test Solution R&D

2015 BiTS Workshop Shanghai October 21, 2015

#### **Contents**

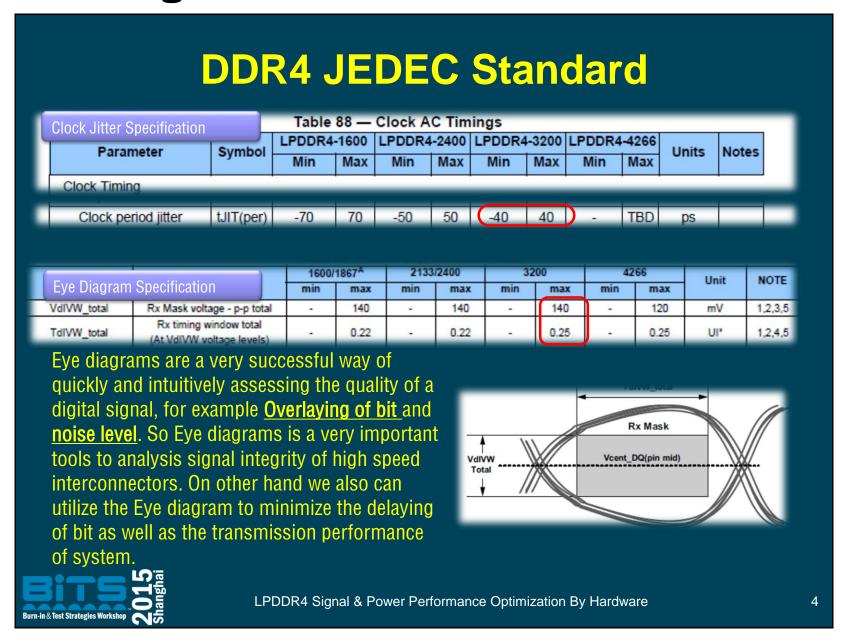

- DDR4 JEDEC Standard

- LPDDR4 PCB Channel & Socket SI Simulation

- LPDDR4 PCB and Socket Power Integrity Simulation

- Summary

#### **DDR4 JEDEC Standard Description Symbol Type** JEDEC Standard No. 209-4 CK\_t\_A, CK\_c\_A, Input Clock CK\_t\_B, CK c B 2XX-ball 15mm x 15mm CA[5:0] A Command/Address Input 0.4mm pitch, Quad-Channel CA[5:0] B Inputs POP FBGA (top view) Data Input/Output: DQ[15:0]\_A, 1/0 Bi-direction data DQ[15:0] B bus. Partial Enlarge Map of DDR DQS[1:0]\_t\_A, DQS[1:0]\_c\_A, 1/0 Data Strobe ZQ1 a DQ15\_a DQ13 a DQS[1:0] t B, DQS[1:0] c B This case only study one group signal pin VDDQ, across all four group signal pins, and only VDD1. Supply **Power Supplies** include DQ pin. VDD2 VSS, VSSQ **GND** GND LPDDR4 Signal & Power Performance Optimization By Hardware 3

# LPDDR4 PCB Channel & Socket SI **Simulation**

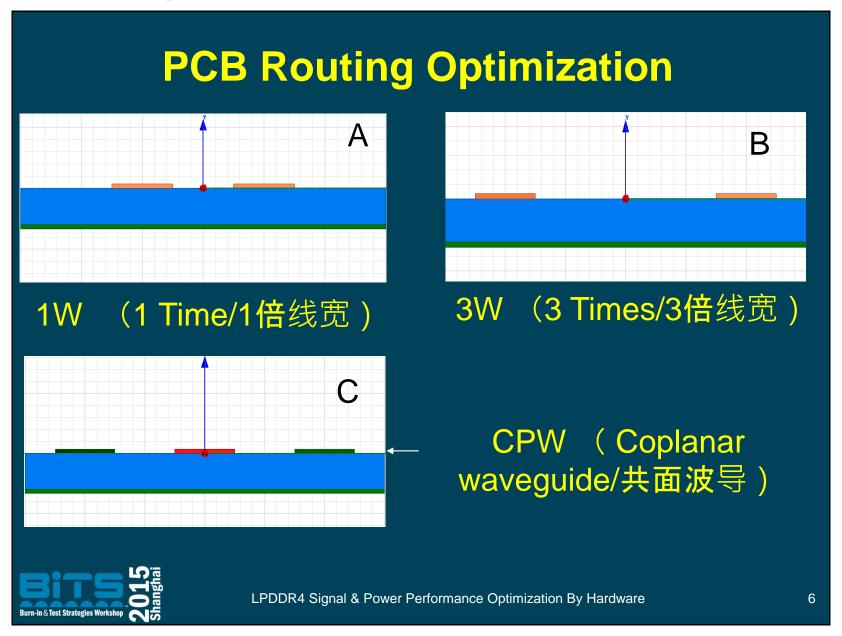

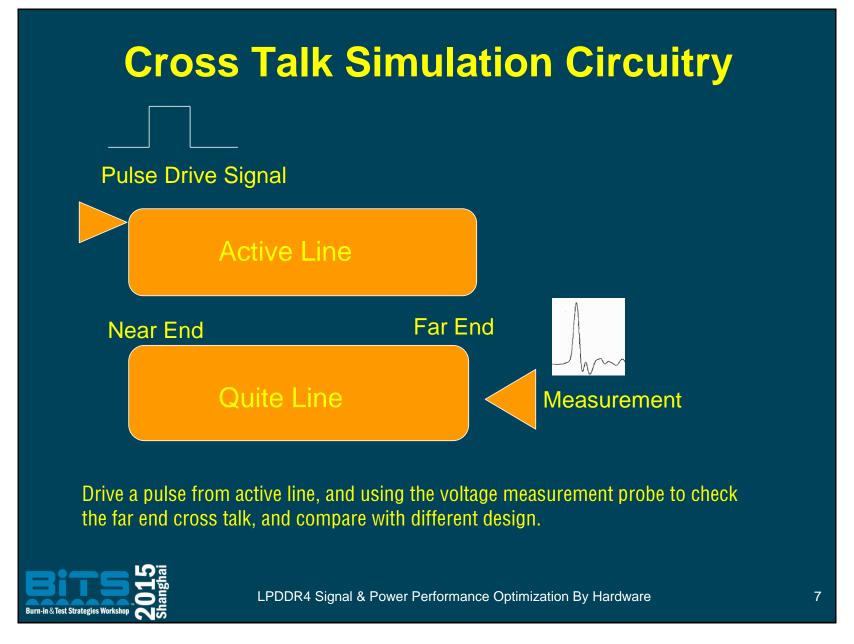

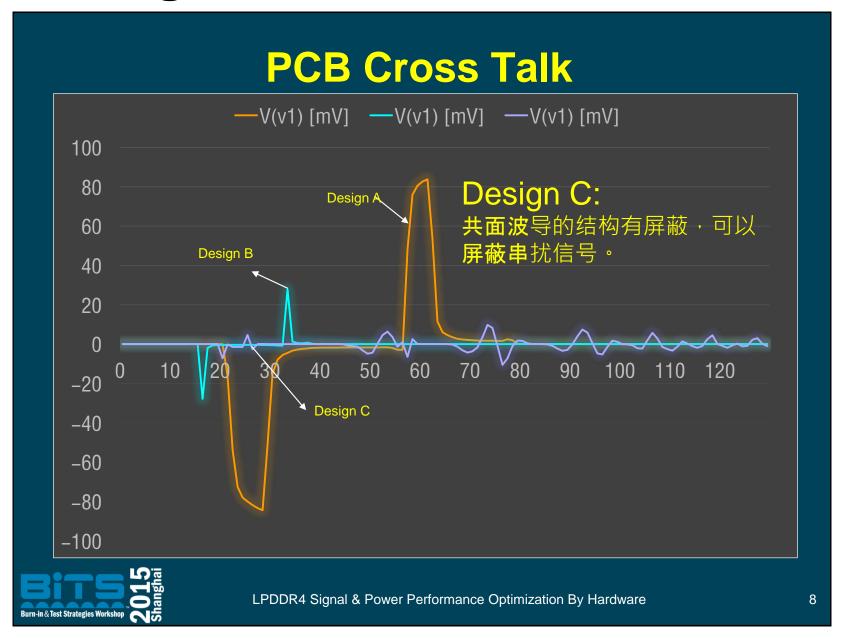

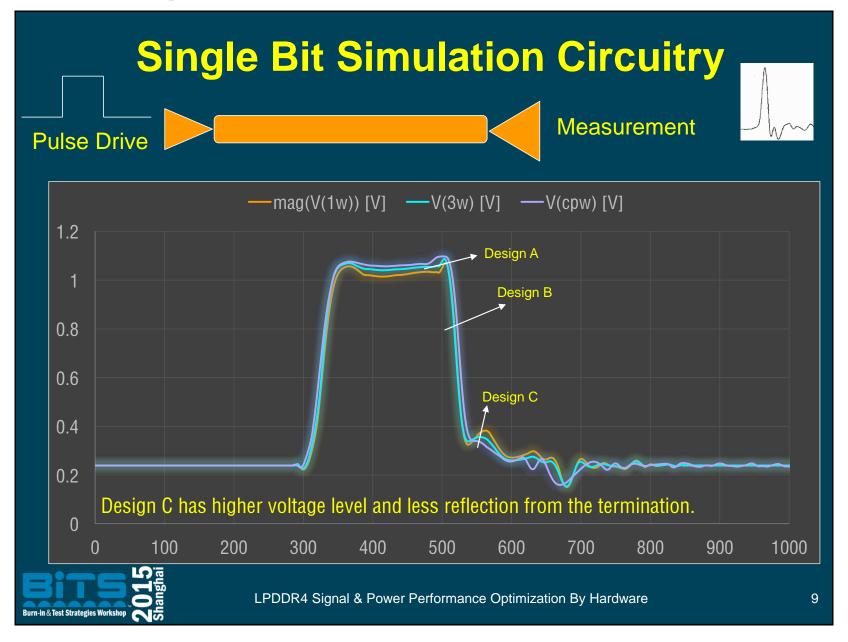

- PCB routing optimization

- Single Bit Performance

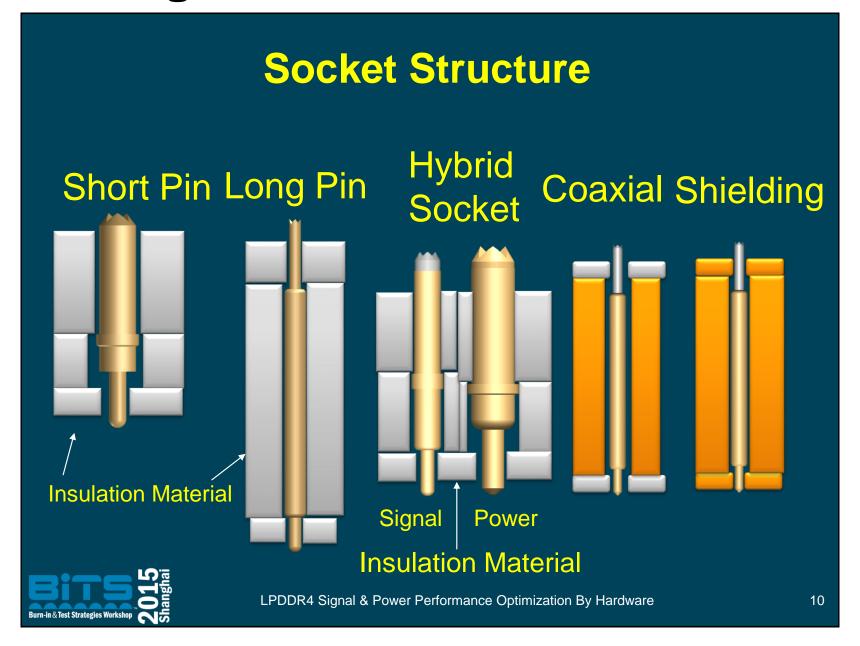

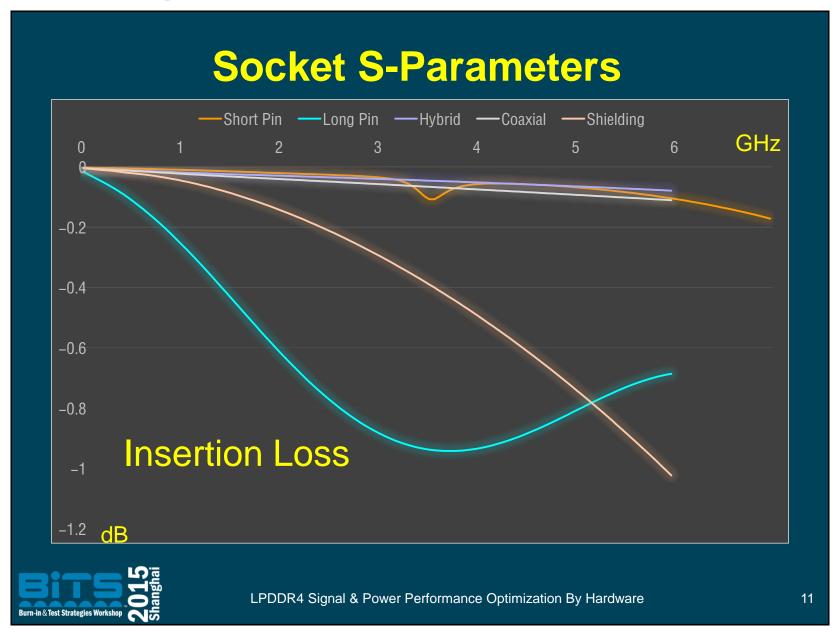

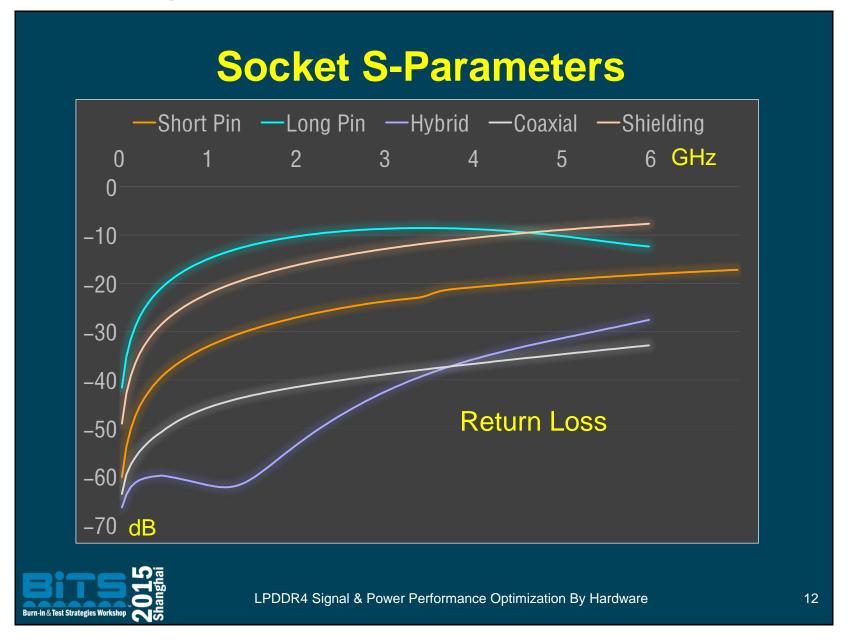

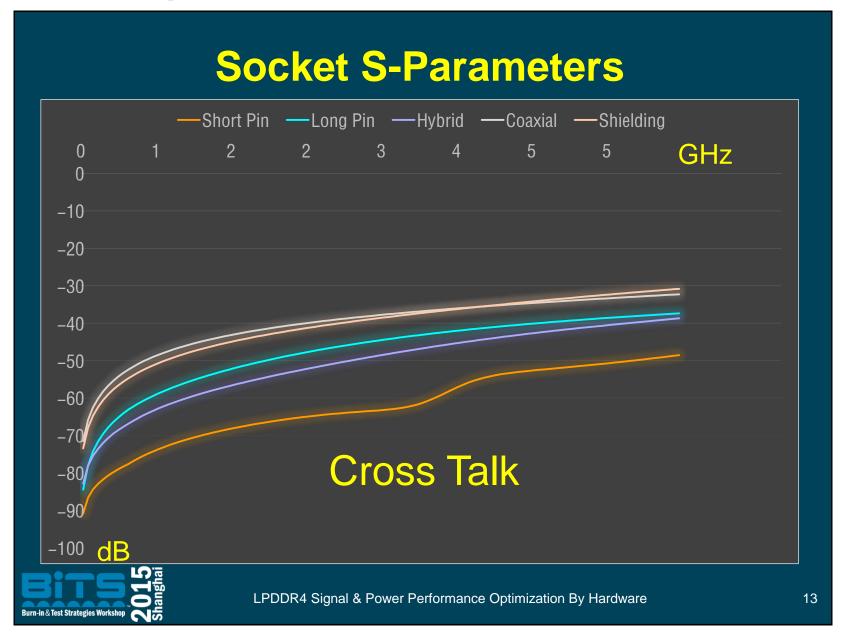

- S-Parameter Comparison Across Different Socket Structure

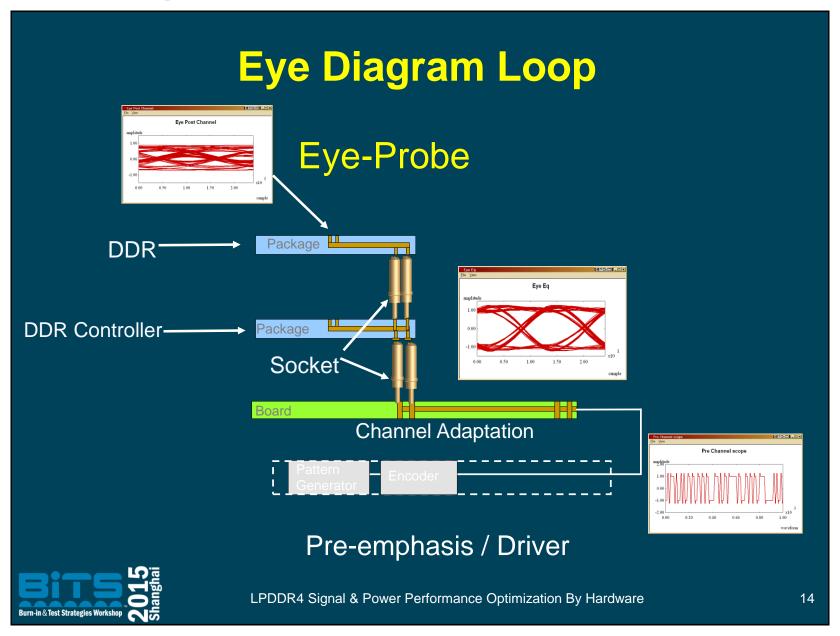

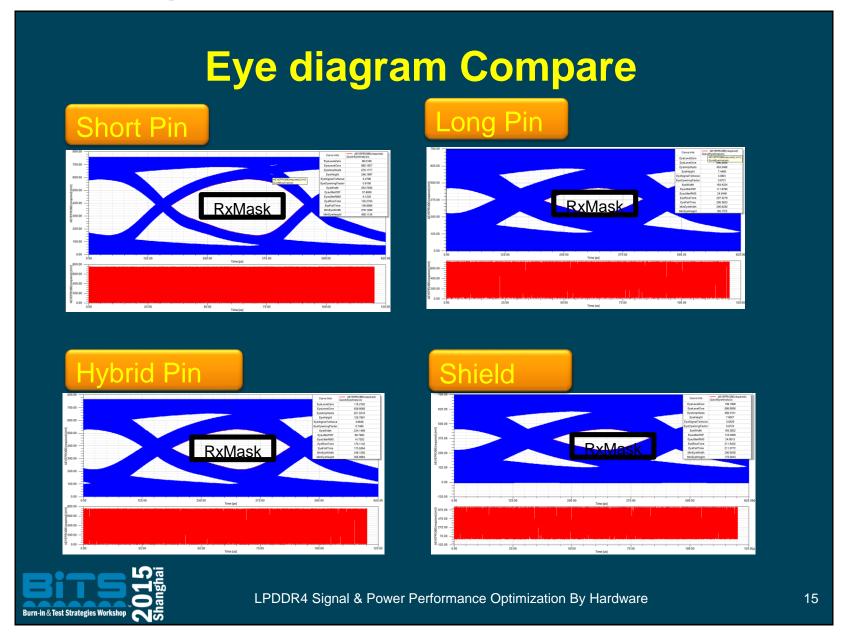

- Eyediagm analysis across different socket structure

# **Eye diagram Summary**

| <u>Structure</u> | <u>Jitter</u> | VdiVW mV |

|------------------|---------------|----------|

| Short Pin        | 0.038         | 247      |

| Long Pin         | 0.112         | 7.5      |

| Hybrid           | 0.069         | 129      |

| Coaxial          | 0.031         | 298      |

| Shielding        | 0.117         | 7.9      |

Jitter Spec: 0.04

TdivW: 79ps

VdiVW: 140mV

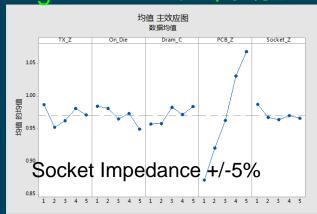

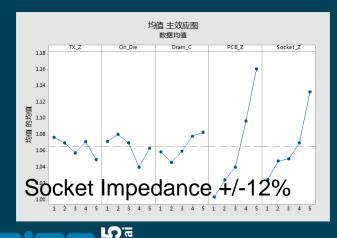

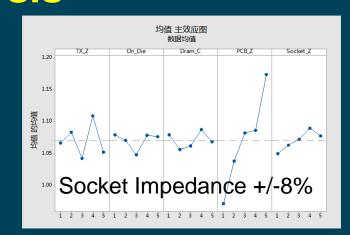

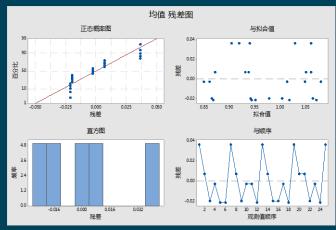

# High volume manufacturing sensitivity analysis

# **Channel Parameters**

Tx driver impedance (ohm)

On-die-termination (ohm)

DRAM Ci (pF)

PCB trace impedance (ohm)

Socket Impedance(ohm)

# **Variation**

34 +/- 10%

60 + / - 20%

2 + / - 10%

55 +/- 15%

50+/-5%

# High volume manufacturing sensitivity analysis

LPDDR4 Signal & Power Performance Optimization By Hardware

18

Burn-in & Test Strategies Workshop

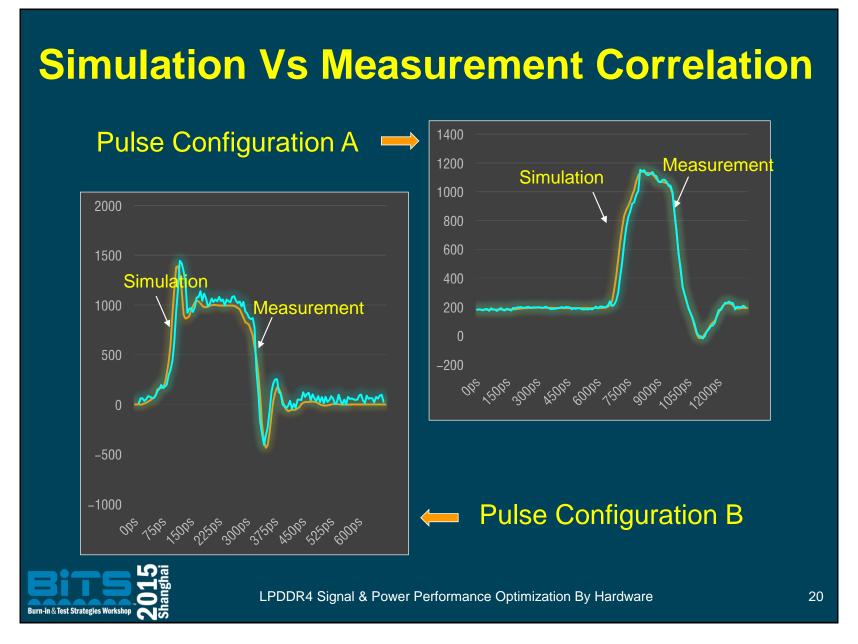

# **Simulation Vs Measurement Correlation** To Prober To Prober Socket Build Base on Pin Map LPDDR4 Signal & Power Performance Optimization By Hardware 19

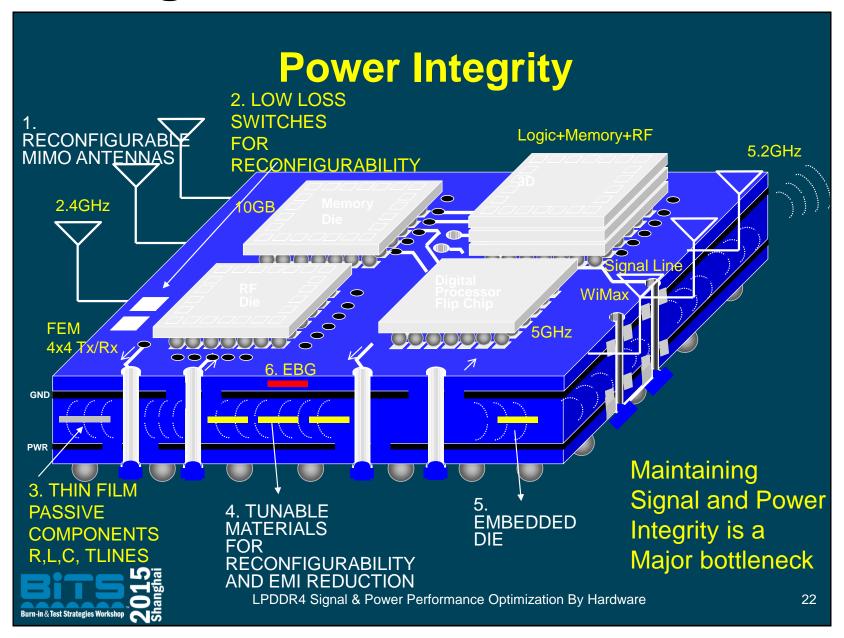

# **LPDDR4 PI Simulations**

- PI Basic

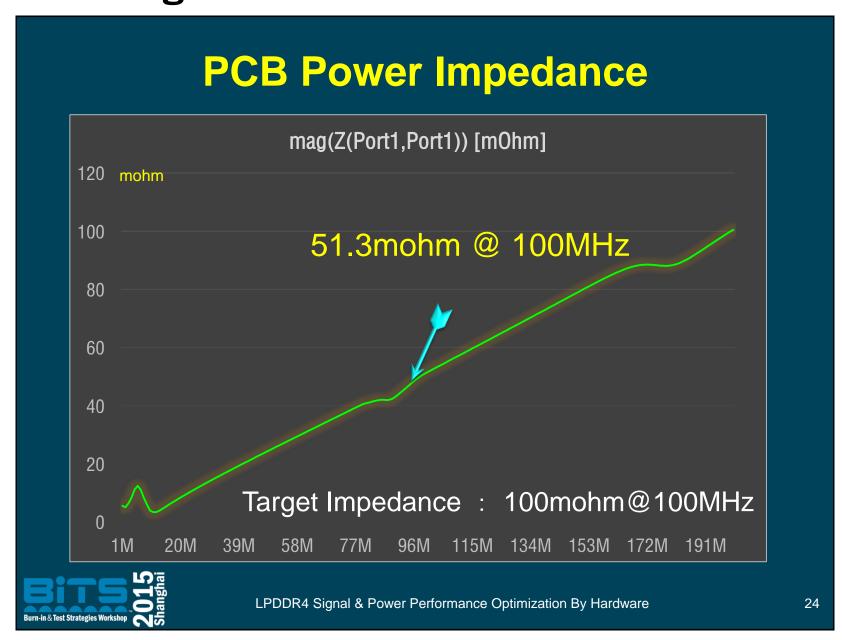

- PCB Impedance

- Socket Power Impedance Vs System Impedance

- Impedance Optimization

# Jitter caused by SSN for I/O

Vdd Varying Voltage Droop on Power Supply due to SSN

Output driver waveform

time

Uncertainty in Delay due to SSN causing Jitter

LPDDR4 Signal & Power Performance Optimization By Hardware

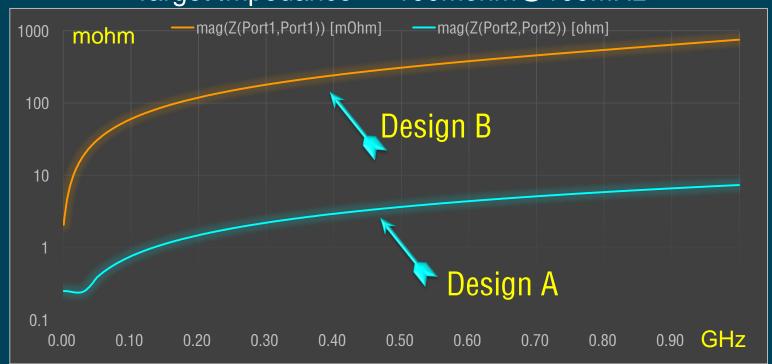

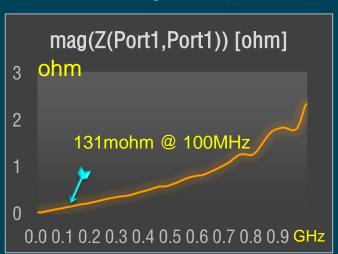

# **Socket Power Impedance**

Target Impedance: 100mohm@100MHz

Long pin and short pin has significant difference in terms of power impedance if only measure socket only.

LPDDR4 Signal & Power Performance Optimization By Hardware

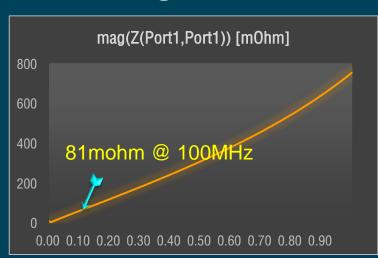

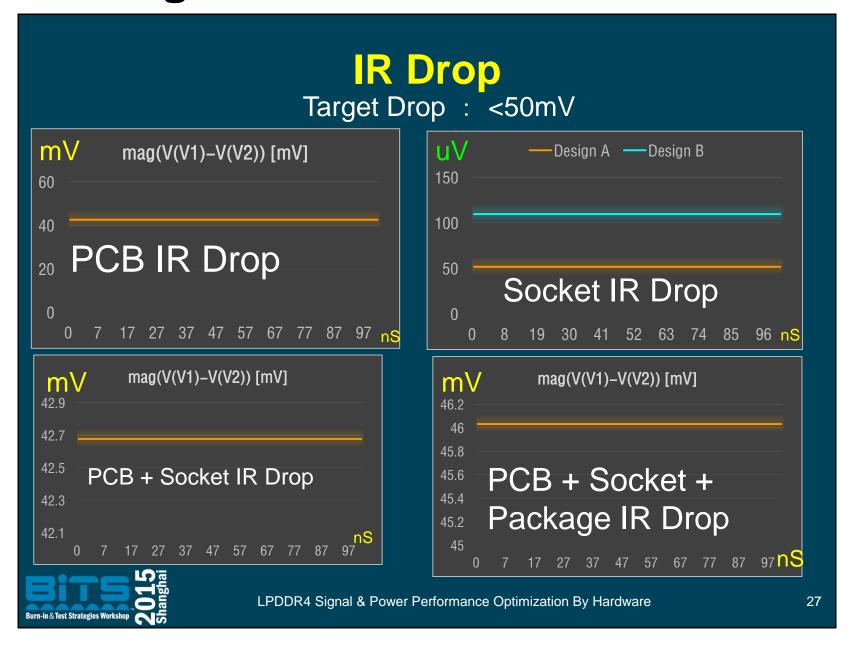

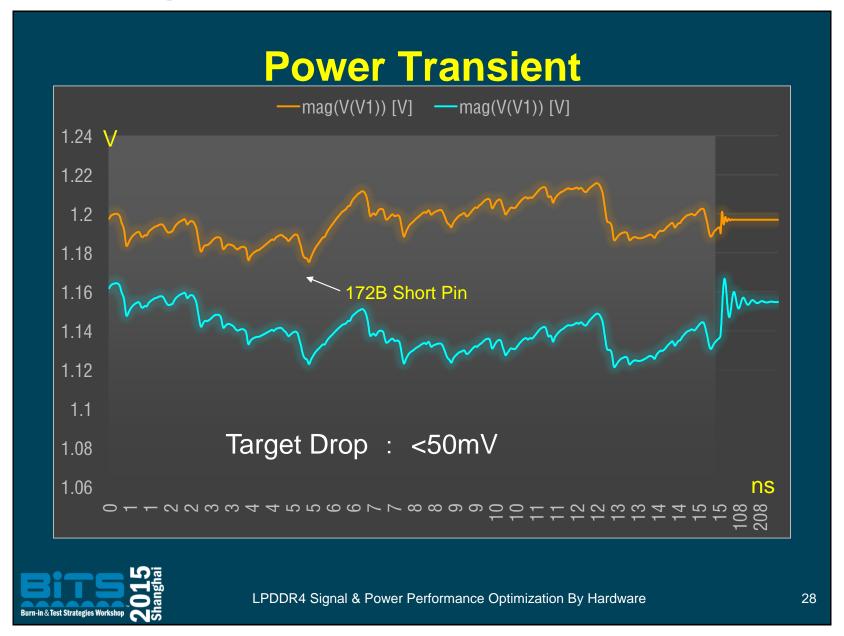

# PCB + Socket + Package Impedance Target Impedance : 100mohm@100MHz

#### **Before**

### After optimized

- Increase the power pane width, and short the distribution length.

- Optimize the pin length and diameter. 2.

- Although socket is not the main factor for the power impedance, however an optimized socket design and contactor selection also help the power impedance certain.

LPDDR4 Signal & Power Performance Optimization By Hardware

# **Summary**

- Discussion one method to study whether the hardware can meet the LPDDR4 specification.

- Discussion one method to identify the main factor for the whole SI chain.

- Optimize the socket and pin layout to meet the power impedance performance.

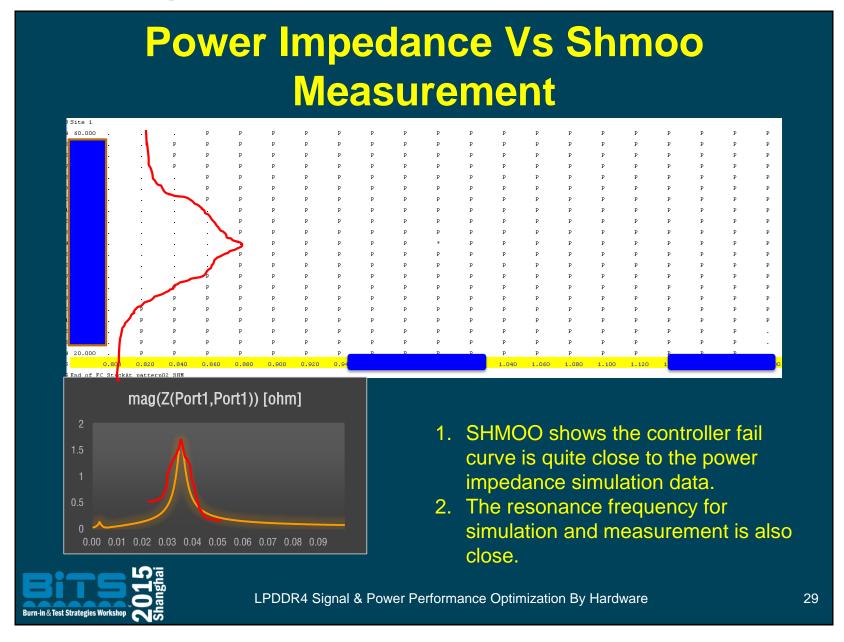

- Utilize Shmoo to correlate the power impedance data.