#### **Proceedings Archive**

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

March 6-9, 2016

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

2

## **Proceedings Archive**

**Burn-in & Test Strategies Workshop**

Burn-in & Test Strategies Wo

www.bitsworkshop.org

March 6-9, 2016

#### Stimulating Simulating - Simulation

#### **BiTS 2016**

# Characterize Only the High Speed Interconnect Performance

Carol McCuen R&D Altanova

2016 BiTS Workshop March 6 - 9, 2016

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

March 6-9, 2016

## Goal

- To provide Signal Integrity Engineering with an accurate model of their particular High Speed Interconnect in the form of an S-parameter data file.

- Where does the Interconnect begin and end?

- Do we include the traces, vias, ground plane, PCB substrate in the model?

- Can we use the measurement data to create Time Domain information, i.e. step impedance or eye diagrams?

- What Signaling (Single-ended or Differential) and Pin configurations are needed?

Characterize Only the High Speed Interconnect Performance

Stimulating Simulating - Simulation

### Plan of Attack to Reach Goal

- Make Laboratory Measurements on PNA

- What measurements do we want and how to set measurement parameters for success?

- Frequency vs. Time Domain

- Create an accurate 3D model, using the measured data, and then use to predict new variations of Interconnect patterns of Signal pins, Aggressor pins and Grounding pins.

Characterize Only the High Speed Interconnect Performance

Stimulating Simulating - Simulation

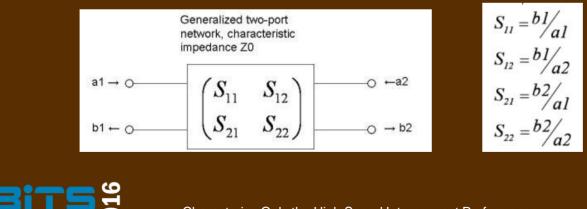

#### What are S-parameters? Network Analyzer measurements

- The Black Box --"Linear Networks can be completely characterized at the network terminals without regard to the contents of the networks..." Richard Anderson, author of the well know Agilent Application Note 95-1

- S-parameters are better than Z (impedance) or Y (admittance) parameters because of the problem of creating a good Open and Short at high frequencies.

- S-parameters are intrinsically a frequency domain measurement.

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

Stimulating Simulating - Simulation

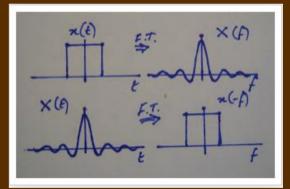

#### **Basic Time Domain Considerations**

- In the perfect world, we can use the Fourier Transform pair to convert from the frequency domain to the time domain, or visa versa.

- Our S-parameter are Band-Limited and only at Discrete Frequencies, use a DFT,

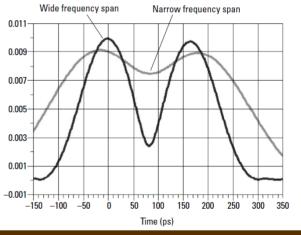

- ±∞ Frequency is impossible which creates ringing and spreading (sinx/x) in the time domain response. See the Inverse Fourier Transform (IFT) of the rectangular function.

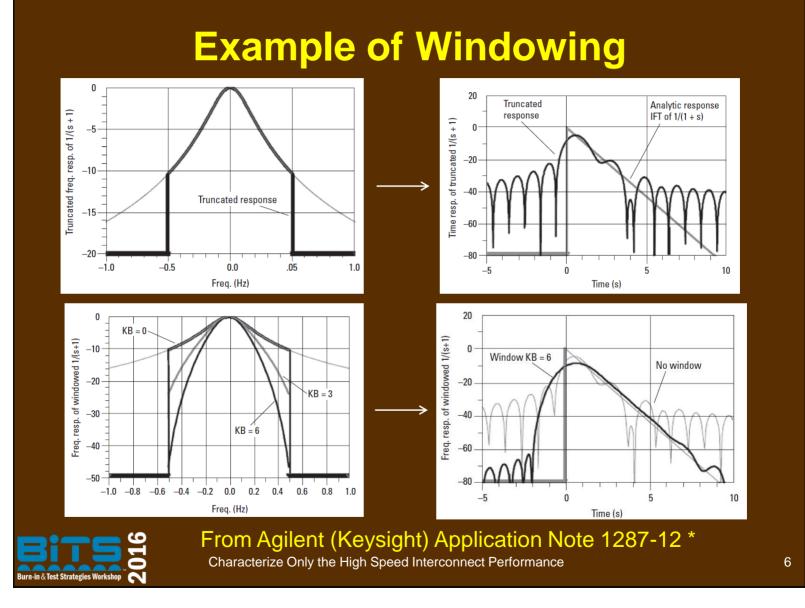

- A Windowing function can be used to control side-lobes in the IFT by gradually reducing frequency data at the band edge, instead of abrupt edge. There are usually 3 choices for windowing – Min., Normal, Max.

#### **Continuous Function**

$$X(\omega) = \int_{-\infty}^{\infty} e^{-j\omega t} x(t) dt$$

$$x(t) = \frac{1}{2\pi} \int_{-\infty}^{\infty} e^{j\omega t} X(\omega) d\omega$$

Birns 0100 Burn-in & Test Strategies Workshop

Characterize Only the High Speed Interconnect Performance

#### **BiTS 2016**

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

## **Time Domain Considerations (cont.)**

- Our S-parameters are Band-Limited and only at Discrete Frequencies

- Response Resolution is the measure of how close two responses can be to each other and still be distinguished.

- Response Resolution and Step Rise Time (RT) is also affected by Windowing. The more the control on the window roll-off the longer the RT and Response Resolution time.

Response Resolution

$$\frac{1}{2 \times F_{max}}$$

, where  $F_{max} = 50 \text{ GHz}$

$= 10 \text{ picoseconds}$

From Agilent (Keysight) Application Note 1287-12 \*

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

#### Stimulating Simulating - Simulation

#### **BiTS 2016**

## **Time Domain Considerations (cont.)**

- Our S-parameter are Band-Limited and only at Discrete Frequencies

- The sample frequencies must be equally spaced all the way down to DC, Zero Hertz + Frequency step.

- Because the S-parameters are discrete frequencies, time domain is a Repeated pulse train - response will repeat at the inverse of the Frequency step, 10 MHz Vary step size to assure length of time for signal to travel across DUT.

5000 Frequency samples 10MHz to 50 GHz

$$Period = \frac{1}{10 \ MHz} = 100 \ ns$$

$Total length of time IDTFT = 5000 \times 10ps = 50ns$

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

Stimulating Simulating - Simulation

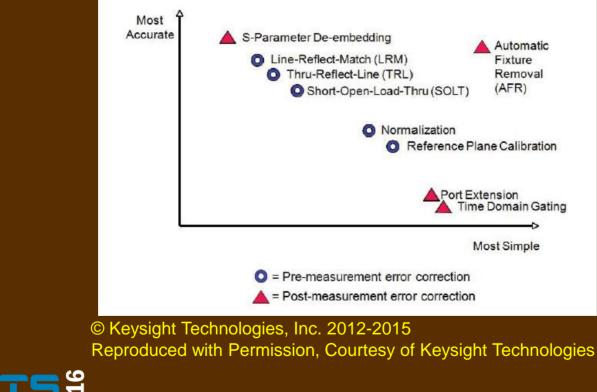

#### Various Error Correction Techniques

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

urn-in & Test Strategies Works

Stimulating Simulating - Simulation

#### Methods to remove the Effects of the Test Fixture

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

10

Stimulating Simulating - Simulation

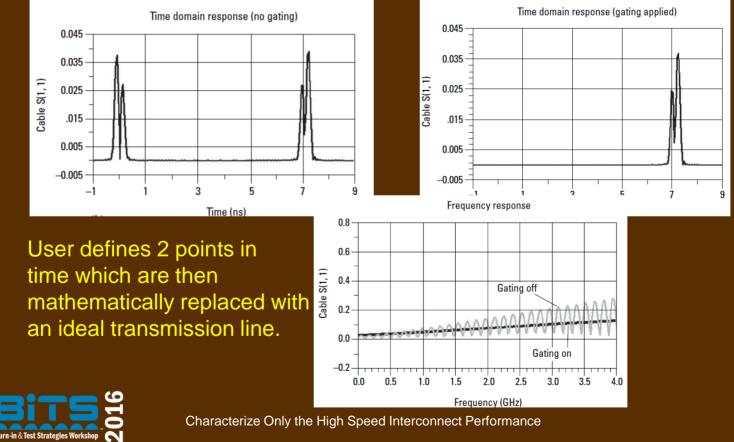

### **Port Extension or Phase Rotation**

- Performs removal of a length (Phase) of perfect ideal transmission line.

- Some VNA's will add an Insertion Loss compensation for flat attenuation across the band of measurement.

- This can lead to inaccurate results because the reflected wave due to the Real Fixture's mismatch combines with the incident waves and create peaks and nulls in the response.

- These disturbances to the response will not be removed when using a simple port extension.

Characterize Only the High Speed Interconnect Performance

#### **BiTS 2016**

Stimulating Simulating - Simulation

#### **Direct measurement vs. De-embedding**

• If we did a probe-tip calibration, a Direct measurement, De-embedding would be unnecessary.

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

### **Bits 2016**

Stimulating Simulating - Simulation

Smeasured

#### **Direct measurement vs. De-embedding**

• The probes alone will not be able to compress the contacts. Post-Measurement processing-De-embedding will be needed.

#### • De-embedding procedure

- 1. Get 2-port S-parameters of Test Fixture A (TFA) and Test Fixture B (TFB).

- 2. Measure DUT with TFA and TFB called  $S_{measured}$

- 3. Convert to T-parameters ->  $[T_{DUT}] = [T_A]^{-1} [T_{measure}] [T_B]^{-1}$

- 4. Convert  $T_{DUT}$  back to S-parameters,  $S_{DUT}$ .

- The difficult part is getting the 2-port S-parameters for the Test fixtures A and B.

- Choose-> Coaxial Cal & Use Keysight's PNA Physical Layer Test System (PLTS) 2015, Automatic Fixture Removal.

Characterize Only the High Speed Interconnect Performance

Stimulating Simulating - Simulation

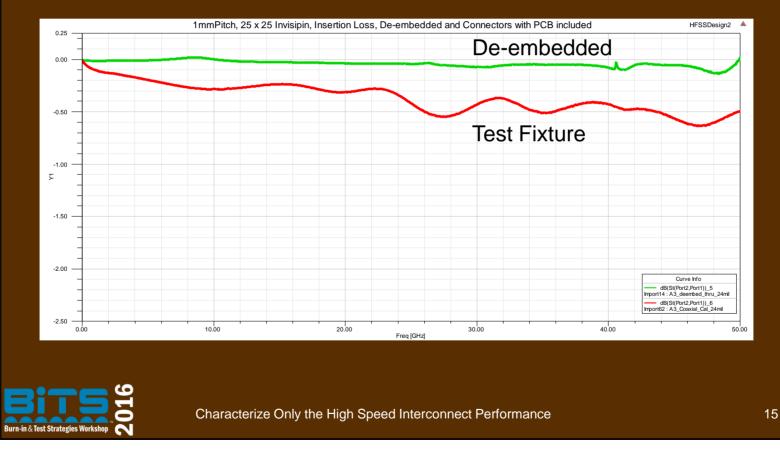

#### **Automatic Fixture Removal (AFR)**

- What is in the test Fixture that needs De-embedding?

- A very flat device with very small separate conductors to contact all the pins evenly. – a PCB will work well along with a stiffening fixture.

- Two 30 mil Taconics TLY-5 with 2 mil thick copper Top and Bottom layers

- Two Connectors 2.4 mm 50 Ohm Vertical PCB Compression Jack

- 1. Assemble the test Fixture without the Interconnect pins soldered. Make Thru measurement.

- 2. The AFR will determine the Test fixture A and B 2-port S-parameters.

- 3. The PNA will do the matrix math to De-embed TFA and TFB, resulting in the DUT S-parameters..

Characterize Only the High Speed Interconnect Performance

Stimulating Simulating - Simulation

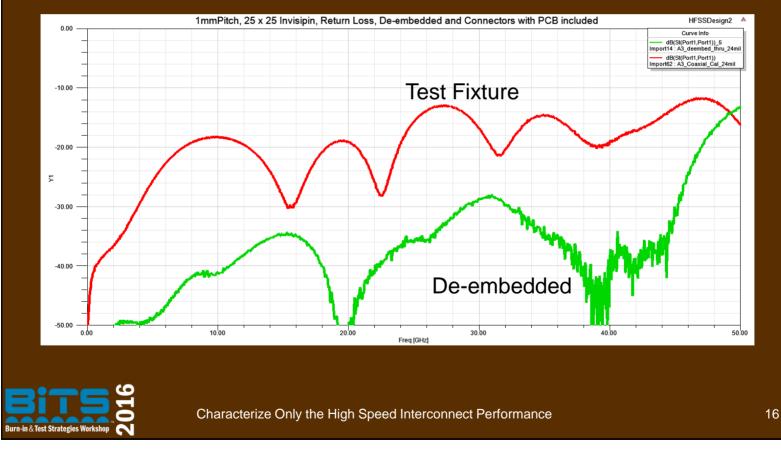

#### Results Insertion Loss: Test Fixture (Red) vs. De-embedded (Green) 1mm pitch, 25 x 25 pin, 24 mil hardstop thickness

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

#### Results Insertion Loss: Test Fixture (Red) vs. De-embedded (Green) 1mm pitch, 25 x 25 pin, 24 mil hardstop thickness

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

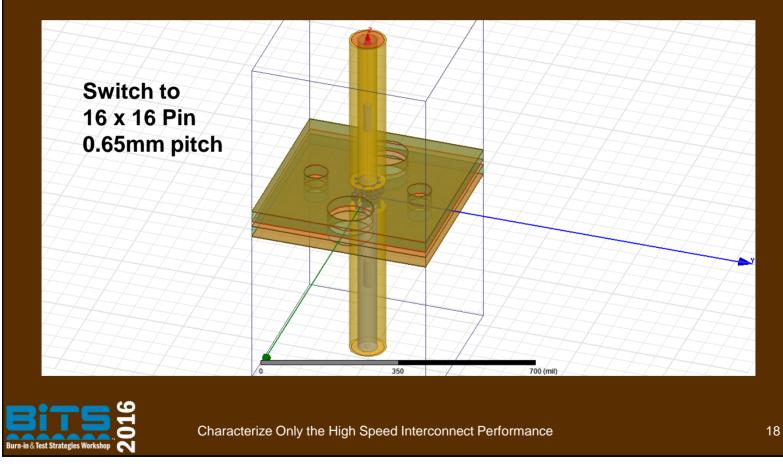

#### **Determine the 3D model**

- In order to have confidence in the High Speed Interconnect 3D model it is best to take more than one approach when comparing with measured data.

- Build 2 HFSS Models and compare with two different measurements:

- 1. Use measured data that contains the test fixture with the contacts that we want to model.

- 2. Use the VNA De-embedded measurement data (Contacts Only)

Characterize Only the High Speed Interconnect Performance

17

Stimulating Simulating - Simulation

#### Complete Measurement- Connectors, two PCB's with Invisipin soldered to one PCB with Hardstop between.

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

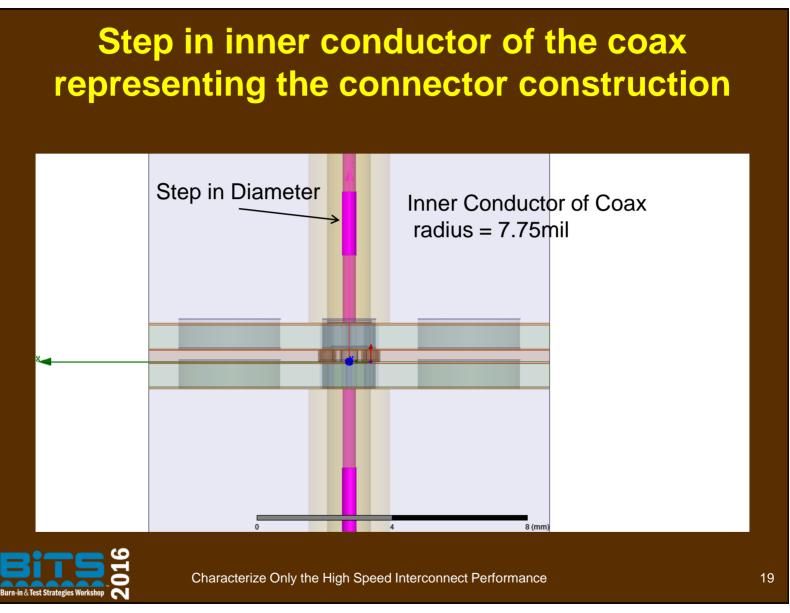

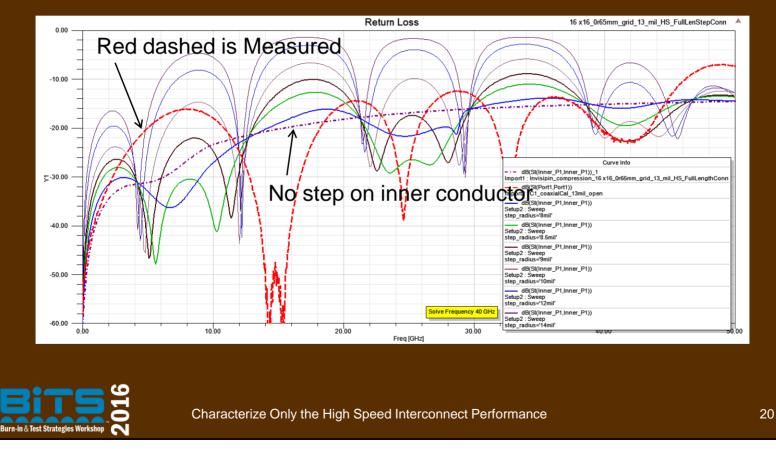

# **Return Loss -** Vary radius of the step on inner conductor, from 8mil to 14mil

#### Inner Conductor of Coax, radius = 7.75mil

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

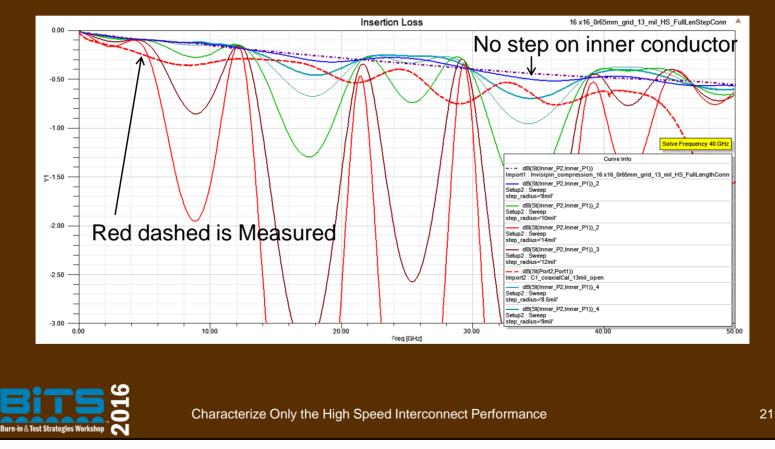

# Insertion Loss - Vary radius of the step on inner conductor, from 8mil to 14mil

#### Inner Conductor of Coax, radius = 7.75mil

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

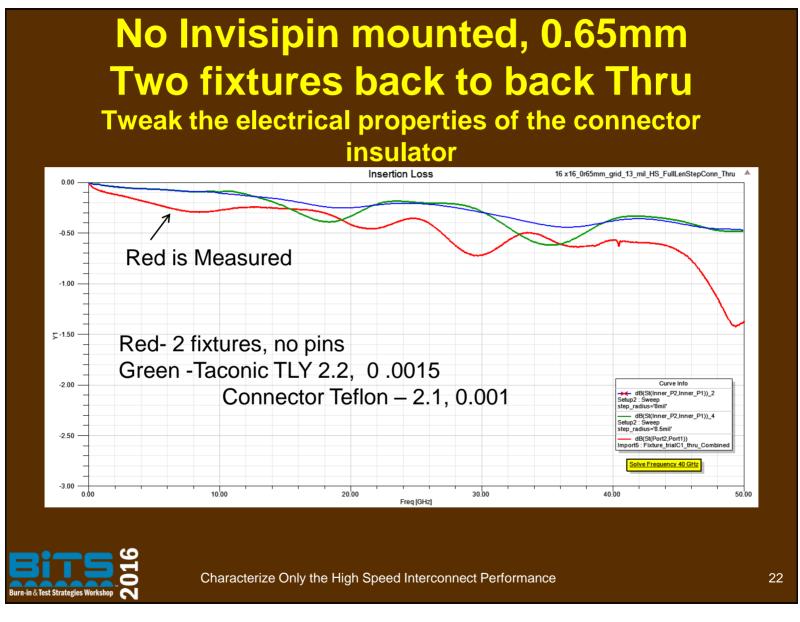

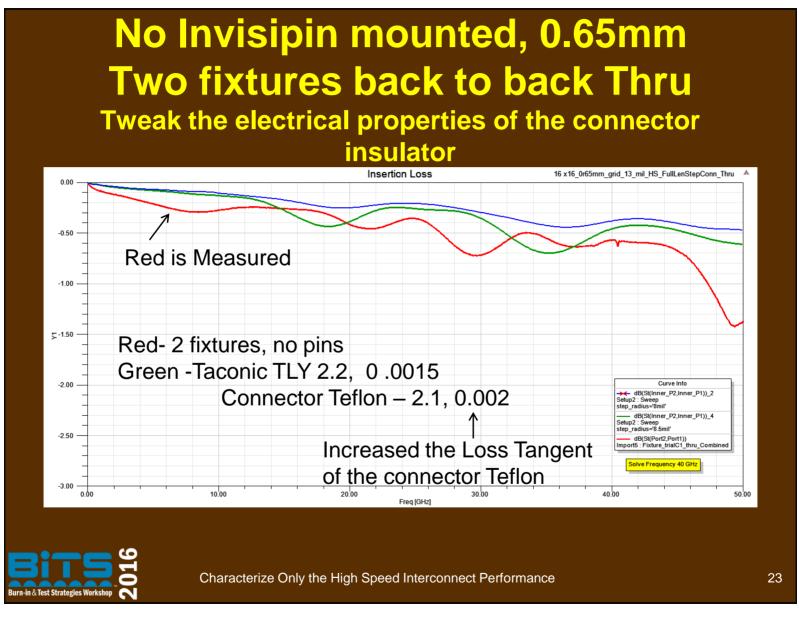

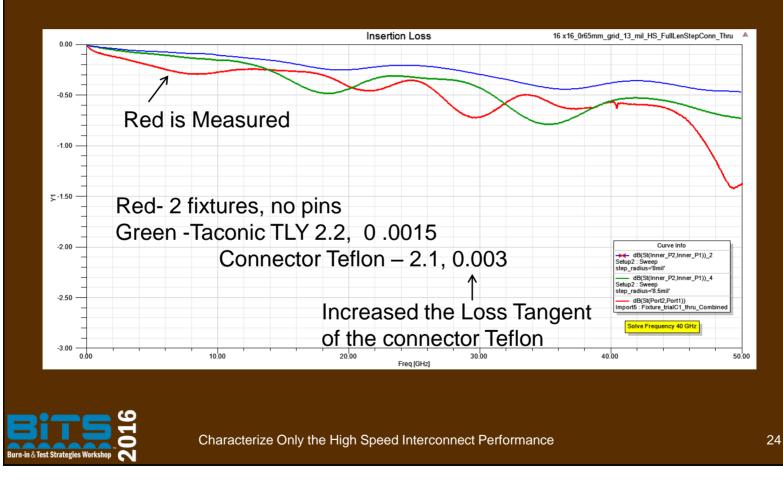

# Change Loss Tangent of the Teflon in Connector

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

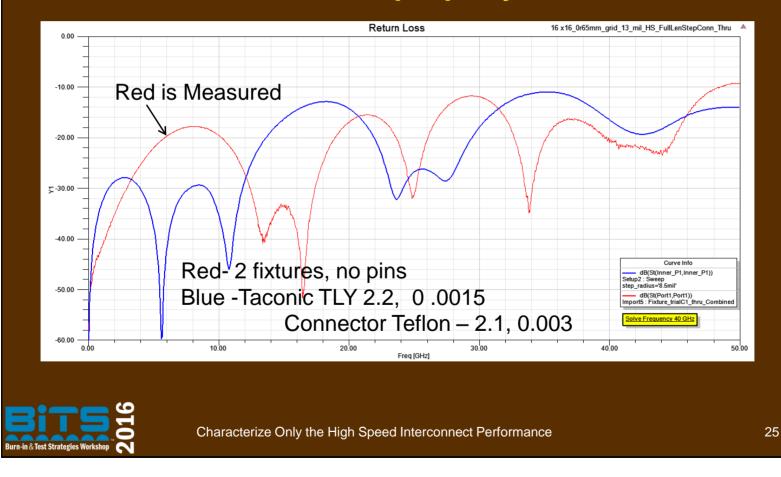

## No Invisipin mounted, 0.65mm Two fixtures back to back Thru Final electrical property values

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

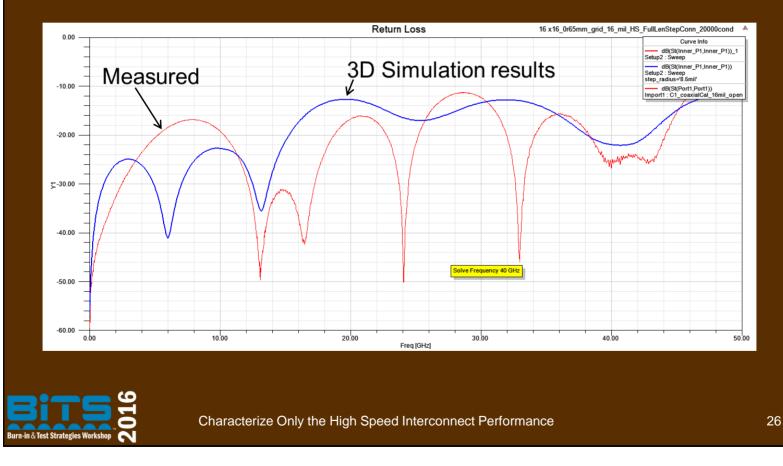

# Measured vs. Final 3D model of <u>Complete</u> Test Fixture with Pins

16 x 16, 0.65mm pitch - 16 mil Hardstop height

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

# Measured vs. Final 3D model of <u>Complete</u> Test Fixture with Pins

16 x 16, 0.65mm pitch - 16 mil Hardstop height

**Burn-in & Test Strategies Workshop**

#### Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

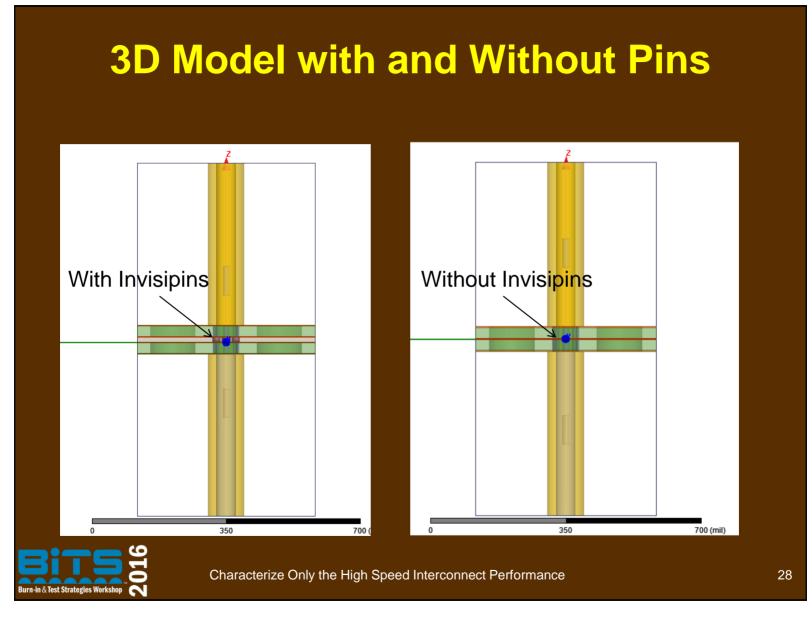

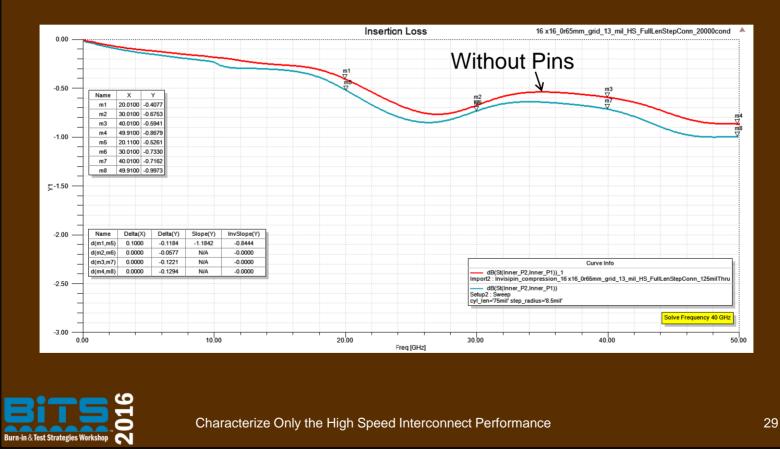

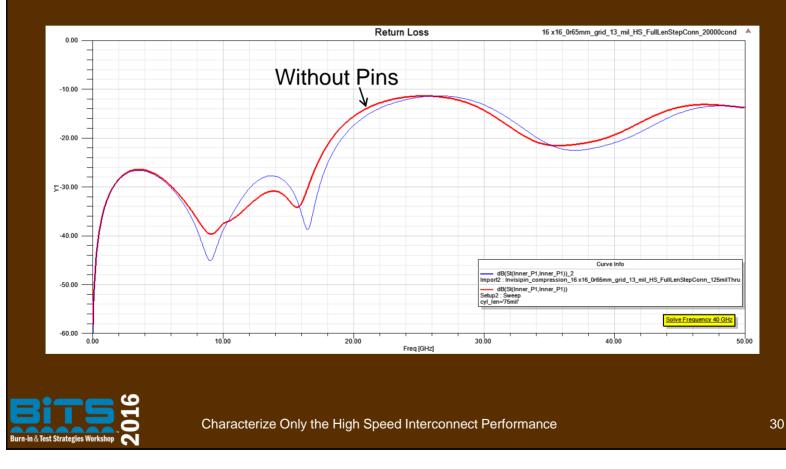

## Comparing the two 3D Modelswith the Pins / without the Pins

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

## Comparing the two 3D Modelswith the Pins / without the Pins

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

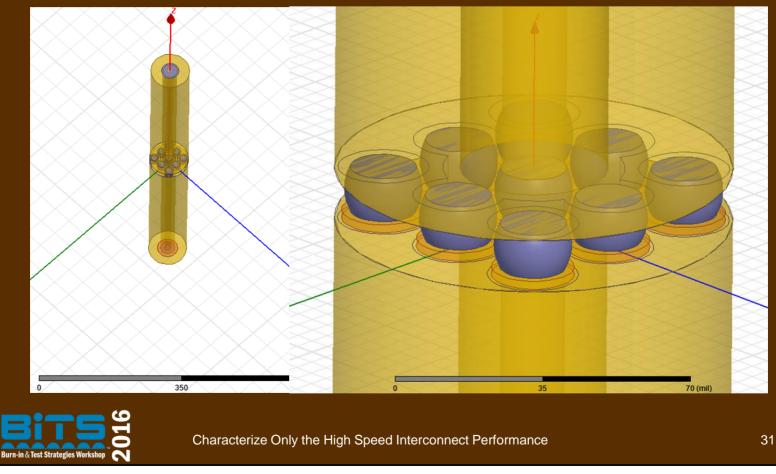

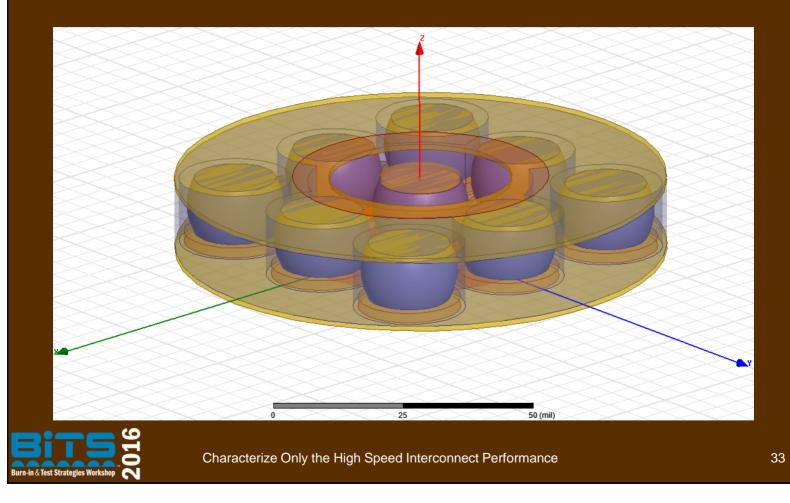

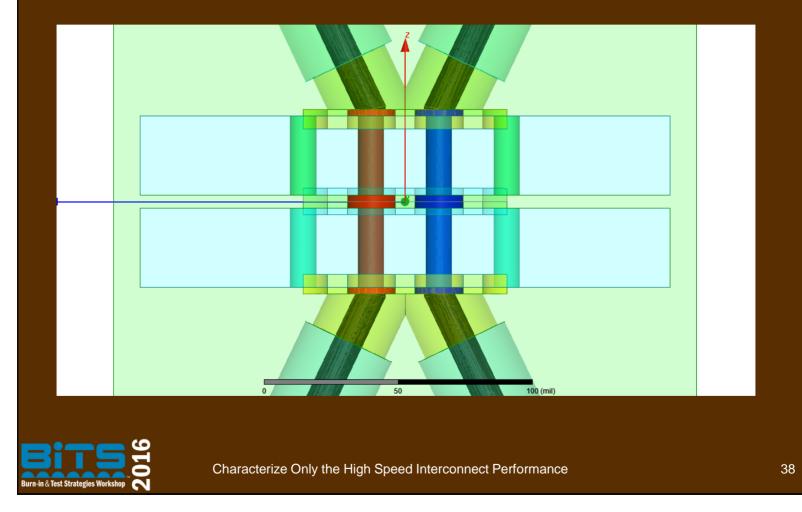

#### 3D Model of Just the Pins, same Electrical properties- with Waveport coaxial launch

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

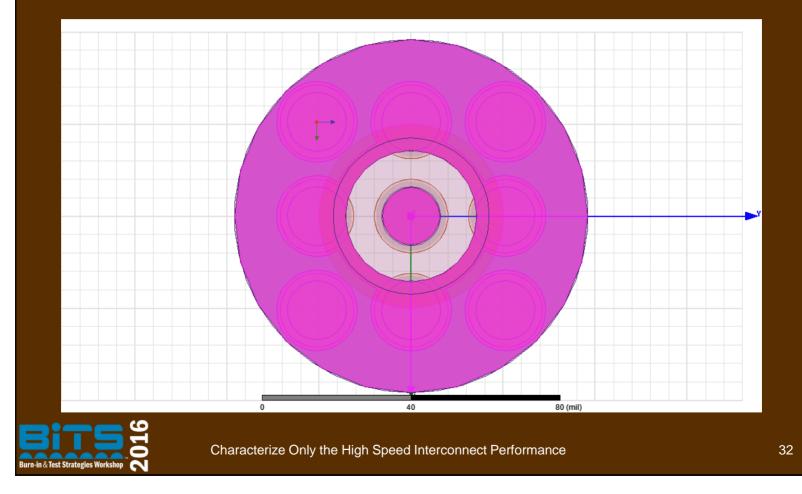

#### Outer and Inner Conductor of Air Core coax

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

## Same diameters on 1 mil thick PEC for the Coaxial Lumped Port

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

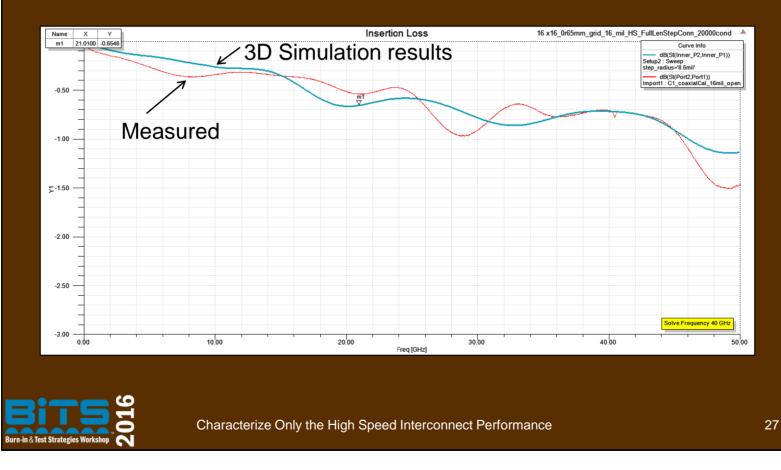

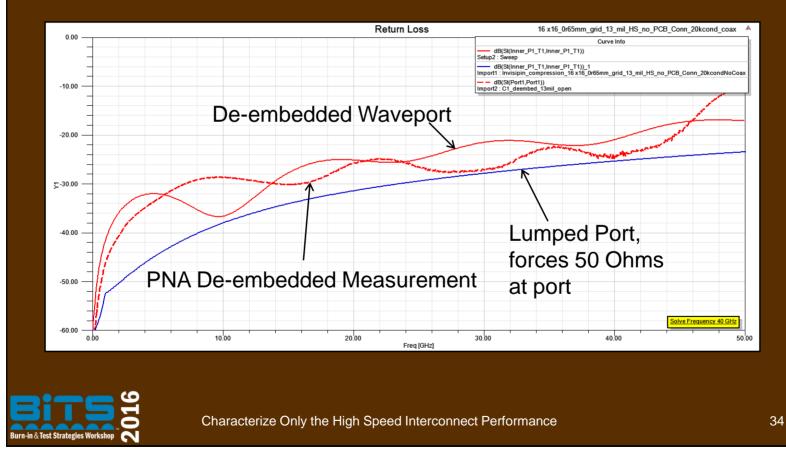

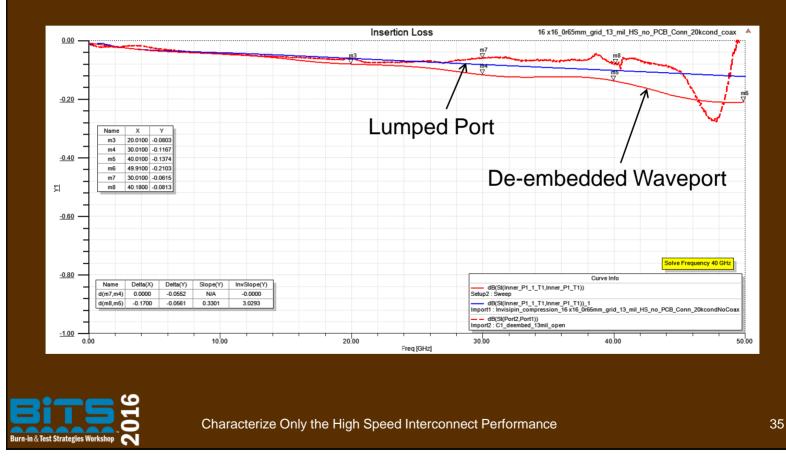

#### Just the Invisipins HFSS models vs. PNA De-embedded

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

#### Just the Invisipins HFSS models vs. PNA De-embedded

**Burn-in & Test Strategies Workshop**

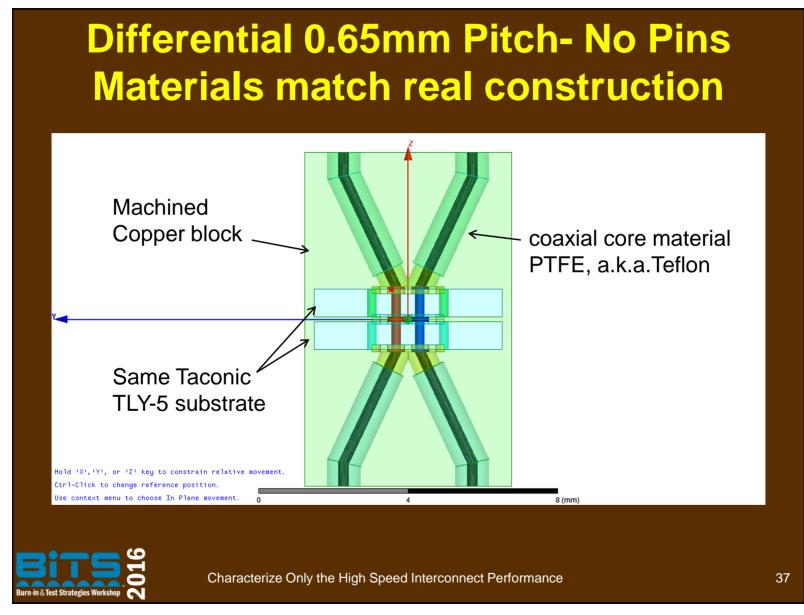

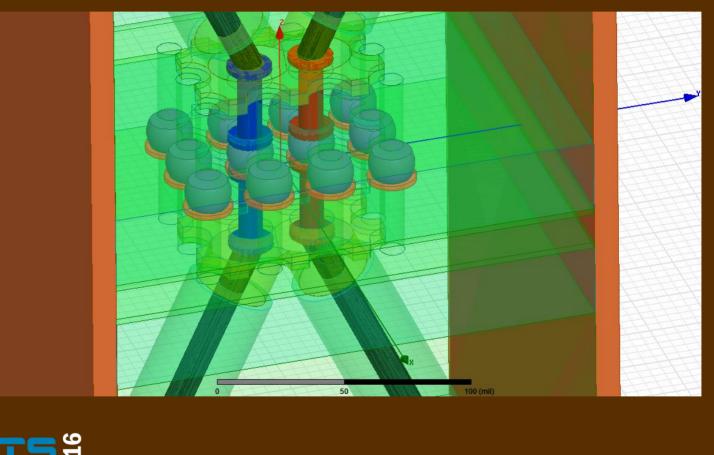

#### Determine the 3D model for a Differential Interconnect

- Why is Differential Signaling beneficial?

- Lower voltage swings

- Immunity from power supply noise

- Reduce dependency on difficult high frequency RF grounding

- Improved EMI performance

- Model will vary depending on the exact differential signal pin/Ground pin pattern being used for your application.

Characterize Only the High Speed Interconnect Performance

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

# Differential 0.65mm Pitch- No Pins Materials match real construction

Burn-in & Test Strategies Workshop

#### **BiTS 2016**

Stimulating Simulating - Simulation

**Burn-in & Test Strategies Workshop**

#### **BiTS 2016**

Stimulating Simulating - Simulation

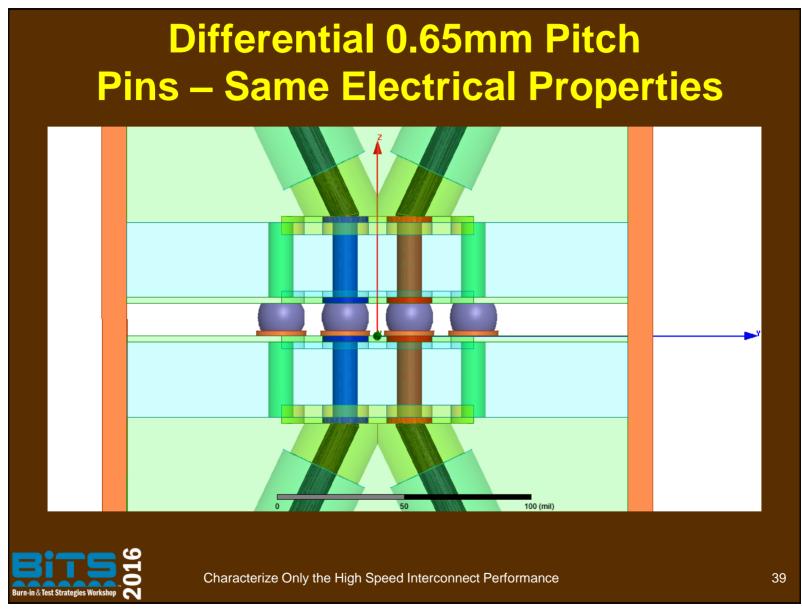

## **Differential 0.65mm Pitch- Pins Ground Pins Surrounding Signal pair**

Characterize Only the High Speed Interconnect Performance

Burn-in & Test Strategies Workshop

rn-in & Test Strategies Wo

Stimulating Simulating - Simulation

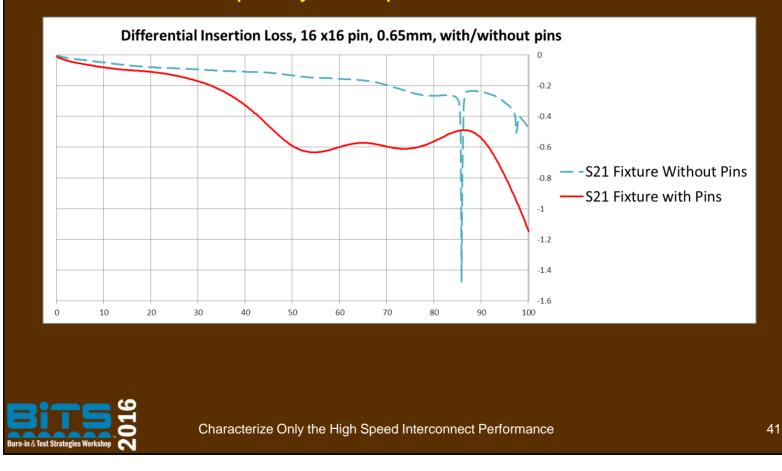

# Differential Insertion Loss 0.65mm Pitch- with/without Pins

Notice the Frequency Sweep has Doubled

Burn-in & Test Strategies Workshop

Stimulating Simulating - Simulation

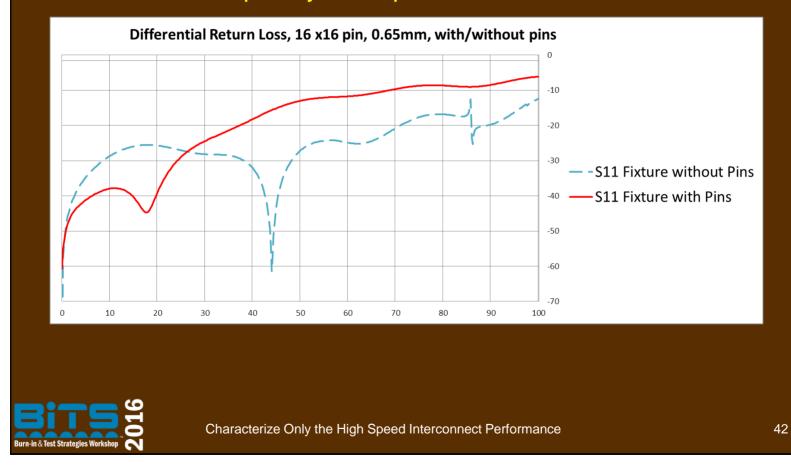

# Differential Return Loss 0.65mm Pitch- with/without Pins

Notice the Frequency Sweep has Doubled

**Burn-in & Test Strategies Workshop**

Stimulating Simulating - Simulation

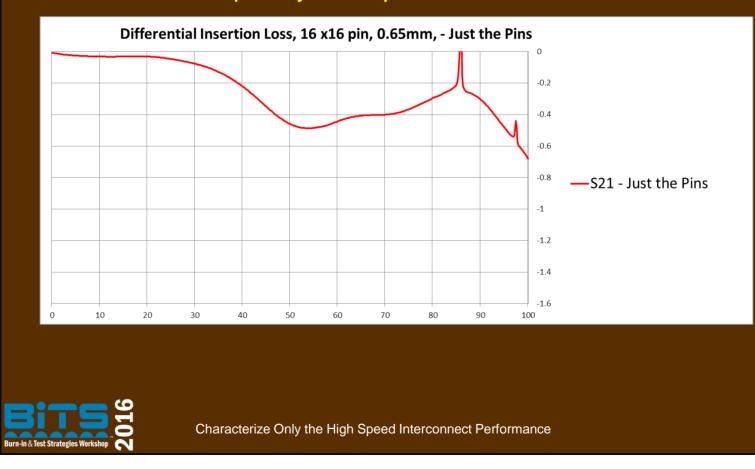

# Differential Insertion Loss 0.65mm Pitch- Just the Pins

Notice the Frequency Sweep has Doubled

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

43

Stimulating Simulating - Simulation

## Acknowledgements

- Diagram of S-parameter block, slide 4, <u>http://practicalfmri.blogspot.com/2011/06/physics-for-understanding-fmri\_23.html</u>

- S-parameters Without Tears- Understand this critical frequency-domain measurement and its interpretations, By Colin Warwick and Fangyi Rao, Agilent Technologies

- Agilent Time Domain Analysis, Using a Network Analyzer, Application Note 1287-12, Document 5989-5723EN

\* Images on slides 6 & 7 are © Keysight Technologies, Inc. 2012-2015

Reproduced with Permission, Courtesy of Keysight Technologies

- Keysight Technologies, Physical Layer Test System (PLTS) 2015, Document 5989-6841EN

- Thomas P. Warwick, HFSS 3D model of Differential Test Fixture

Characterize Only the High Speed Interconnect Performance