### **Proceedings Archive**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

### **Proceedings Archive**

Session 2

Ashok Kabadi Session Chair **BiTS Workshop 2016 Schedule**

### Frontiers Day

Monday March 7 - 1:30 pm

### **Material Matters**

#### "Long Life Probe Pin by Electroforming Process"

Makota Kondo & Hirotada Teranishi - Omron Corporation Takahiro Sakai & Naoyuki Kimura - Omron Corporation

# "Carbon Nanotube Polymer Composites as High Performance Thermal Interface Materials for Burn in and Test Applications"

Leonardo Prinzi - Georgia Institute of Technology

Craig Green & Baratunde Cola - Carbice Nanotechnologies, Inc.

#### "Requirements and Solutions for Test PCBs"

Markku Jamsa - Aspocomp Group Oyj

#### "PCB Test Fixture and Socket Challenges for mmWave Applications"

Don Thompson Jose - R&D Altanova Jose Moreira - Advantest Europe GmbH Giovanni Bianchi - Advantest

# Requirements and Solutions for Test PCBs

Markku Jämsä Aspocomp Group plc

2016 BiTS Workshop March 6 - 9, 2016

## **Test PCBs in the Test Systems**

- PCB is a key component for several IC testing applications including:

- IC ATE testing in component manufacturing

- Reliability testing during component qualification

PCB manufacturing lead times can be bottleneck regarding the project schedules

# IC ATE PCBs, Typical Technical Requirements

- High packaging density combined to large PCB

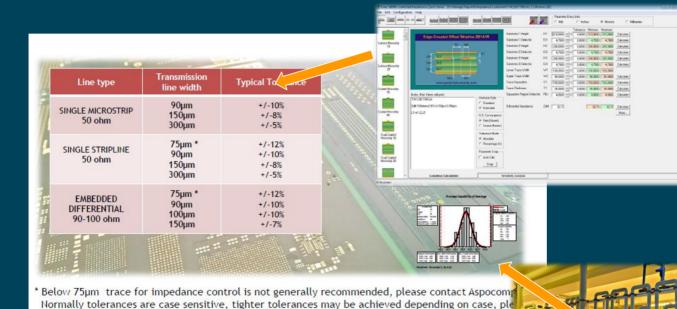

- Impedance match, insertion loss minimize

- Other signal integrity items

- Flatness

- PCB assisted cooling

- And a few more

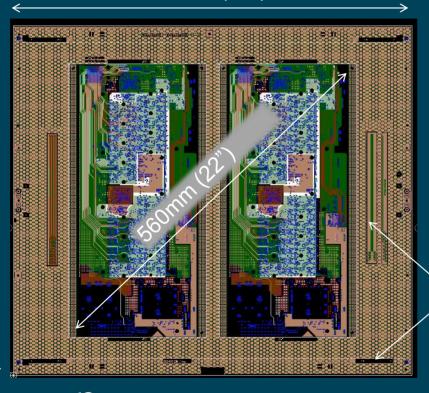

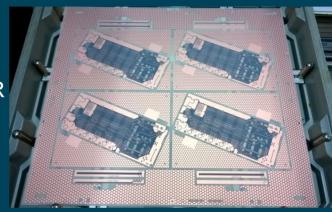

## IC Test Board Example

- PCB size 250 x 450mm (9"x18")

- 3,7mm (0,15 inch); 24 Layers, no HDI

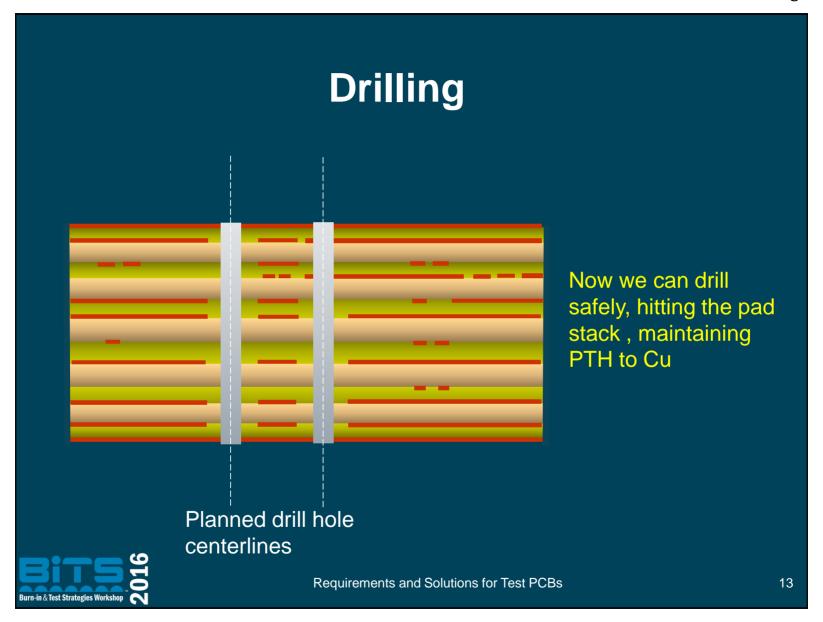

- Epoxy filled / over plated vias, back-drill in 6 levels

- Via size 0,25mm (10mils), Aspect ratio 15

- PTH to Cu Clearance 180u /7 mils

- Low loss material EM828

- 12 impedance control configurations

- Dielectric thickness 75-150u (3-6 mils)

- Line width 75/90u (3/3,5mils)

# Test Board in Quick Turn Around (QTA) Manufacturing

5 day manufacturing requires at least following:

- All laminate raw materials must be in hand

- All technology features tested and agreed in advance

- Dimensional parameters are known in advance

- Impedance and other signal integrity matters pre-set

Target is to make the example PCB in 5 working days, how to make it happen?

# **Key Issues to Prepare for This QTA Batch**

- Dimensional (shrinkage) control of the new stack-up

- Impedance details and tolerances

- Insertion loss and material choices

- Cooling details and design guidelines for it

- Prepare with the laminates if any missing

- Agree in advance as much commercial matter as possible

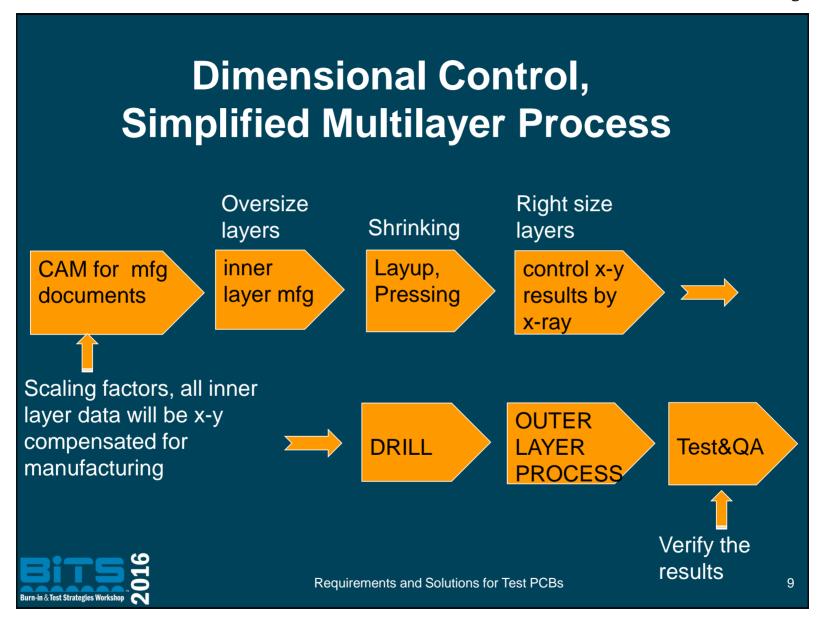

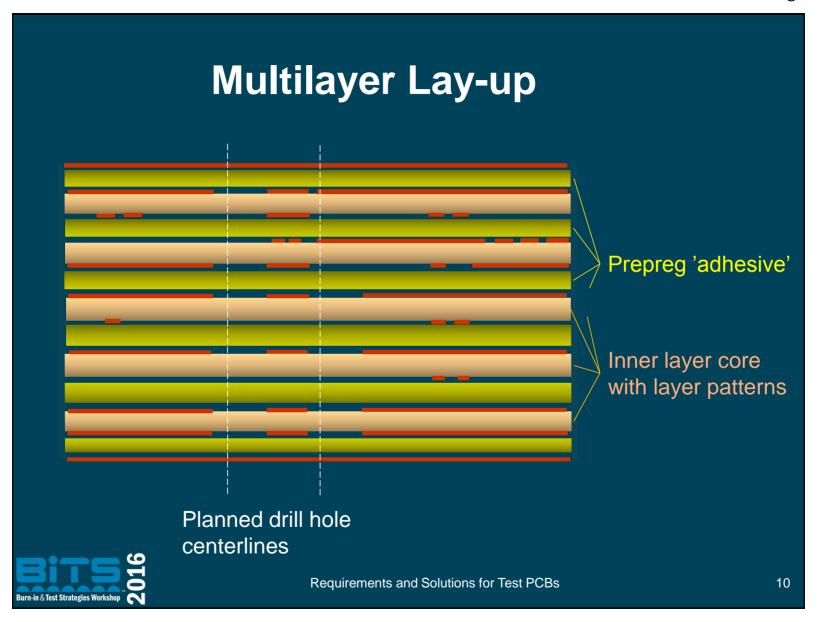

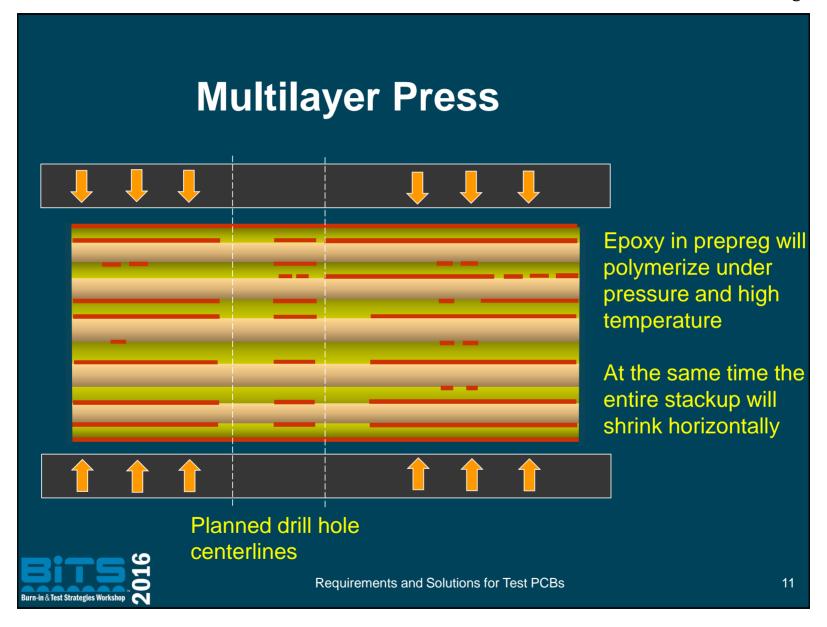

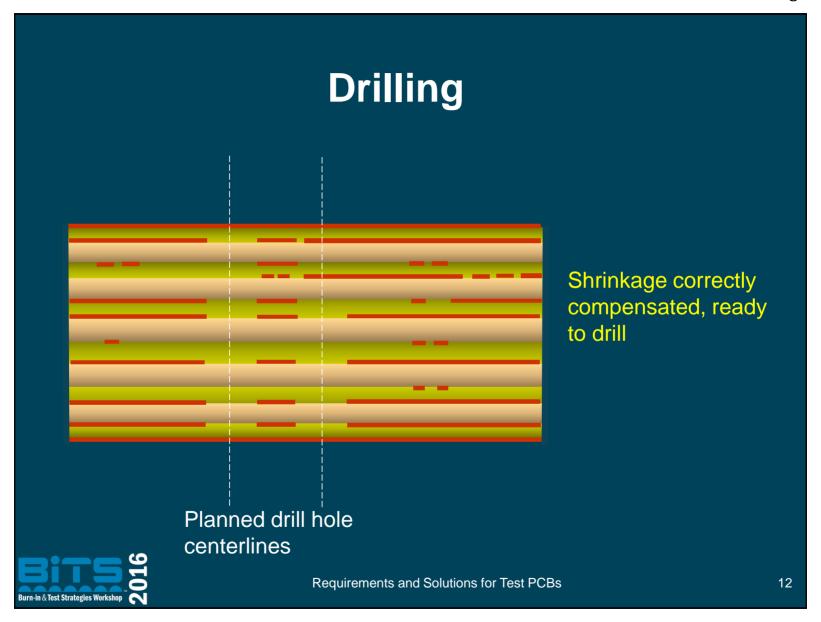

### **Dimensional Control Challenge**

PCB is based on organic substrate, x-y dimensions change (shrink) during the manufacturing

Each inner layer in this PCB will shrink in magnitude of 8-12 mils, each layer in individual manner\*

Shrinkage is stack-up sensitive, but repeat-able

<sup>\*</sup> Depending on the materials and number of sequential laminations, the values can be much higher in some cases

### **Inner Layer Production Panel**

619mm (24")

Dimensional control is a key regarding functionality, PCB yield and cost

Impedance coupons

Layer x-y position targets

533mm (21")

Requirements and Solutions for Test PCBs

#### **BiTS 2016**

# **PCB** Ready PCB can be finalized **Epoxy fill** Backdrilled overplate via via Requirements and Solutions for Test PCBs 14

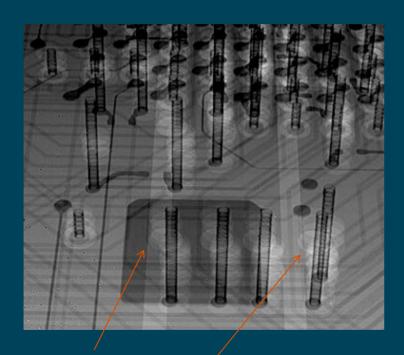

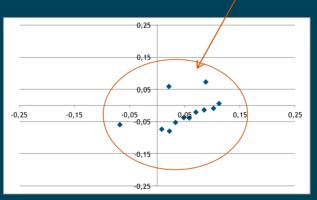

## **View Before Optimizing**

True layer average positions within +/- 120u (5mils)

Short circuit risk due to layer misalignment

Batch will fail without optimizing

Requirements and Solutions for Test PCBs

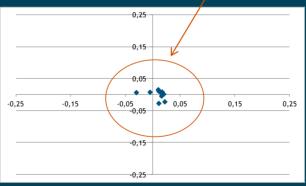

### **View After Optimizing**

All true layer average positions within +/-40u (1,5mils)

Batch will be ok

Requirements and Solutions for Test PCBs

Designer takes care of robust dimensions and PCB company takes care of the best possible

contact Aspocomp

Requirements and Solutions for Test PCBs

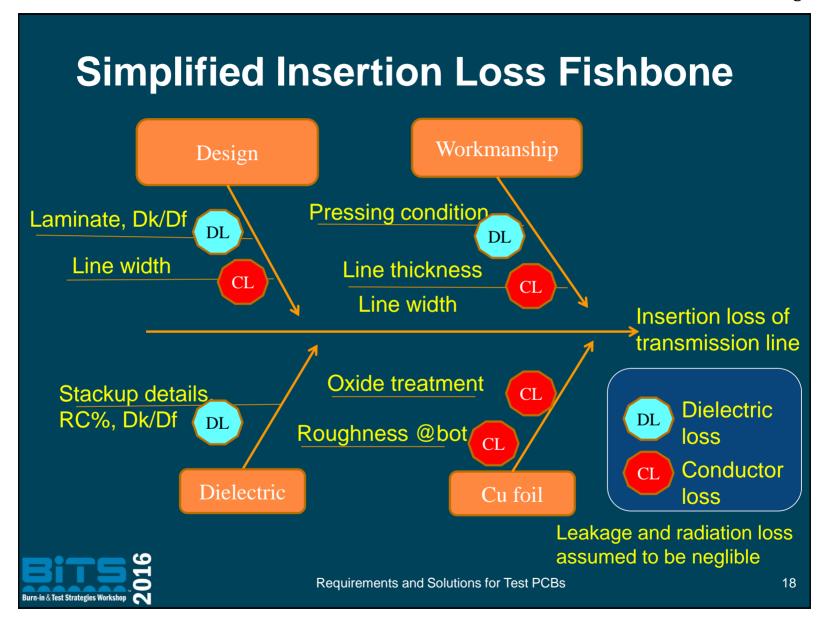

### Insertion Loss Consideration

- Designer's task

- Laminate material choice

- Applicable track width

- Copper foil type selection together with PCB supplier

- Insertion loss simulation

- PCB manufacturer's task

- Support the material choice and copper foil selection

- Detailed stack-up support, impedance/trace dimensions

- Possibly insertion loss simulation

- Good workmanship

- Project management need to connect designer and the PCB shop

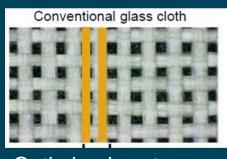

### **Additional Signal Integrity Matters**

- Stub elimination → Back-drill

- Glass weave effect elimination

- Tilted PCB in panel, can be bad MUR

- Flat Glass

Optimized cost

No quality impacts

Higher cost

Improved RF performance

Requirements and Solutions for Test PCBs

Spreaded glass cloth

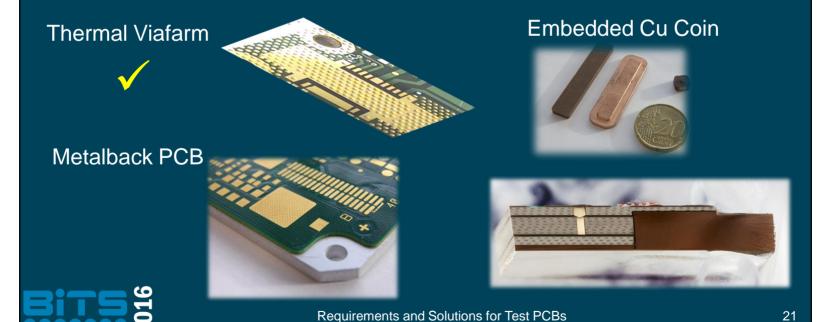

### **PCB Level Cooling**

- Heat management is important when designing IC test equipment electronics

- Higher operating temperature may influence the electrical properties of the PCB

- Possibilities for PCB cooling:

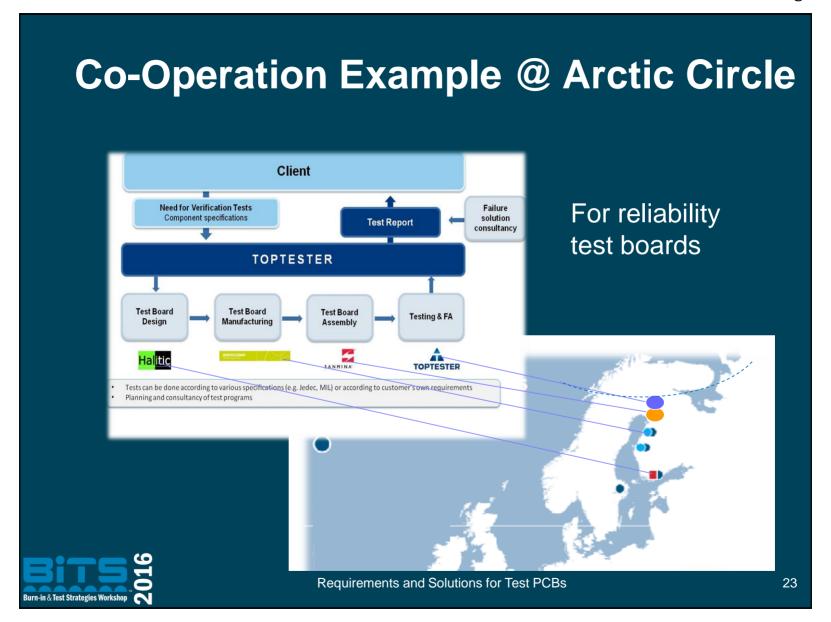

### Reliability Test PCBs of JEDEC Style

- Examples of the key requirements for these PCBs:

- High reliability, the purpose is to test components, not the PCB

- Mechanical robustness

- Connectivity → High local packaging density

With courtesy of

Requirements and Solutions for Test PCBs

10 000 g drop

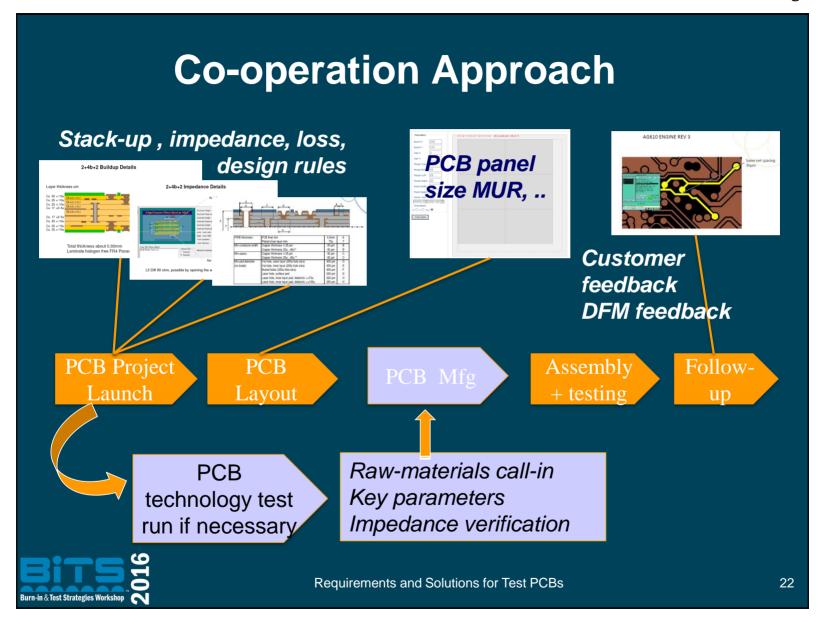

### Conclusion

- Co-operate with your PCB partner in early stage

- Agree about commercial issues in advance

- Take care of the PCB details

- Follow-up with your PCB supplier

Requirements and Solutions for Test PCBs