## **Proceedings Archive**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the 2016 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the 2016 BiTS Workshop. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop.

2

## **Proceedings Archive**

Poster Session

**BiTS Workshop 2016 Schedule**

## Frontiers Day

Monday March 7 - 3:30 pm

## **Poster Session**

"WiGig Test"

Bert Brost - Xcerra

"Re-balling BGA with Gold Plated Copper Spheres, the Need and the SMT Challenges"

Emad Al-Momani, Srikanth Mothukuri, Jack Mumbo - Intel Corporation

"Thermal Test Methodology for Validating Automotive Semiconductor Packages"

Ying Feng Pang, Amy Xia – Intel Corporation

"Insitu 256 Node Resistive Leakage Tester"

Gordon Cowan, Rich Zavala - HighRel, Inc.

## **Poster Session**

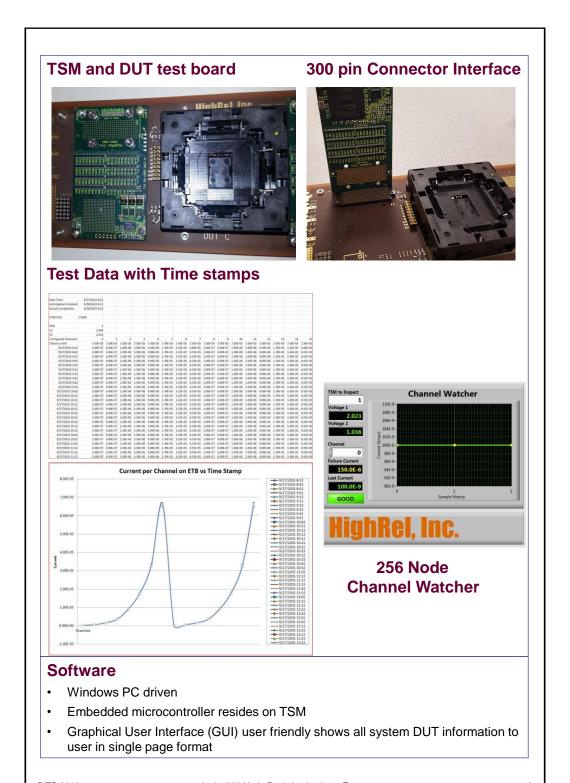

### In-situ 256 Node Resistive Leakage Tester

Mr. Gordon Cowan, President and CEO Mr. Rich Zavala, Vice-President of Engineering

#### **Challenges**

- Data from previous testing was more generic in terms of location of failures within the DUT. Test structures are tested in groupings of pins

- DUT coverage of the testing was not complete using DUT card type of testing per old test interface equipment. Only 30 channels of testing available on current systems test

- HAST test durations are typically 200 Hour tests at 25 hr-25 hr-50 hr-100 hr test intervals with removal of the DUTs from system to gather test data for failures

#### **System Overview / Solutions**

- Leakage Current Measurement in the range of 1-100 μA [+/- 1μA]. Range is set by user, per channel. Once the threshold current is met, voltage is removed from test structure during the stress test. Structure is identified and shut down. More precise data is gathered and recorded

- In-System Monitor and Report up to 256 DUT test nodes.

- Eliminates the need for removal of the DUT from environmental test to perform additional DUT testing causing decreased cycle time in product and process validation to production

#### **Hardware**

- Test system module (TSM) is 2.5" x 3.0" in size.

- Powered by a single 5Vdc supply and up to two external 1-5Vdc power supplies provide power to DUT

- 16 banks of 16 channels hosting 10K measurement resistor to GND

- 300-pin SMT compression connector used to interface to DUT

- Data management handled by local TSM microprocessor

- High precision ADC used to measure and capture data logged

- Entire TSM measurement set of 256 channels completed < 1 min</li>

- Conformal coated to achieve long life within hostile environments

BiTS 2016

Insitu 256 Node Resistive Leakage Tester

## **BiTS 2016**

## **Poster Session**

BiTS 2016

Insitu 256 Node Resistive Leakage Tester

2

## **Poster Session**

#### Software (cont.)

- Win PC logs TSM measurement data on regular basis, show pass/fail condition of each of the 256 channels

- Application layer connects with embedded processor via single USB port and standard 1-wire communication reducing I/O pins

- Multiple TSMs available to PC for test / data management via embedded processor communication board

- Data management through simple \*.csv formatted files

- Recipe files stored with test condition data, min/max fail parameters and frequency of data collection

- Test results are collected with time-stamp for each cycle measurement

#### **Conclusion / Solutions**

- Can be used in any series mode, low side sense current measurements

- Voltage is removed from DUT to preserve fail points at set threshold levels as the DUT degradation occurs

- Precise data is gathered for the location of the failed DUT structures

- 8.5 X more coverage of the DUT captured data

e Count 2 TSM Count 3 Channel Count 243 Test Length (Hrs) 1 Test Freq (min) 5

- TSM basically viewed as 256 low current measurement meters and the data stored in disk file information files

- Developed for HAST systems, but can be adapted to any environmental system test

- 10K resistor may be changed to rescale to other leakage range requirement

- Operator handling of DUT is kept to a minimum

HighRel, Inc.

BiTS 2016

Insitu 256 Node Resistive Leakage Tester