Burn-in & Test Strategies Workshop

www.bitsworkshop.org

October 21, 2015

#### **Proceedings**

**Burn-in & Test Strategies Workshop**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the BiTS Workshop Shanghai. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the BiTS Workshop Shanghai. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop Shanghai. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop Shanghai.

#### Proceedings

# LPDDR4 Signal & Power Performance Optimization By Hardware

#### Yuanjun Shi / Twinsolution R&D Xiao Yao / Hisilicon Test Solution R&D

2015 BiTS Workshop Shanghai October 21, 2015

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

October 21, 2015

East Meets West

#### BiTS Shanghai 2015

#### **Contents**

- DDR4 JEDEC Standard

- LPDDR4 PCB Channel & Socket SI Simulation

- LPDDR4 PCB and Socket Power Integrity Simulation

- Summary

LPDDR4 Signal & Power Performance Optimization By Hardware

Burn-in & Test Strategies Workshop

East Meets West

| DDR4 J | EDEC | <b>Standard</b> |

|--------|------|-----------------|

|        |      |                 |

|                                                                                                                          | <u>Symbol</u>                                                   | <u>Type</u> | Description                                     |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-------------------------------------------------|

| JEDEC Standard No. 209-4                                                                                                 | CK_t_A,<br>CK_c_A,<br>CK_t_B,<br>CK_c_B                         | Input       | Clock                                           |

| 2XX-ball 15mm x 15mm<br>0.4mm pitch, Quad-Channel<br>POP FBGA (top view)                                                 | CA[5:0]_A<br>CA[5:0]_B                                          | Input       | Command/Address<br>Inputs                       |

|                                                                                                                          | DQ[15:0]_A,<br>DQ[15:0]_B                                       | I/O         | Data Input/Output:<br>Bi–direction data<br>bus. |

| Partial Enlarge Map of DDR12345678910ADNUVSSVDDCA4.sVDDZ01.sVDD0D015.sVDD2D013.sBVSSVDDCA4.sVSSCA5.sVSSZ00.sVSSD014.sVSS | DQS[1:0]_t_A,<br>DQS[1:0]_c_A,<br>DQS[1:0]_t_B,<br>DQS[1:0]_c_B | I/O         | Data Strobe                                     |

| This case only study one group signal pin<br>across all four group signal pins, and only<br>include DQ pin.              | VDDQ,<br>VDD1,<br>VDD2                                          | Supply      | Power Supplies                                  |

| 10'=                                                                                                                     | VSS, VSSQ                                                       | GND         | GND                                             |

| Burn-in & Test Strategies Workshop                                                                                       | nance Optimization By                                           | Hardware    | 3                                               |

Burn-in & Test Strategies Workshop

East Meets West

#### **DDR4 JEDEC Standard**

| Clock Jitter Specification |           | Table 88 — Clock AC Timings |     |             |     |             |     |             |     |       |       |

|----------------------------|-----------|-----------------------------|-----|-------------|-----|-------------|-----|-------------|-----|-------|-------|

| Parameter                  | Symbol    | LPDDR4-1600                 |     | LPDDR4-2400 |     | LPDDR4-3200 |     | LPDDR4-4266 |     | Units | Notes |

| Farameter                  | Symbol    | Min                         | Max | Min         | Max | Min         | Max | Min         | Max | Units | Notes |

| Clock Timing               |           |                             |     |             |     |             |     |             |     |       |       |

|                            |           |                             |     |             |     | _           |     |             |     |       |       |

| Clock period jitter        | tJIT(per) | -70                         | 70  | -50         | 50  | -40         | 40  | <b>)</b> -  | TBD | ps    |       |

|             |                                                     | 1600/1867 <sup>A</sup> |      | 2133/2400 |      | 3200 |      | 4266 |      | Unit | NOTE    |

|-------------|-----------------------------------------------------|------------------------|------|-----------|------|------|------|------|------|------|---------|

| Eye Diagram | Specification                                       | min                    | max  | min       | max  | min  | max  | min  | max  | onne |         |

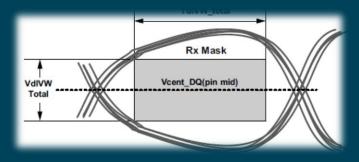

| VdIVW_total | Rx Mask voltage - p-p total                         | -                      | 140  | -         | 140  | -    | 140  | -    | 120  | mV   | 1,2,3,5 |

| TdIVW_total | Rx timing window total<br>(At VdIVW voltage levels) |                        | 0.22 |           | 0.22 | -    | 0.25 |      | 0.25 | UP   | 1,2,4,5 |

Eye diagrams are a very successful way of quickly and intuitively assessing the quality of a digital signal, for example <u>Overlaying of bit</u> and <u>noise level</u>. So Eye diagrams is a very important tools to analysis signal integrity of high speed interconnectors. On other hand we also can utilize the Eye diagram to minimize the delaying of bit as well as the transmission performance of system.

Burn-in & Test Strategies Workshop

LPDDR4 Signal & Power Performance Optimization By Hardware

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

4

East Meets West

#### LPDDR4 PCB Channel & Socket SI Simulation

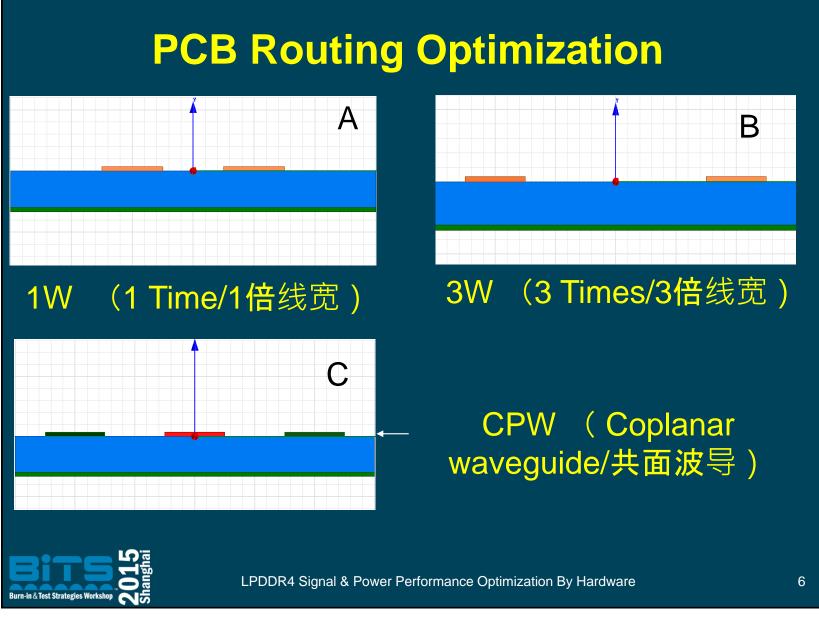

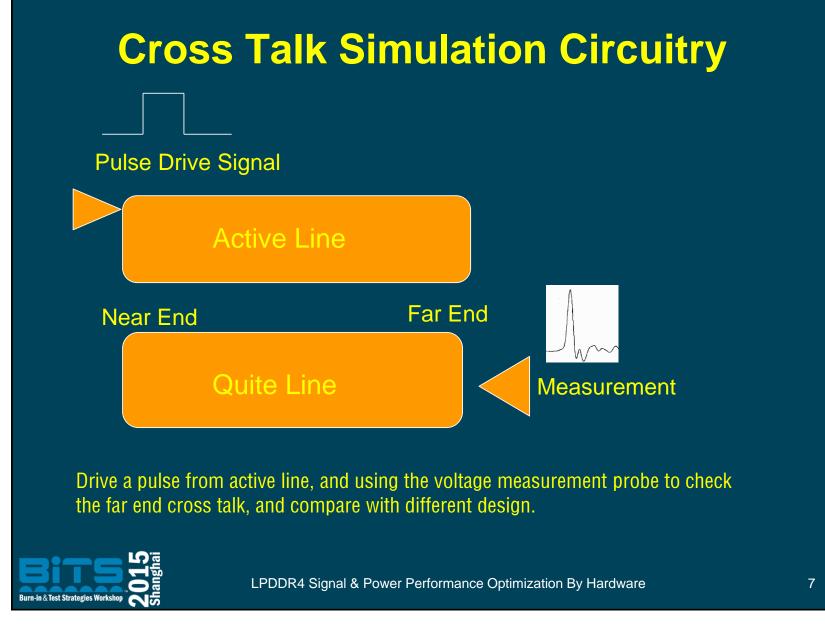

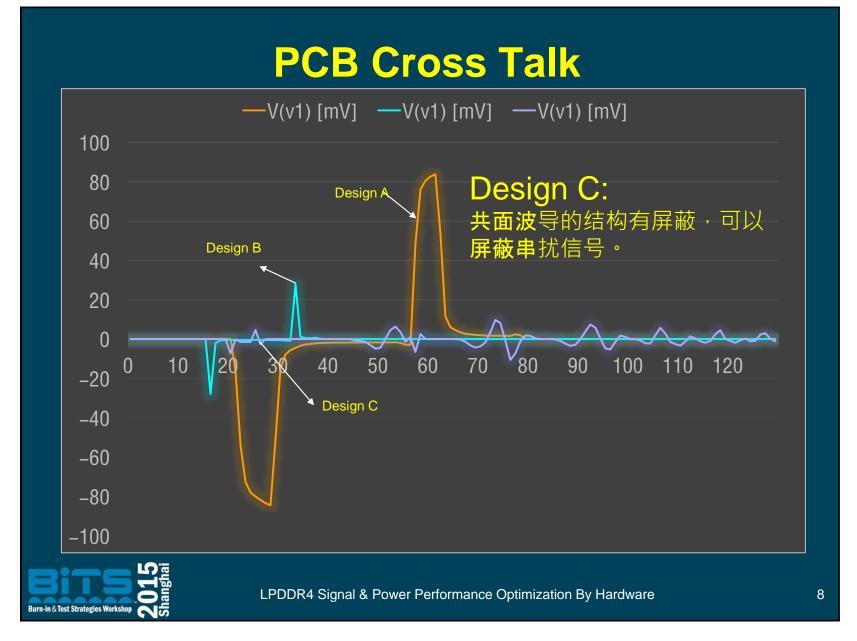

- PCB routing optimization

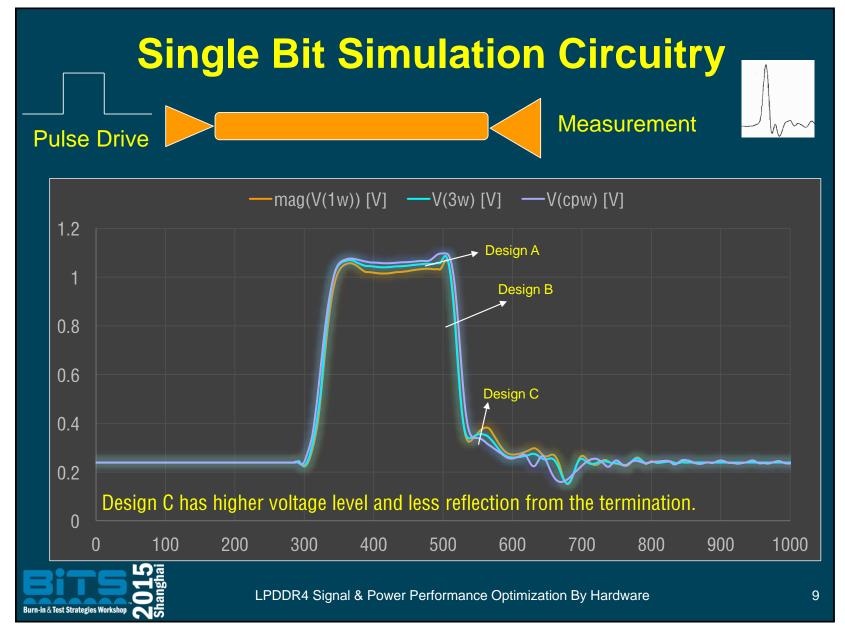

- Single Bit Performance

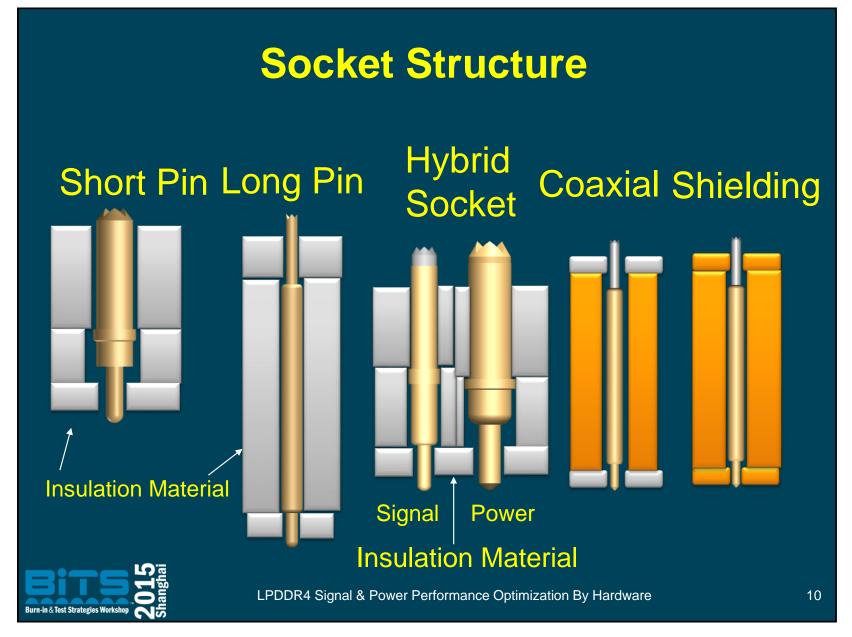

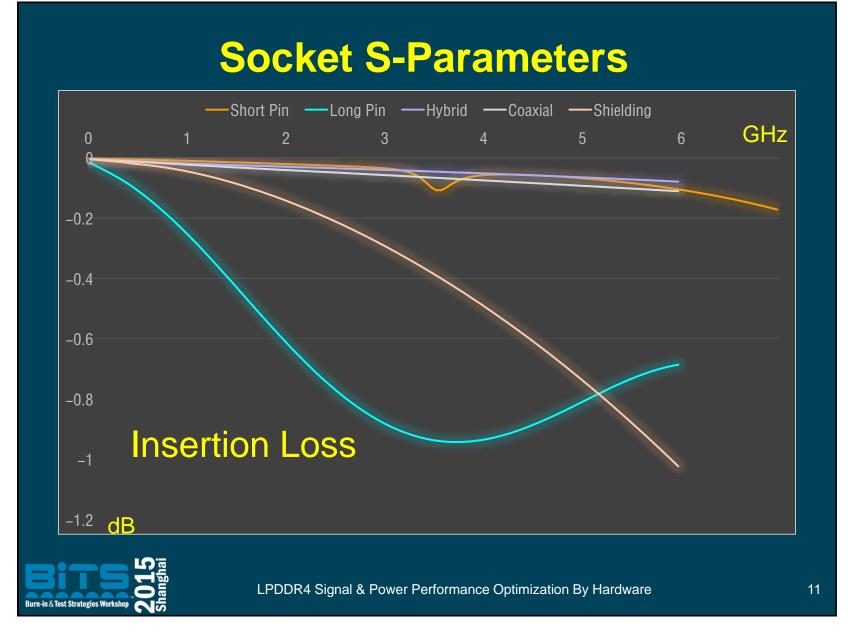

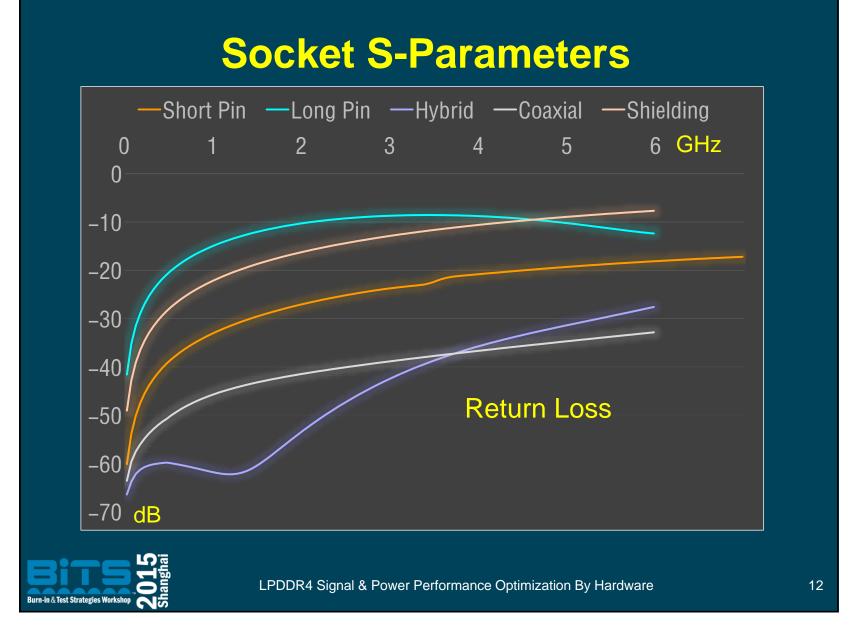

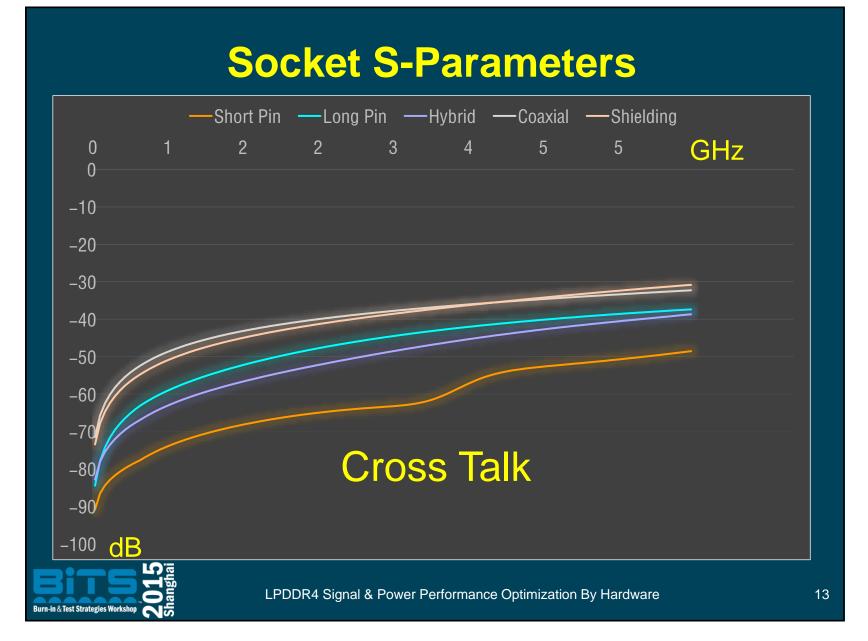

- S-Parameter Comparison Across Different Socket Structure

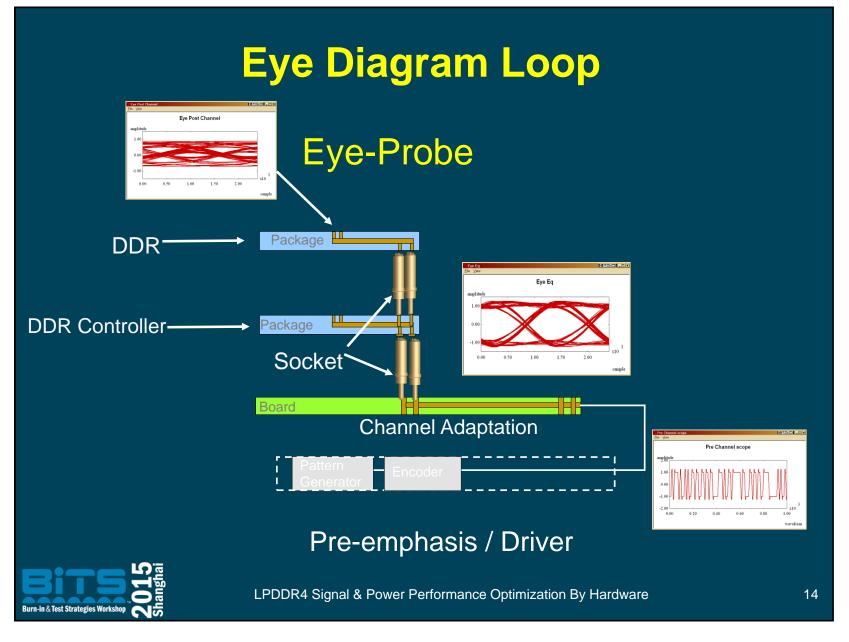

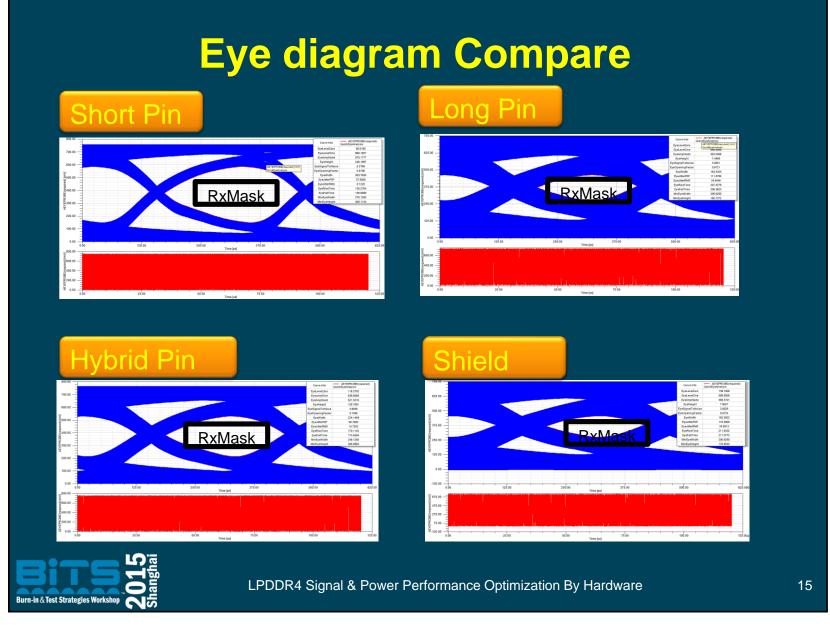

- Eyediagm analysis across different socket structure

LPDDR4 Signal & Power Performance Optimization By Hardware

Burn-in & Test Strategies Workshop

East Meets West

Burn-in & Test Strategies Workshop

East Meets West

**Burn-in & Test Strategies Workshop**

Session 2 Presentation 4

#### **BiTS Shanghai 2015**

East Meets West

**Burn-in & Test Strategies Workshop**

**Burn-in & Test Strategies Workshop**

East Meets West

#### **BiTS Shanghai 2015**

**Burn-in & Test Strategies Workshop**

East Meets West

Burn-in & Test Strategies Workshop

East Meets West

Burn-in & Test Strategies Workshop

East Meets West

**Burn-in & Test Strategies Workshop**

East Meets West

Burn-in & Test Strategies Workshop

East Meets West

**Burn-in & Test Strategies Workshop**

East Meets West

### Eye diagram Summary

| <b>Structure</b> | <u>Jitter</u> | VdiVW mV |

|------------------|---------------|----------|

| Short Pin        | 0.038         | 247      |

| Long Pin         | 0.112         | 7.5      |

| Hybrid           | 0.069         | 129      |

| Coaxial          | 0.031         | 298      |

| Shielding        | 0.117         | 7.9      |

#### Jitter Spec: 0.04 TdivW: 79ps VdiVW: 140mV

LPDDR4 Signal & Power Performance Optimization By Hardware

16

**Burn-in & Test Strategies Workshop**

East Meets West

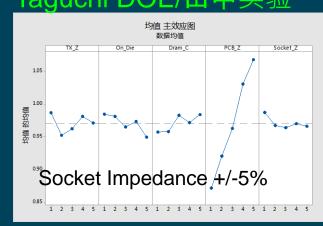

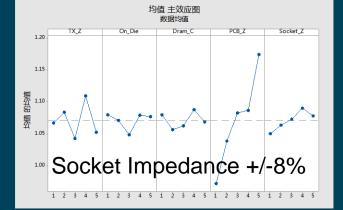

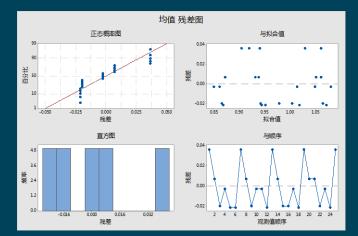

# High volume manufacturing sensitivity analysis

# **Channel Parameters**

Tx driver impedance (ohm) On-die-termination (ohm) DRAM Ci (pF) PCB trace impedance (ohm) Socket Impedance(ohm) <u>Variation</u>

34 +/- 10% 60 +/- 20% 2 +/- 10% 55 +/- 15% 50+/-5%

LPDDR4 Signal & Power Performance Optimization By Hardware

Burn-in & Test Strategies Workshop

East Meets West

## High volume manufacturing sensitivity analysis

LPDDR4 Signal & Power Performance Optimization By Hardware

**Burn-in & Test Strategies Workshop**

Burn-in & Test Strategies Worksho

East Meets West

**Burn-in & Test Strategies Workshop**

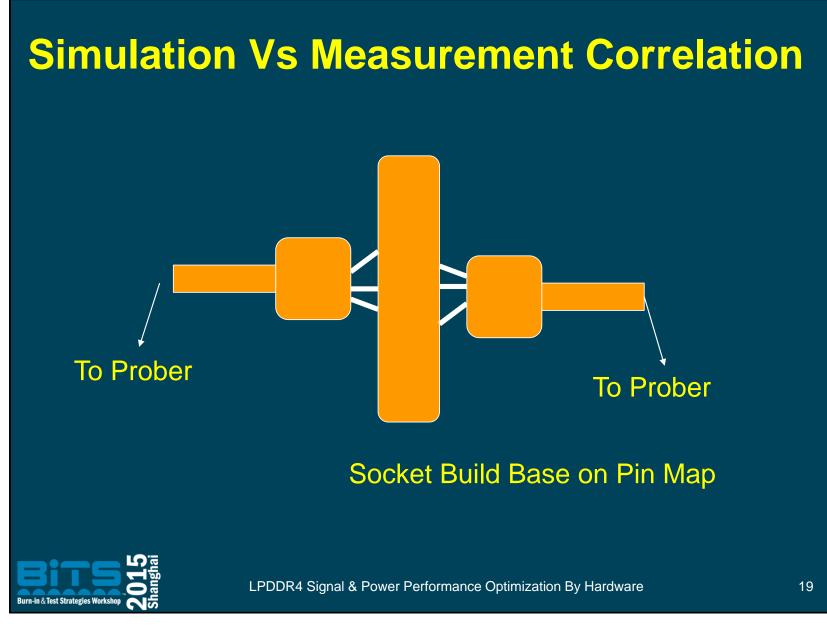

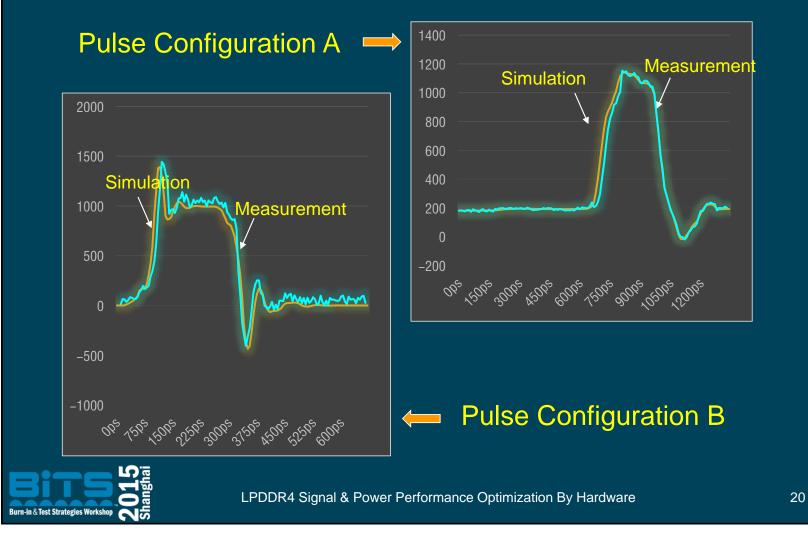

#### **Simulation Vs Measurement Correlation**

**Burn-in & Test Strategies Workshop**

East Meets West

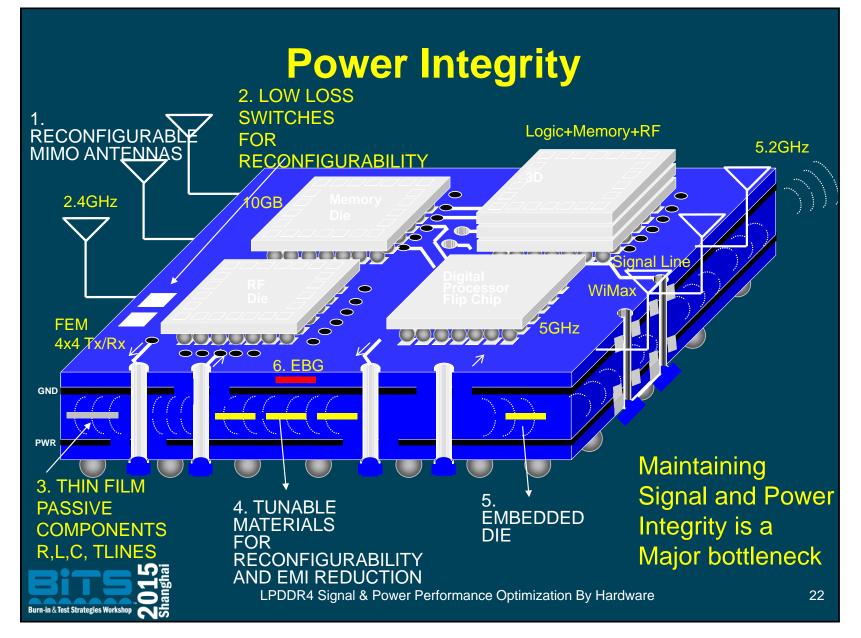

#### **LPDDR4 PI Simulations**

- PI Basic

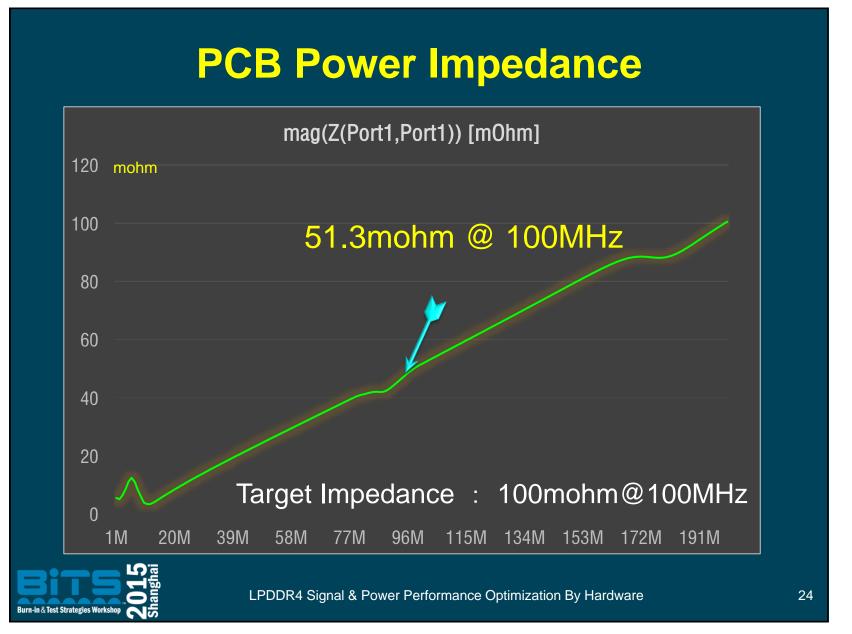

- PCB Impedance

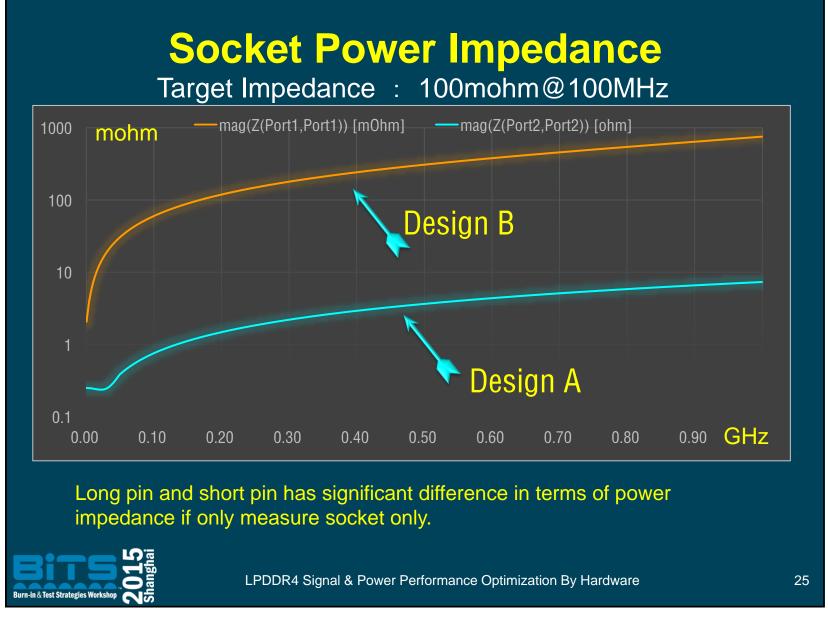

- Socket Power Impedance Vs System Impedance

- Impedance Optimization

LPDDR4 Signal & Power Performance Optimization By Hardware

21

Burn-in & Test Strategies Workshop

East Meets West

**Burn-in & Test Strategies Workshop**

**Burn-in & Test Strategies Workshop**

East Meets West

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

October 21, 2015

East Meets West

Burn-in & Test Strategies Workshop

East Meets West

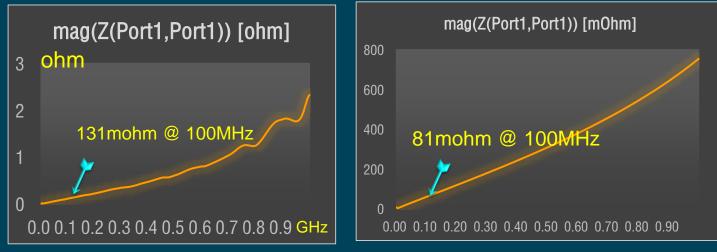

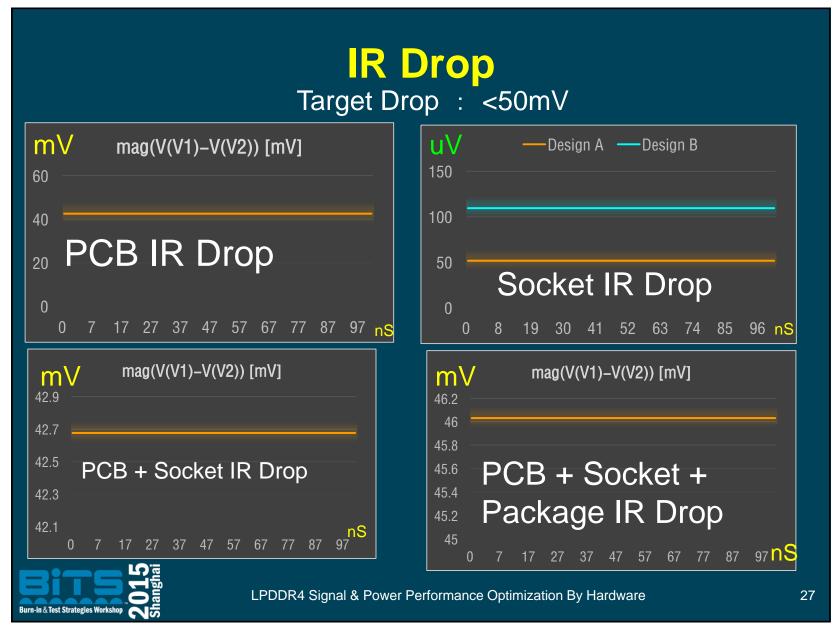

#### PCB + Socket + Package Impedance Target Impedance : 100mohm@100MHz

#### Before

#### After optimized

- 1. Increase the power pane width, and short the distribution length.

- 2. Optimize the pin length and diameter.

- 3. Although socket is not the main factor for the power impedance, however an optimized socket design and contactor selection also help the power impedance certain.

LPDDR4 Signal & Power Performance Optimization By Hardware

26

**Burn-in & Test Strategies Workshop**

Session 2 Presentation 4

#### **BiTS Shanghai 2015**

East Meets West

**Burn-in & Test Strategies Workshop**

East Meets West

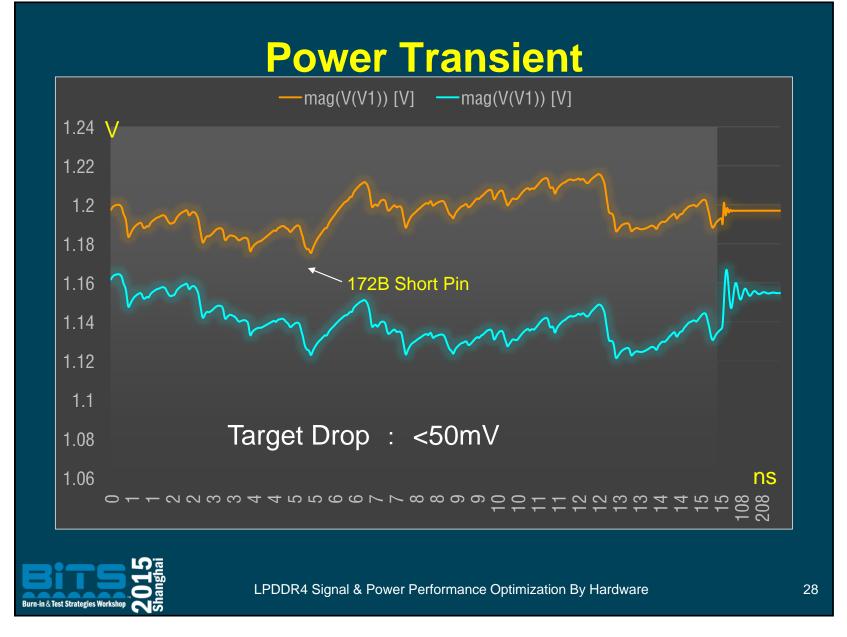

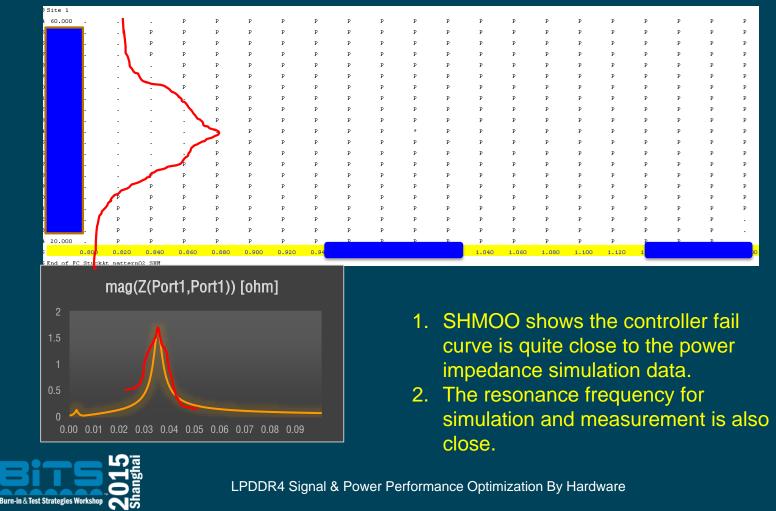

#### Power Impedance Vs Shmoo Measurement

**Burn-in & Test Strategies Workshop**

www.bitsworkshop.org

29

East Meets West

**Burn-in & Test Strategies Workshop**

East Meets West

#### **BiTS Shanghai 2015**

#### Summary

- Discussion one method to study whether the hardware can meet the LPDDR4 specification.

- Discussion one method to identify the main factor for the whole SI chain.

- Optimize the socket and pin layout to meet the power impedance performance.

- Utilize Shmoo to correlate the power impedance data.

LPDDR4 Signal & Power Performance Optimization By Hardware

31

Burn-in & Test Strategies Workshop