Burn-in & Test Strategies Workshop

www.bitsworkshop.org

#### **Proceedings**

**Burn-in & Test Strategies Workshop**

# Presentation / Copyright Notice

The presentations in this publication comprise the pre-workshop Proceedings of the BiTS Workshop Shanghai. They reflect the authors' opinions and are reproduced here as they are planned to be presented at the BiTS Workshop Shanghai. Updates from this version of the papers may occur in the version that is actually presented at the BiTS Workshop Shanghai. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop or the sponsors.

There is NO copyright protection claimed by this publication. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop Shanghai.

#### Proceedings

# The Economics of Semiconductor Test Challenges and Opportunities for 2016

# John West VLSIresearch

2015 BiTS Workshop Shanghai October 21, 2015

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

# **Overview**

- What's happening now?

- What's next?

- How will this impact the cost of test?

- Review

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

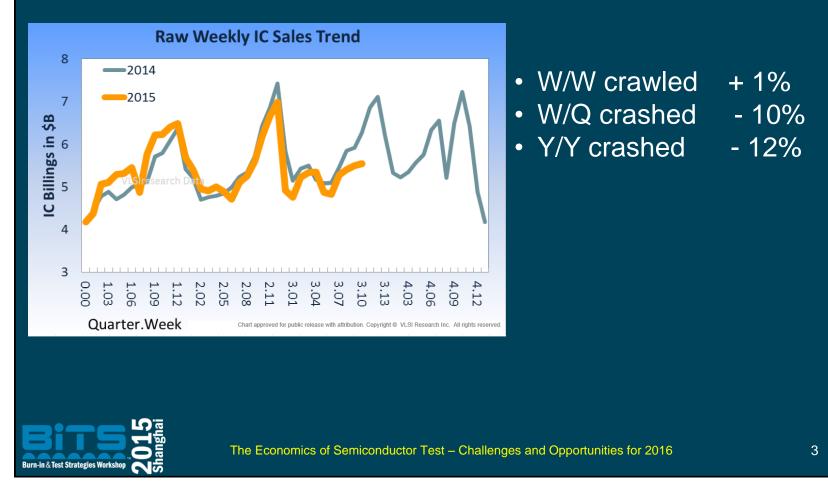

#### **Semiconductors – Into Negative Territory**

Raw IC Sales: weekly data for 2015 mapped over 2014

Burn-in & Test Strategies Workshop

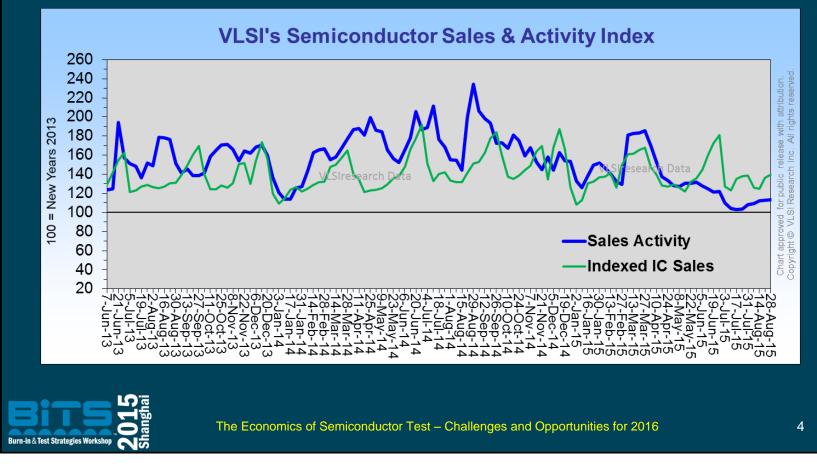

#### **Semiconductors – Into Negative Territory**

#### Trending down since August 2014

**Burn-in & Test Strategies Workshop**

# **Key Indicators**

- Inventory to billings ratio for semiconductors trending upwards to 1.5 months

- Chip prices falling rapidly after 2 years' stability

- Peak capacity utilization rate reached 90% this summer, compared to 95% in 2014

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

Burn-in & Test Strategies Workshop

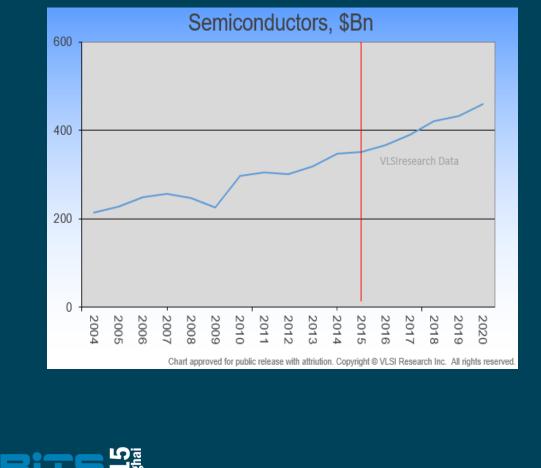

# Industry Growth – Needs a New Driver

2015 is flat at 0.7% 2016 up 4.4%

Long-term Growth 5.6%

Electronics Demand Weak: last 4 years below long term trend

Burn-in & Test Strategies Workshop

Burn-in & Test Strategies Work

www.bitsworkshop.org

The Economics of Semiconductor Test - Challenges and Opportunities for 2016

#### Next generation devices to drive near term growth..

- Server/High Performance Computing

- ARM based devices

- Personal Computing

- Merging Tablet and PC

- Communications

- 4G LTE

- Expansion to mid-tier phones

- Network upgrades

- 64bit Application processors

- Next Gen WLAN

- Next Generation PCI Express

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

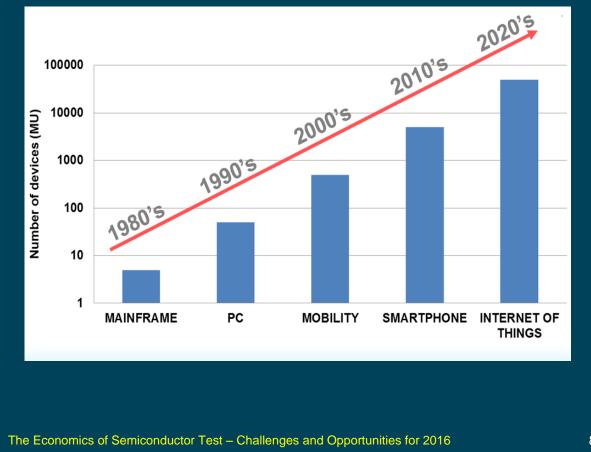

The power of 10 required to drive next wave of growth

**Burn-in & Test Strategies Workshop**

Burn-in & Test Strategies Works

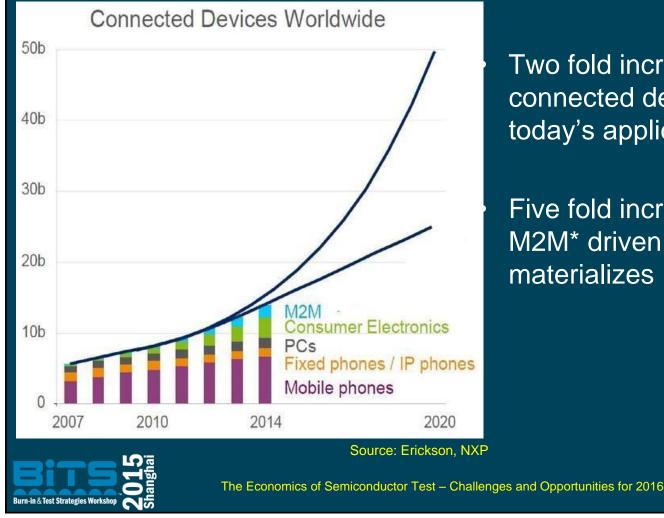

# Volume of Devices Will Explode

Two fold increase in connected devices in today's applications

Five fold increase, if M2M\* driven expansion materializes

**Burn-in & Test Strategies Workshop**

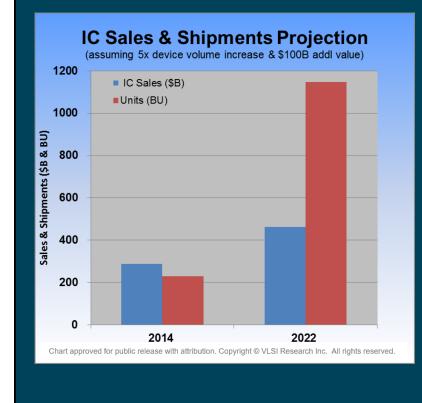

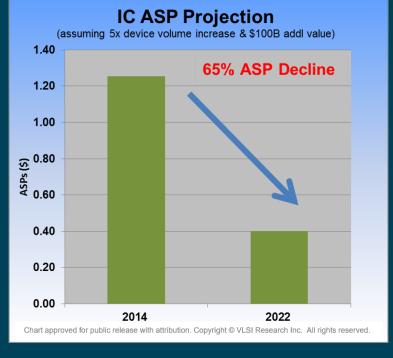

# **IC ASPs Have to Be Significantly Lower**

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

10

Burn-in & Test Strategies Workshop

# Lower ASP's Impact on Manufacturing

#### **INDUSTRY ECONOMICS**

- Moore's law has to continue

- Productivity gains have to continue

- Higher throughputs

- Better yields

- Improved Time-to Market

- Bigger factories

- Industry concentration

- 450mm

#### **TEST ECONOMICS**

- Better, faster, cheaper testers

- Burden on Test OEMs

- Better, faster, cheaper DFT

- Burden on internal test development

- Higher level of parallel testing

- Multi-wafer production test?

- Higher level parallelism at package test

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

# **Two Test Challenges for IoT**

How to test all of the IoT devices at low cost?

How to test the high end devices for cloud infrastructure?

- Very large volumes

- Short test times

- Leadless packages

- Small die sizes

- Highly efficient manufacturing

- Wide range of products –

ICs, MEMS, Sensors, etc

- Time to Volume

- 20nm and below devices

- 3D integration

- Highly customized manufacturing

- Time to Quality -> Ramp Risk

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

12

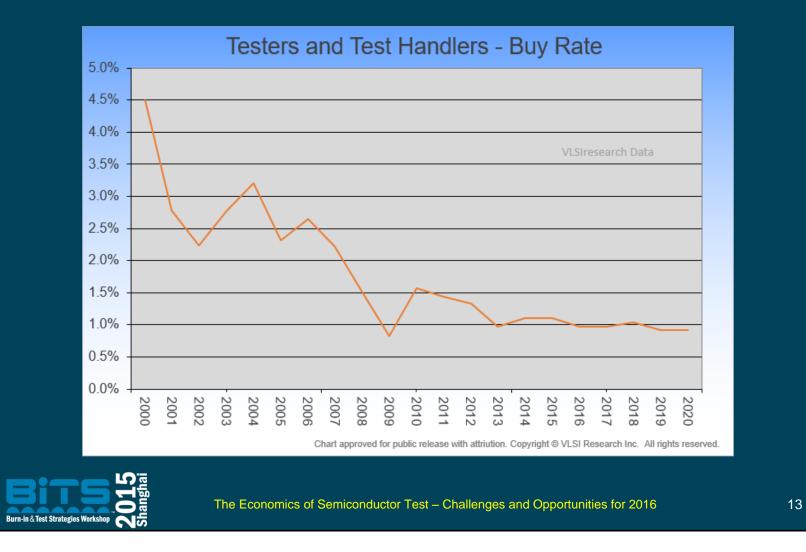

# Spending on Test Equipment is Not Growing..

**Burn-in & Test Strategies Workshop**

# How is This Possible?

Parallel Test

**Modular Testers**

**Design For Test**

Increased use of OSATS - higher utilization rates and lower costs

Consolidation – ATE vendors and Chipmakers

Probe Cards and Load Boards with Higher Functionality

But other (difficult to quantify) costs are growing...

Systems test, software, and overtime

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

14

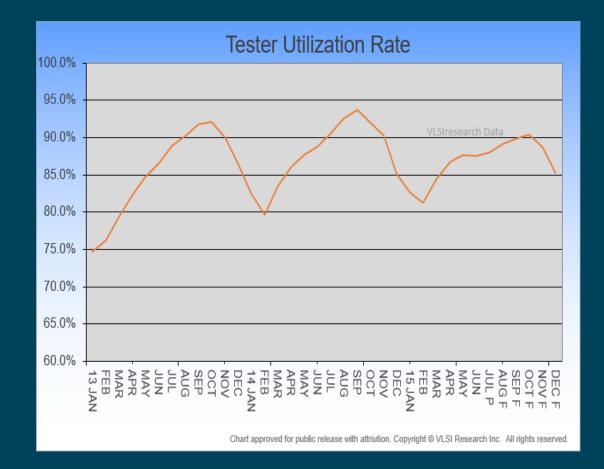

# **Tester Utilization**

Consistently above 80%

Enabled by OSATS and flexible test platforms

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

15

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

# **Consolidation**

Top 5 ATE companies account for 88% of market in 2014

Advantest and Teradyne account for 78% of total test sales

Xcerra, DGC Systems and SPEA combined make up the next 10%

35 other suppliers provide the remaining 12%

Chipmakers Consolidating too:

Intel / Altera NXP / Freescale Cypress / Spansion Qualcomm / CSR Avago / LSI / Broadcom? Triquint / RF Micro Infineon / International Rectifier Others...

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

16

**Burn-in & Test Strategies Workshop**

# **Test Consumable Costs Going Up...**

Probe Card, Socket and Interface Board Costs causing concern with chipmakers.

Not just cost issues. Chipmakers often have to accept a lower level of performance than they would like at the leading edge.

Long lead times for probe cards and interface boards

But consumables do add functionality to ATE

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

Test Consumables, \$M 1750 1500 1250 1000 750 500 Probe Cards 250 Test & Burn-In Sockets Interface Boards 0 200 2002 2004 200 2000 200: 2008 2009 2018 2005 2006 2010 2012 2013 2014 2015 2016 2017 2019 Chart approved for public release with attribution. Copyright © VLSI Research Inc. All rights reserved

17

**Burn-in & Test Strategies Workshop**

#### **Semiconductor Test in China**

Chinese OSATs

JCET in top 10 Others gaining share

5% of probe cards going to China

10% of test and burn-in sockets going to China

Expect trend to continue as cost pressure increases and more chips made in China

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

18

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

# **Challenges and Opportunities**

Usual issue: overall cost of test is going up

Some costs hard to measure for the industry as a whole what is the right amount to spend on test?

Not helped by restricted information transfer and lack of transparency between companies in the supply chain

No one has all the solutions and it's a problem for everyone - big and small

Test is getting more difficult...

...so developing the right test strategy and right partners is more critical than ever

The Economics of Semiconductor Test – Challenges and Opportunities for 2016

19