### **Proceedings Archive**

### **Proceedings Archive**

$S_{\text{ession}} \, 3$

Valts Treibergs

Session Chair

**BiTS Workshop 2015 Schedule**

## Frontiers Day

Monday March 16 4:30 pm

#### **Wafer Level Pots of Gold**

"Coplanarity Analysis of WLCSP Spring Probe Head"

Jiachun (Frank) Zhou, Daniel DelVecchio, & Cody Jacob - Smiths Connectors

"Pushing the envelope in DFM (Design for Manufacturing) for 0.2 mm

Pitch WLCSP Socket"

Paul Gunn, Muhammad Syafiq, & Takuto Yoshida - Test Tooling Solutions Group

"Space Transformer PCB For Testing 200 μm WLCSP"

Khaled Elmadbouly - Smiths Connectors

### **Proceedings Archive**

#### Copyright Notice

The presentation(s)/paper(s) in this publication comprise the Proceedings of the 2015 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2015 BiTS Workshop. This version of the papers may differ from the version that was distributed in hardcopy & softcopy form at the 2015 BiTS Workshop. The inclusion of the presentations/papers in this publication does not constitute an endorsement by BiTS Workshop or the workshop's sponsors.

There is NO copyright protection claimed on the presentation content by BiTS Workshop. However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop. All rights reserved.

Wafer Level Pots of Gold - Wafer Level Chip Scale Packaging (WLCSP)

# **Space Transformer PCB** For Testing 200 µm WLCSP

## Khaled Elmadbouly **Smiths Connectors**

2015 BiTS Workshop March 15 - 18, 2015

#### **Contents**

- What is the Space Transformer PCB

- How it gets used in the Probe Head

- Comparing Probe Head with Load Board vs. Traditional Probe Card

- Comparing PCB with MLC and MLO

- The Challenges of PCB

- Test and Validation

- Summary

### What is the Space Transformer PCB

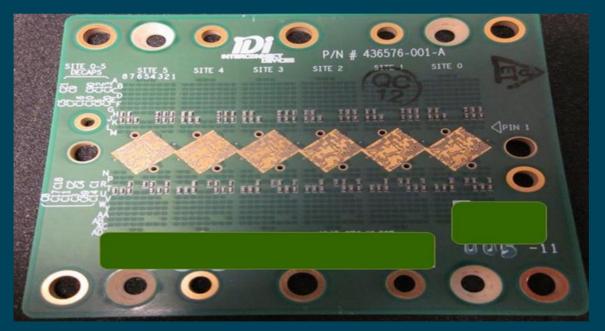

Standard pitch extender PCB to fan out the 200um DUT pins to 0.7mm pitch or larger for standard load board fabrication process

#### **How it Gets Used in the Probe Head**

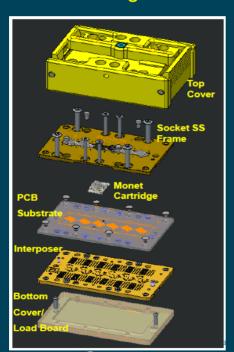

Space transformer connects the Monet 200um probe head to load board through a low profile spring probe interposer

For Probing Wafer

# Comparing Probe Head with Load Board vs. Traditional Probe Card

| Parameter                      | Load Board with Probe Head smiths connectors Proprietary Design                                                                                      | Traditional Design Probe Card                                                                                                            |  |

|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| Application                    | Probe wafer and final packages                                                                                                                       | Probe wafer only                                                                                                                         |  |

| Multi-Sites<br>Limitation      | No limit (up to max tester resources)                                                                                                                | Size restriction for tooling                                                                                                             |  |

| Maintenance                    | <ul> <li>Field service repairable</li> <li>When a probe is damaged, the cartridge for a broken site can be replaced for quick PH recovery</li> </ul> | <ul> <li>Non field service repairable</li> <li>When a probe is damaged,<br/>the entire PH is down and<br/>need to be replaced</li> </ul> |  |

| Cost Of<br>Ownership           | PH can be refurbished when probes reach end of life                                                                                                  | PH will be retired when probes reach end of life                                                                                         |  |

| High Speed<br>Signal Integrity | Acceptable                                                                                                                                           | Acceptable                                                                                                                               |  |

| High Power<br>Delivery         | Superior                                                                                                                                             | Acceptable                                                                                                                               |  |

Wafer Level Pots of Gold - Wafer Level Chip Scale Packaging (WLCSP)

## **Comparing PCB with MLC and MLO**

| Parameter                    | Standard PCB<br>smiths connectors<br>Proprietary Design | MLO (Multi-layer Organic) Thin/ Thick Film Substrate | MLC<br>Multi-Layers Ceramic |

|------------------------------|---------------------------------------------------------|------------------------------------------------------|-----------------------------|

| Flatness                     | Acceptable                                              | Need Improvement                                     | Best                        |

| Thermal<br>Performance       | Acceptable                                              | Need Improvement                                     | Best                        |

| Rigidity                     | Acceptable                                              | Need Improvement                                     | Best                        |

| High Power Delivery          | Acceptable                                              | Need Improvement                                     | Acceptable                  |

| Hole's True Position to Pads | Acceptable                                              | Acceptable                                           | Poor                        |

| 16-Layers Average            | Acceptable                                              | Acceptable                                           | Too Thick                   |

| Thickness                    | 1.3 to 1.6mm range                                      |                                                      | 3 to 5mm                    |

| Via Resistance               | Acceptable                                              | Acceptable                                           | High Resistance             |

| High Speed Signal Integrity  | Acceptable Up to 6Ghz                                   | Acceptable                                           | Poor                        |

## The Challenges of PCB

The success of the probe head relies heavily on the success of the space transformer PCB

- PCB flatness will have big effect on tip to tip coplanarity of the probe head (first to last touch)

- Alignment hole true position accuracy is very critical for pin to pad alignment

- RF signals need special routing

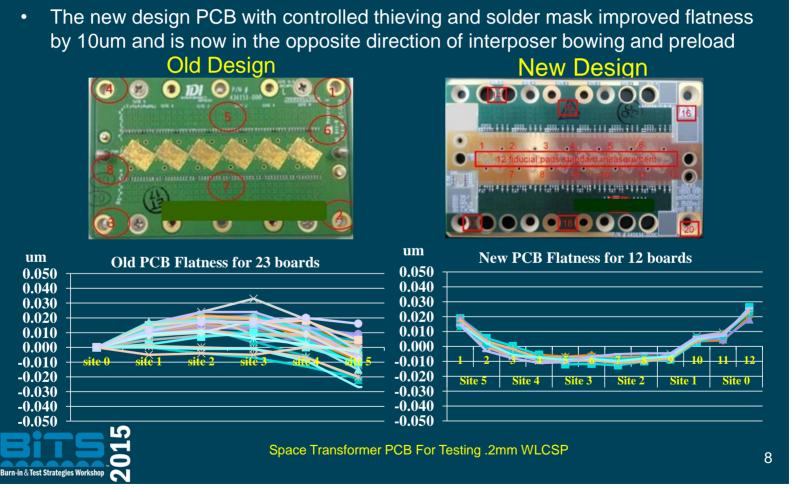

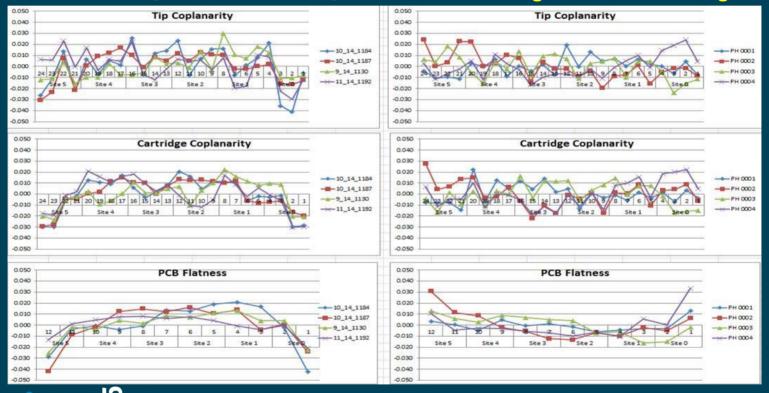

## **PCB Flatness**

The old design PCB had a flatness issue in the same direction of the bowing induced by the spring probe interposer preload.

## **Probe Head Flatness**

The new SS frame structure and the improved PCB flatness design contributed significantly to reduce the bowing by 30um

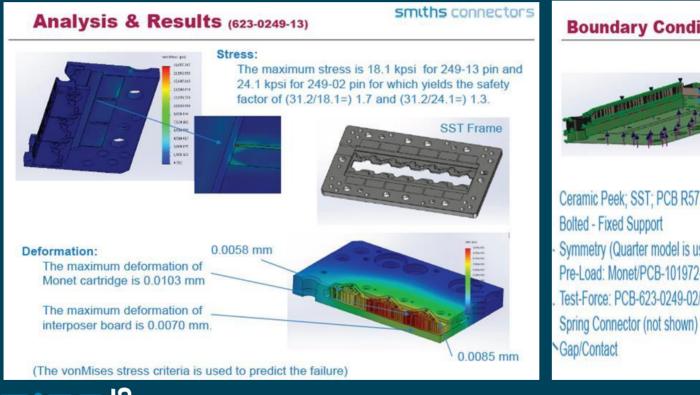

#### **Boundary Conditions**

Ceramic Peek; SST; PCB R5775

Bolted - Fixed Support

Symmetry (Quarter model is used)

Pre-Load: Monet/PCB-101972-000: Total: 2430

Test-Force: PCB-623-0249-02/13; Total 1521

## **Probe Head & PCB Flatness**

The overall PH coplanarity and the bowing was reduced by 30um after improving the structure of the PH frame and PCB flatness.

4 PH using the Old PCB design

Same PH using the New PCB design

Space Transformer PCB For Testing 200 µm WLCSP

10

Burn-in & Test Strategies Workshop

Wafer Level Pots of Gold - Wafer Level Chip Scale Packaging (WLCSP)

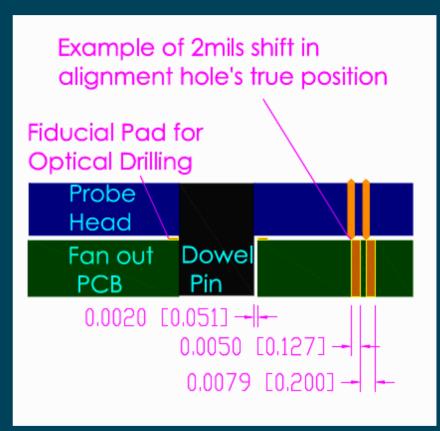

## **Alignment Hole True Position**

Placing fiducial pads around alignment holes in PCB with true position of +/-0.001" is a standard practice for POP interposer PCB, however for these 200um WLCSP PCB, the target pad is too small, therefore we developed additional fiducial pads to achieve precision PH optical alignment

Space Transformer PCB For Testing 200 µm WLCSP

11

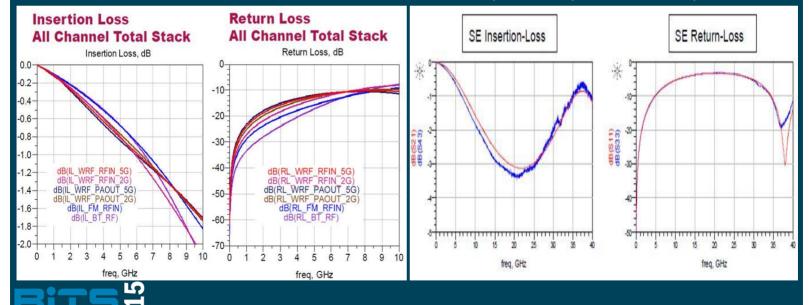

## **RF Signal Routing**

Developed special routing for RF signal to meet 6GHz speed requirement.

This routing was simulated then verified by actual measurement not only for the PCB but also for the entire Probe Head

Simulation vs Actual Measurements: IL: -1 dB, 6.8GHz; RL: -10dB, 6.0GHz

Burn-in & Test Strategies Workshop

Burn-in & Test Strategies Workshop

www.bitsworkshop.org

Space Transformer PCB For Testing 200 µm WLCSP

March 15-18, 2015

12

## **Test and Validation**

Design and set up 4-wire Kelvin Cres board to measure leakage and 100% Cres for every space transformer PCB and probe head

#### **Test and Validation** Example of Cres report for each probe head WLCSP- 395 - 0.2mm 6-Sites Cres Report SN# 1165 SN# 1151 40-0814-1142 08/05/2014 SN# 1123 SN# 1142 SN# 1143 PH SN SN# 1146 RF Avrg Cres RF STD DEV 0.069 0.071 0.057 0.063 0.071 0.089 0.084 0.060 0.065 0.123 0.073 0.074 0.066 Signal Avrg Cres 0.4330.419 0.438 0.412 0.454 0.464 0.447 0.408 0.418 0.404 0.435 0.451 0.431 Signal STD DEV 0.094 0.074 | 0.068 | 0.068 | 0.107 | 0.105 | 0.107 | 0.112 | 0.115 | 0.114 | 0.095 | 0.098 | 0.097 ligh Cre Pins Max **Socket Cres Criteria's** Avrg Cres Cres Site 0 Site 1 Site 2 Site 3 Site 4 Site 5 0.8mm 0.2mm Bumps 0.500 1.000 Name Type Net Name Number 0.232 0.256 0.237 PCIE TDP0 0.357 0.274 0.287 0.281 0.221 0.357 0.235 0.201 0.195 0.194 0.233 0.297 0.216 0.172 0.193 0.171 PCIE RDPO 0.337 0.268 0.290 0.337 0.244 0.195 0.289 0.326 0.267 0.206 0.117 0.208 0.240 0.330 0.330 0.201 PCIE RDNO 0.2470.323 0.265 0.299 0.229 0.204 0.283 0.231 0.307 0.323 0.265 0.182 0.253 0.178 0.302 0.279 0.296 0.194 0.178 0.169 USB3 TDP 0.25 0.318 0.273 0.316 0.233 0.218 0.271 0.155 0.211 0.301 0.312 0.318 0.316 0.293 0.201 0.231 0.185 0.266 0.215 0.205 0.259 USB3 TDN 0.371 0.219 0.212 0.214 0.352 0.364 0.317 0.325 0.371 0.297 0.203 0.171 0.194 0.250 0.252 0.244 0.223 0.235 BT REG ON 0.357 0.447 0.377 0.385 0.328 0.342 0.361 0.339 0.426 0.410 0.393 0.284 0.313 0.303 0.415 0.447 0.377 0.291 0.360 0.270 182 0.390 0.324 GPIO\_13 0.429 0.360 0.461 0.375 0.382 0.352 0.352 0.326 0.362 0.473 0.345 0.373 RF\_SW\_CTRL\_12 184 0.392 0.410 0.393 0.365 0.395 0.382 0.370 0.406 0.404 0.407 0.354 0.358 0.337 0.379 0.388 0.364 0.474 0.426 181 RF\_SW\_CTRL\_8 0.352 0.433 0.343 0.353 0.345 0.310 0.433 0.340 0.384 0.304 0.379 0.372 0.359 0.373 0.427 0.392 0.311 0.320 0.302 0.350 RF\_SW\_CTRL\_4 0.439 0.387 0.392 0.439 0.385 0.318 0.37 0.370 0.370 0.363 0.307 0.369 0.325 0.302 0.279 0.313 0.339 0.343 0.318 PACKAGEOPTION 2 0.363 0.325 0.341 0.293 0.305 0.364 0.381 0.351 0.418 0.328 0.267 0.344 0.344 0.489 0.324 77 78 130 GPIO 2 0.41 0.430 0.384 0.441 0.401 0.319 0.325 0.385 0.429 0.377 0.398 0.402 0.413 0.437 0.426 0.414 0.362 0.320 0.479 GPIO 12 0.334 0.343 0.337 0.268 0.325 0.263 0.306 0.343 0.273 0.252 0.250 0.247 0.430 0.479 0.449 0.268 0.324 0.268 PS15 P15 PCIEUSB AVDD1P2 0.05 0.112 0.055 0.072 0.037 0.020 0.037 0.041 0.012 0.112 0.093 0.073 0.044 0.047 0.045 0.037 0.089 0.056 0.052 0.038 P16\_USB2\_AVDD33 0.208 0.379 0.189 0.211 0.141 0.093 0.177 0.112 0.274 0.218 0.231 0.379 0.321 0.303 0.161 0.205 0.168 0.189 0.175 PS19 P19\_VDDIO 0.103 0.090 0.036 0.014 0.091 0.089 0.016 0.072 0.024 0.100 0.037 0.012 0.103 0.060 0.066 0.059 0.024 P20\_WRF\_SYNTH\_VDD3P3 0.20 0.316 0.273 0.267 0.242 0.162 0.178 0.202 0.227 0.316 0.267 0.176 0.167 0.141 0.159 0.160 0.214 0.179 0.183 PS20 0.190 136 0.176 $0.12^{\circ}$ 0.079 0.127 0.089 0.111 0.139 0.175 0.107 0.176 0.157 0.100 0.140 0.126 PS21 P21 AVDD3P3 0.087 0.103 0.126 0.082 0.136 0.123 137 P22\_VDDIO\_RF 0.100 0.169 0.110 0.085 0.091 0.090 0.045 0.130 0.067 0.066 0.103 0.153 0.050 0.086 0.165 0.169 0.106 0.082 0.113 0.087 0.047 0.114 0.069 0.057 0.044 0.038 0.035 0.030 0.078 WRF XTAL VDD1P2 SEN 0.217 0.314 VOUT\_LNLDO\_SENSE 351 0.248 0.324 0.322 0.324 0.310 0.269 0.27 0.486 Space Transformer PCB For Testing 200 µm WLCSP 14 Burn-in & Test Strategies Workshop

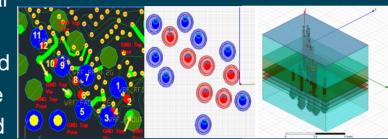

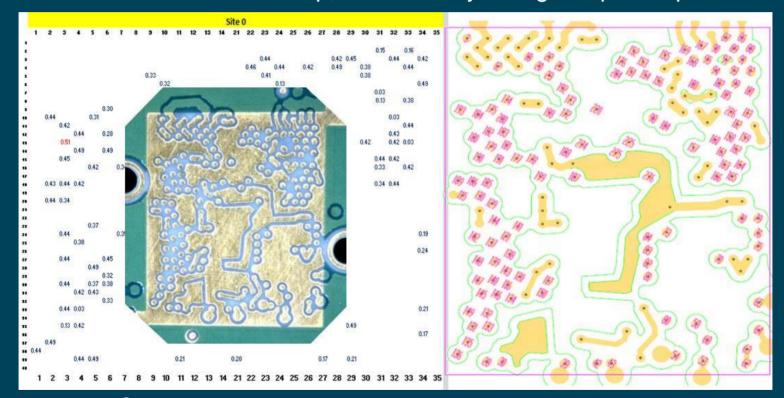

## **Test and Validation**

Example of a device pin map showing the Cres measurement of the exact location of each bump, to check any failing via, pad or pin

Space Transformer PCB For Testing 200 µm WLCSP

15

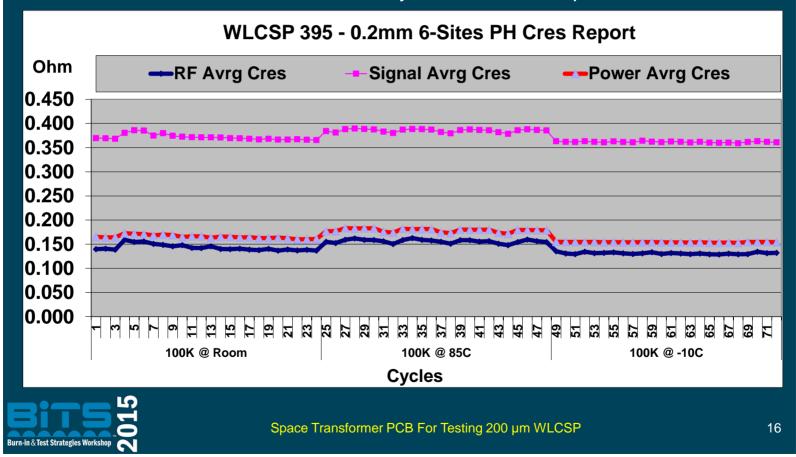

## **Test and Validation**

Example of first article PH validation to verify the space transformer PCB and the PH can withstand the 300K cycles at room temp, 85C and -10C

Wafer Level Pots of Gold - Wafer Level Chip Scale Packaging (WLCSP)

## Summary

- Over the past several years, development of this type of fan out PCB that gets integrated into PoP test sockets has been very successful, and more recently has been adapted to probe heads for multi-site ≥200um WLCSP

- The design standards of this space transformer PCB have been developed in such a way as to ensure precision alignment in HVM environment and in consideration of PCB fabrication, yield, and tolerances

- Overall performance is very satisfactory while there is still room for improvement, moving forward for the next generation Probe Head.