#### BRING IT TO THE BOARD (PCB)

The device under test (DUT) board is sometimes overlooked as a critical element in test-and burn-in strategies. This session brings PCBs into the limelight. The first presentation will cover some of the challenges that various DUT layouts present, demonstrating to semiconductor and ASICS design engineers the importance of considering final test hardware when designing device layouts. Another important consideration, covered in the second presentation, is the importance of performing RF characterization and simulation in-house to accurately measure the materials' electrical performance.

#### **Building Optimized Test PCB's Starts at the DUT**

Joe Birtola—CMR Summit Technologies

#### **High Frequency PCB Material Characterization and Simulation**

Ryan Satrom—Multitest

#### **MARKET REPORT**

As a bonus in this session, you'll get a look at the marketplace for test equipment and test consumables

### Market Trends in Test Equipment and Test Consumables

John West—VLSI Research

#### **COPYRIGHT NOTICE**

The paper(s) in this publication comprise the Proceedings of the 2013 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2013 BiTS Workshop. This version of the papers may differ from the version that was distributed in hardcopy & softcopy form at the 2013 BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by BiTS Workshop, LLC or the workshop's sponsors.

There is NO copyright protection claimed on the presentation content by BiTS Workshop, LLC. (Occasionally a Tutorial and/or TechTalk may be copyrighted by the author). However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop, LLC. All rights reserved.

Bring it to the Board (PCB)

### Reality is -

- Multiple vias in transmission lines.

- Lengthy Indirect trace paths.

- Narrow resistive higher-loss trace geometries.

- Congested signal launch and termination pin fields.

- Loads / circuitry in trace paths.

3/2013

Building Optimized Test PCB's Starts at the DUT

- 1

### Reality May =

- Signal performance below expectations.

- Higher board development cost

- Overall increased cost for Test

- Risk of project and test delays, failure to meet time to market expectations.

- A Grumpy CEO.

3/2013

Building Optimized Test PCB's Starts at the DUT

|   |      | Optim        | izing C       | evice        | Pin As       | signme       | ents         |       |      |

|---|------|--------------|---------------|--------------|--------------|--------------|--------------|-------|------|

| _ | 1    | 2            | 3             | 4            | 5            | 6            | 7            | 8     |      |

| Α | GND  | 1/0          | NO.           | I/O          | I/O          | SERDES VCC   | vcc          | NO.   |      |

| В | 110  | NO NO        | 110           | SERDES VCC   | SERDES VCC   | 1/0          | GND          | 110   |      |

| c | 110  | GND          | SERDES_VCC    | I/O          | SERDESZ_TE_H | SERDES2_TE_P | GND          | VCC   | - IA |

| D | 110  | 1/0          | 110           | GND          | INO          | VCC          | I/O          | 1/0   |      |

| E | 1/0  | 1/0          | VCC           | I/O          | GND          | VCCIO        | VCCIO        | VCCIO |      |

| F | 1/0  | VCC          | NO            | SERDES VCC   | I/O          | VCC          | VCC          | VCC   |      |

| G | 11/0 | I/O          | GND           | I/O          | GND          | NO           | I/O          | GND   | Gr   |

| н | I/O  | GND          | КO            | GND          | I/O          | VCC          | VCC          | NO    |      |

| J | I/O  | 1/0          | GND           | КO           | I/O          | GND          | GND          | GND   |      |

| К | VCC  | 1/0          | NO            | GND          | GND          | SERDES_VCC   | SERDES_VCC   | GND   |      |

| L | IAO  | GND          | GND           | КO           | IVO          | SERDES6_TE_M | SERDES6TE_P  | VCC   |      |

| М | GND  | I/O          | SERDES_VCC    | VCC          | VCCIO        | VCC          | VCC          | VCC   |      |

| N | IIO  | I/O          | КO            | ŀЮ           | SERDES6_RX_M | SERDES6RE_P  | VCCIO        | VCCIO |      |

| Р | 1/0  | 1/0          | GND           | КO           | NO           | GND          | VCC          | NO    |      |

| R | GND  | SERDES_VCC   | NO            | ΙłΟ          | GND          | SERDES_VCC   | КO           | GND   |      |

| Т | IVO  | SERDESZ_RE_P | SERDESZ_RE_H  | GND          | NO           | ΙłΟ          | GND          | NO    |      |

| U | VCC  | 1/0          | SERDES_VCC    | NO           | I/O          | NO           | NO           | NO    |      |

| ٧ | I/O  | VCC          | SERDES1_RX_P  | SERDES1_RX_H | GND          | SERDES1_TX_H | SERDES1_TX_P | GND   |      |

|   |      |              |               |              |              |              |              |       |      |

|   |      |              |               |              |              |              |              |       |      |

|   | LOOP | BACK NON     | I-OPTIMIZ     | ZED PIN P    | LACEMEN      | <u>T</u>     |              |       |      |

|   |      |              |               |              |              |              |              |       |      |

| 3 |      | В            | uilding Optin | nized Test P | CB's Starts  | at the DUT   |              |       |      |

| 10           | 11           | 12           | 13           | 14           | 15           | 16         | 17           | 18           |

|--------------|--------------|--------------|--------------|--------------|--------------|------------|--------------|--------------|

| I/O          | VCC          | 1/0          | 1/0          | 1/0          | I/O          | VCC        | I/O          | I/O          |

| I/O          | I/O          | GND          | 1/0          | GND          | 1/0          | 1/0        | GND          | I/O          |

| SERDES_VCC   | GND          | 1/0          | SERDES_VCC   | VCC          | 1/0          | VCC        | I/O          | 1/0          |

| 1/0          | 1/0          | VCC          | GND          | GND          | 1/0          | GND        | I/O          | 1/0          |

| VCCIO        | VCCIO        | VCCIO        | VCCIO        | SERDES_VCC   | 1/0          | 1/0        | I/O          | VCC          |

| VCC          | VCC          | VCC          | VCCIO        | 1/0          | 1/0          | 1/0        | I/O          | GND          |

| GND          | GND          | VCC          | VCCIO        | 1/0          | 1/0          | VCC        | I/O          | 1/0          |

| GND          | GND          | VCC          | VCCIO        | GND          | VCC          | GND        | GND          | I/O          |

| GND          | GND          | VCC          | VCCIO        | GND          | GND          | 1/0        | I/O          | I/O          |

| GND          | GND          | VCC          | VCCIO        | SERDES_VCC   | I/O          | I/O        | I/O          | I/O          |

| GND          | GND          | VCC          | VCCIO        | 1/0          | 1/0          | SERDES_VCC | I/O          | GND          |

| VCC          | VCC          | VCC          | VCCIO        | 1/0          | 1/0          | GND        | I/O          | I/O          |

| VCCIO        | VCCIO        | VCCIO        | VCCIO        | SERDES_VCC   | GND          | 1/0        | 1/0          | 1/0          |

| VCC          | SERDES4_RX_N | 1/0          | GND          | VCC          | 1/0          | 1/0        | I/O          | I/O          |

| GND          | SERDES4_RX_P | GND          | SERDES4_TX_N | SERDES4_TX_P | 1/0          | VCC        | GND          | 1/0          |

| 1/0          | TCI          | 1/0          | GND          | 1/0          | 1/0          | 1/0        | 1/0          | VCC          |

| SERDES3_RX_N | 1/0          | GND          | SERDES_VCC   | GND          | SERDESS_RX_N | GND        | 1/0          | GND          |

| SERDES3_RX_P | GND          | SERDES3_TX_N | SERDES3_TX_P | SERDES_VCC   | SERDESS_RX_P | SERDES_VCC | SERDES5_TX_N | SERDESS_TX_P |

|              |              |              |              |              |              |            |              |              |

|              |              |              |              |              |              |            |              |              |

| LOOP BAG     | CK OPTIMIZ   | ZED PIN PL   | ACEMENT      |              |              |            |              |              |

Bring it to the Board (PCB)

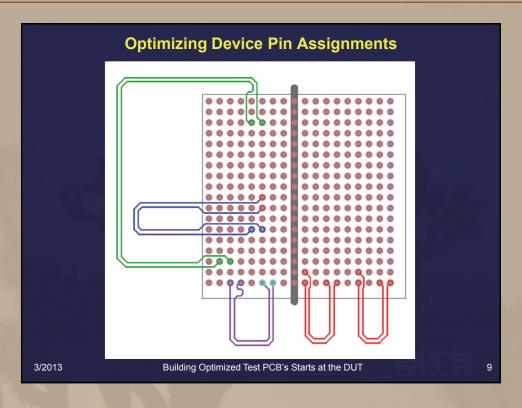

#### **High-Speed / Critical Signal Pin Placement**

- Locate loop-back, differential, RF signal pins at outer edge of package matrix (BGA)

- Assign to a location that promotes equal trace length at board level.

- Locate relative pair pins centrally, avoiding cross matrix loop-back routing.

- Assign these pins at a position that reduces routing through power pin fields.

3/2013

Building Optimized Test PCB's Starts at the DUT

| _    | _   | _       |                |              |               |              |            |       |       | _  |

|------|-----|---------|----------------|--------------|---------------|--------------|------------|-------|-------|----|

|      |     |         | Optir          | nizing l     | Device        | Pin As       | signme     | nts   |       |    |

|      |     |         |                |              |               |              |            |       |       |    |

|      |     | 1       | 2              | 3            | 4             | 5            | 6          | 7     | 8     | 9  |

|      | Α   | INO     | NO             | I/O          | 1/0           | IłO          | 1/0        | 1/0   | 1/0   |    |

|      | В   | I/O     | NO             | INO          | 1/0           | 110          | DGND       | 1/0   | DGND  | GN |

|      | С   | I/O     | IVO            | INO          | I/O           | I/O          | 1/0        | AVCC  | 11/0  |    |

|      | D   | NO      | NO             | NO           | I/O           | AVCC         | AVCC       | ASIG  | 1/0   |    |

|      | Ε   | NO      | IAO            | DGND         | IłO           | VCCIO        | VCCI0      | VCCIO | VCCIO |    |

|      | F   | IVO     | NO             | NO           | ИO            | VCCIO        | vcc        | VCC   | VCC   |    |

|      | G   | NO      | NO             | IAO          | DGND          | VCCIO        | ASIG       | DGND  | DGND  |    |

|      | н   | ISO     | КO             | ISO          | I/O           | ASIG         | VCC        | ASIG  | AGND  |    |

|      | J   | NO      | NO             | NO           | I/O           | VCCIO        | VCC        | DGND  | AGND  |    |

|      | K   | INO     | IAO            | I/O          | DGND          | VCCIO        | AGND       | AGND  | DGND  |    |

|      | L   | IVO     | DGND           | DGND         | AVCC          | AGND         | VCC        | DGND  | DGND  |    |

|      | М   | NO      | NO             | NO           | I/O           | ASIG         | AGND       | AGND  | VCC   |    |

|      | N   | IVO     | IAO            | NO           | IłO           | AGND         | DGND       | VCCIO | AGND  |    |

|      | Р   | NO      | IAO            | NO           | DGND          | AGND         | AVCC       | DGND  | ASIG  |    |

|      | R   | IAO     | DGND           | INO          | DGND          | NO           | AGND       | AVCC  | DGND  |    |

|      | Т   | I/O     | INO            | INO          | I/O           | DGND         | I/O        | DGND  | I/O   |    |

|      | U   | I/O     | I/O            | IIO          | I/O           | NO           | DGND       | I/O   | I/O   |    |

|      | ٧   | I/O     | IIO            | IIO          | I/O           | I/O          | I/O        | I/O   | I/O   |    |

|      |     |         |                |              |               |              |            |       |       |    |

|      |     |         |                |              |               |              |            |       |       |    |

|      |     | NON-C   | DTIMIZE        | MIVEDS       | ICNAL DI      | N PLACEM     | IENIT      |       |       |    |

|      |     | INCIN-C | F THVIIZEL     | IVIIAED 3    | IGNAL FII     | VELACEIV     | LIVI       |       |       |    |

|      |     |         | 17 11 11 11 11 |              |               |              |            |       |       |    |

| 3/20 | )13 |         |                | Building Opt | imized Test F | PCB's Starts | at the DUT |       |       | 1  |

Bring it to the Board (PCB)

|        |         | Optim    | izing D       | evice P      | in Assi       | ignme   | nts  |      |   |

|--------|---------|----------|---------------|--------------|---------------|---------|------|------|---|

| 9      | 10      | 11       | 12            | 13           | 14            | 15      | 16   | 17   | ٦ |

| 0      | I/O     | DGND     | IłO           | I/O          | ASIG          | ASIG    | 1/0  | 1/0  |   |

| ND     | I/O     | NO       | AVCC          | AGND         | AGND          | AGND    | AVCC | DGND |   |

| ю      | DGND    | DGND     | IAO           | ASIG         | AGND          | ASIG    | AGND | I/O  |   |

| 0      | I/O     | IAO      | DGND          | AGND         | AGND          | AGND    | NO   | NO   |   |

|        | VCCIO   | VCCIO    | VCCIO         | VCCIO        | ASIG          | ASIG    | КO   | IYO  |   |

|        | VCC     | VCC      | VCC           | VCCIO        | AGND          | ASIG    | КO   | DGND |   |

|        | DGND    | DGND     | DGND          | VCCIO        | ASIG          | AGND    | AVCC | NO   |   |

|        | DGND    | DGND     | VCC           | VCCIO        | AGND          | КO      | 1/0  | I/O  |   |

|        | DGND    | DGND     | VCC           | VCCIO        | AGND          | КO      | DGND | I/O  |   |

|        | DGND    | DGND     | VCC           | DGND         | AVCC          | DGND    | 1/0  | I/O  |   |

|        | DGND    | DGND     | DGND          | VCCIO        | NO            | AVCC    | NO   | NO   |   |

|        | VCC     | VCC      | VCC           | VCCIO        | NO            | I/O     | NO   | NO   |   |

|        | VCCIO   | VCCIO    | VCCIO         | VCCIO        | DGND          | КO      | 1/0  | I/O  |   |

| ES_VC  | IVO     | DGND     | 1/0           | 1/0          | I/O           | I/O     | 1/0  | I/O  |   |

|        | DGND    | NO       | DGND          | 1/0          | NO            | I/O     | DGND | ŀΟ   |   |

| 0      | I/O     | DGND     | I/O           | DGND         | NO            | I/O     | 1/0  | DGND |   |

| 10     | I/O     | NO       | 1/0           | 1/0          | I/O           | DGND    | 1/0  | I/O  |   |

| Ю      | I/O     | NO       | DGND          | 1/0          | 1/0           | NO      | 1/0  | NO   |   |

|        |         |          |               |              |               |         |      |      |   |

|        |         |          |               |              |               |         |      |      |   |

|        | OPTIMIZ | ED MIXED | )-SIGNAL      | PIN PLACI    | <u>EMENT</u>  |         |      |      |   |

| 3/2013 |         | В        | uilding Optim | ized Test PC | B's Starts at | the DUT |      |      |   |

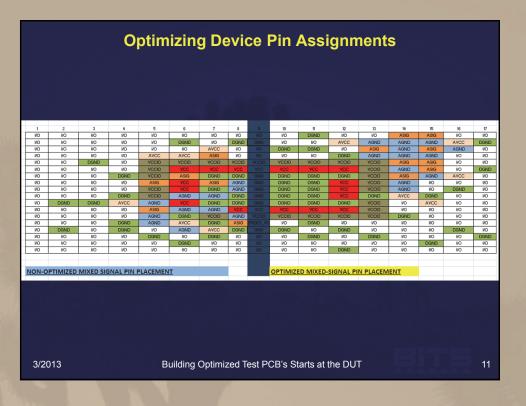

# Mixed Signal Package Pin Assignment Considerations

- Keep analog ground pins in same area of package array and away from digital ground

- Keep analog signal pins near analog ground pins. (likewise for digital pins)

- Keep analog power pins adjacent to analog ground pins for decoupling optimization.

3/2013

Building Optimized Test PCB's Starts at the DUT

|      |          | Optin     | nizing C       | Device F      | Pin Ass        | ignmer  | its   |       |       |

|------|----------|-----------|----------------|---------------|----------------|---------|-------|-------|-------|

|      |          |           |                |               |                |         |       |       |       |

|      | 1        | 2         | 3              | 4             | 5              | 6       | 7     | 8     |       |

|      |          | IAO       | IAO            | I/O           | 1/0            | 1/0     | I/O   | I/O   | 17    |

|      |          | IAO       | IłO            | IłO           | 1/0            | DGND    | 1/0   | DGND  | GI    |

|      | 1/0      | I/O       | КO             | I/O           | 1/0            | I/O     | AVCC  | 1/0   | 18    |

|      | 1/0      | I/O       | КO             | I/O           | AVCC           | AVCC    | ASIG  | 1/0   | 16    |

|      | 1/0      | I/O       | DGND           | ΙłΟ           | VCCIO          | VCCIO   | VCCIO | VCCIO | VC    |

|      | I/O      | I/O       | 1/0            | NO            | VCCIO          | VCC     | VCC   | VCC   | VC    |

|      | I/O      | I/O       | I/O            | DGND          | VCCIO          | ASIG    | DGND  | DGND  | GI    |

|      | I/O      | I/O       | NO             | NO            | ASIG           | VCC     | ASIG  | AGND  | GI    |

|      | I/O      | I/O       | I/O            | I/O           | VCCIO          | VCC     | DGND  | AGND  | GI    |

|      | I/O      | I/O       | I/O            | DGND          | VCCIO          | AGND    | AGND  | DGND  | GI    |

|      | 1/0      | DGND      | DGND           | AVCC          | AGND           | VCC     | DGND  | DGND  | GI    |

|      | 1/0      | IAO       | ΙłΟ            | I/O           | ASIG           | AGND    | AGND  | VCC   | VC    |

|      | 1/0      | IAO       | ΙłΟ            | I/O           | AGND           | DGND    | VCCIO | AGND  | VC    |

|      | 1/0      | I/O       | ΙłΟ            | DGND          | AGND           | AVCC    | DGND  | ASIG  | SERDE |

|      | I/O      | DGND      | NO             | DGND          | I/O            | AGND    | AVCC  | DGND  | GI    |

|      | I/O      | NO        | NO             | I/O           | DGND           | I/O     | DGND  | I/O   | N.    |

|      | I/O      | I/O       | NO             | I/O           | 1/0            | DGND    | NO    | NO    | 18    |

|      | 1/0      | IAO       | ΙłΟ            | IłO           | 1/0            | 1/0     | I/O   | NO    | 12    |

|      |          |           |                |               |                |         |       |       |       |

|      |          |           |                |               |                |         |       |       |       |

|      | NON-OPT  | IMIZED PO | W/FR PIN       | PLACEMEN      | UT.            |         |       |       |       |

|      | HOW OF I |           | A COLUMN       | - LACEIVIEI   | ••             |         |       |       |       |

| 3/20 | )13      | _         | Building Optir | mized Test PC | CB's Starts at | the DUT | Ę     |       |       |

|      | 10              | 11        | 12        | 13    | 14   | 15   | 16   | 17   |

|------|-----------------|-----------|-----------|-------|------|------|------|------|

|      | I/O             | DGND      | 1/0       | 1/0   |      | ASIG | 1/0  | 1/0  |

| )    | I/O             | 1/0       | AVCC      | AGND  |      | AGND | AVCC | DGND |

|      | I/O             | 1/0       | 1/0       | ASIG  | AGND | ASIG | AGND | 1/0  |

| _    | DGND            | DGND      | DGND      | AGND  | AGND | AGND | 1/0  | 1/0  |

| 0    | VCCI0           | VCCIO     | VCCIO     | VCCIO | ASIG | ASIG | 1/0  | 1/0  |

|      | VCC             | VCC       | VCC       | VCCIO | AGND | ASIG | 1/0  | DGND |

|      | DGND            | DGND      | DGND      | VCCIO | ASIG | AGND | AVCC | 1/0  |

|      | DGND            | DGND      | VCC       | VCCIO | AGND | 1/0  | I/O  | 1/0  |

|      | DGND            | DGND      | VCC       | VCCIO | AGND | 1/0  | DGND | 1/0  |

|      | DGND            | DGND      | VCC       | DGND  | AVCC | DGND | 1/0  | 1/0  |

|      | DGND            | DGND      | DGND      | VCCIO | I/O  | AVCC | 1/0  | 1/0  |

|      | VCC             | VCC       | VCC       | VCCIO | DGND | 1/0  | 1/0  | 1/0  |

| 0    | VCCIO           | VCCIO     | VCCIO     | VCCIO | DGND | 1/0  | I/O  | 1/0  |

| _vcc | I/O             | DGND      | 1/0       | DGND  | 1/0  | 1/0  | 1/0  | 1/0  |

|      | DGND            | 1/0       | DGND      | 1/0   | I/O  | I/O  | DGND | 1/0  |

|      | I/O             | DGND      | 1/0       | DGND  | I/O  | 1/0  | 1/0  | DGND |

|      | I/O             | 1/0       | 1/0       | I/O   | I/O  | DGND | 1/0  | 1/0  |

|      | I/O             | 1/0       | DGND      | 1/0   | I/O  | 1/0  | I/O  | 1/0  |

|      |                 |           |           |       |      |      |      |      |

|      |                 |           |           |       |      |      |      |      |

| 9    | <u>OPTIMIZE</u> | D POWER I | PIN PLACE | MENT  |      |      |      |      |

|      |                 |           |           |       |      |      |      |      |

Bring it to the Board (PCB)

# Optimized Pin Assignment Will Promote...

- Optimized test regimen / board performance.

- Expeditious board development.

- Lower board layer count and cost.

- A happy CEO!

3/2013

Building Optimized Test PCB's Starts at the DUT