## **STREAMLINING OPERATIONS**

Test operations, generally considered costly, yet necessary, add value to device manufacturing when optimized for efficiency. This session offers a variety of approaches that promise high yields, lean manufacturing, maximized performance at minimal costs, and optimized production times. The first paper discusses a method of incorporating multidimensional Monte Carlo analysis simulation with known design parameters to focus manufacturing improvement efforts and maximize alignment performance while minimizing costs. Presented next is a method for redefining test tooling design rules to gain process margin and prevent substrate chipping caused by test handler misalignment. Zero-cost, software based, virtual tool checkers that bring the whole production area towards a manufacturing LEAN direction is then discussed. Wrapping things up is a paper on a screwless socket and dual pin testing concept said to greatly enhance the robustness and efficiency of IC testing.

### Improving Socket Alignment Performance Using Monte Carlo Analysis Techniques and Manufacturing Controls

Daniel DelVecchio, Dustin Allison-Interconnect Devices Incorporated

**Tooling Stack-up Process Margin Improvement**

Mook Koon Wong, Boon Hor Phee-Intel Malaysia

### Zero Cost Virtual Tool Checker

Seong Guan Ooi—Intel Technology Sdn. Bhd.

### Enablers for Robust & Fast Online Trouble-shooting for High Parallelism Testing

Benedict Loh—Infineon Technologies Kohei Hironaka—NHK Spring Co. Ltd. Michelle Ng—TestPro

### **COPYRIGHT NOTICE**

The paper(s) in this publication comprise the Proceedings of the 2013 BiTS Workshop. The content reflects the opinion of the authors and their respective companies. They are reproduced here as they were presented at the 2013 BiTS Workshop. This version of the papers may differ from the version that was distributed in hardcopy & softcopy form at the 2013 BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by BiTS Workshop, LLC or the workshop's sponsors.

There is NO copyright protection claimed on the presentation content by BiTS Workshop, LLC. (Occasionally a Tutorial and/or TechTalk may be copyrighted by the author). However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author(s) or their companies.

The BiTS logo and 'Burn-in & Test Strategies Workshop' are trademarks of BiTS Workshop, LLC. All rights reserved.

# Tooling Stack-up Process Margin Improvement

Wong Mook Koon Phee Boon Hor Intel Malaysia

2013 BiTS Workshop March 3 - 6, 2013

# Agenda

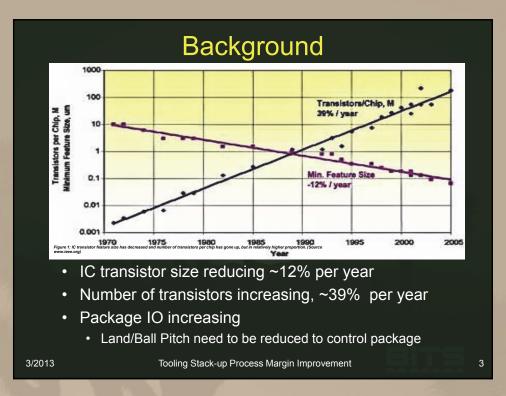

- Background

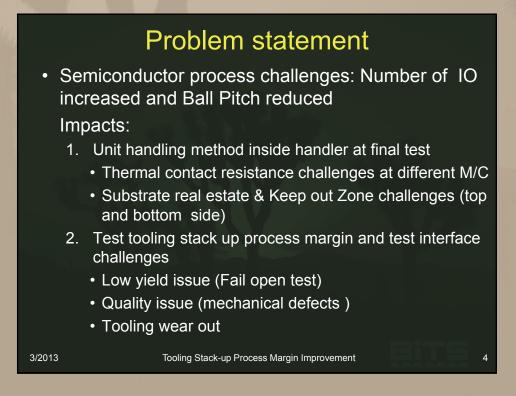

- Problem statement

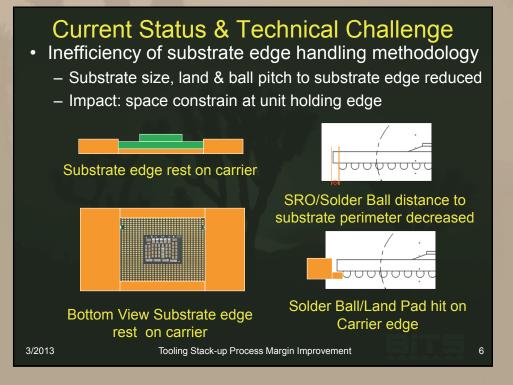

- Current Status and Technical Challenges

- Solution

- Check Result

- Summary

- Acknowledgement

3/2013

2

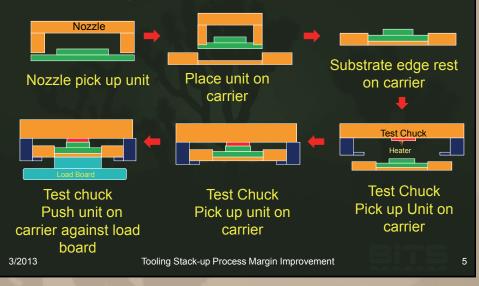

# **Current Status & Technical Challenge**

Unit handling method inside handler at final test -Substrate edge handling

# **Current Status & Technical Challenge**

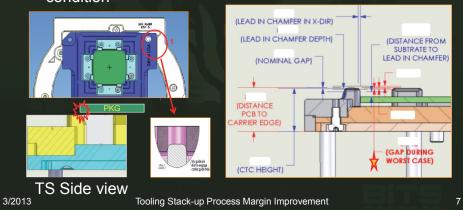

- Test tooling stack up process margin and test interface challenges

- Chuck Z-motion inside handler may cause package bottom

- surface to hit test socket's <u>Anvil Surface</u> under worst case condition

# <section-header><list-item><list-item><list-item><complex-block>

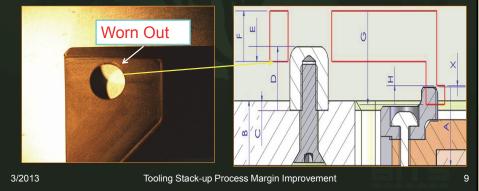

# **Current Status & Technical Challenge**

- Test tooling stack up process margin and test interface challenges

- Carrier guide hole deterioration due to occasional crash by guide pin and wear out

- Need to physically measure carrier guide hole dimensions to avoid substrate hit on Test Socket's top plate

11

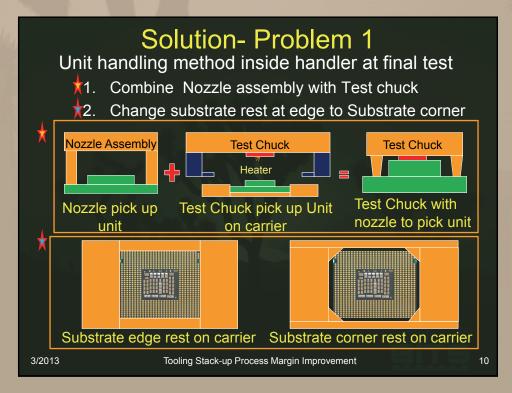

# Solution-Problem 1

Unit handling method inside handler at final test

|   | L | Unit handling Method                      | Need Bottom KOZ | Test Ball/Land Pad depopulate | Meet Thermal Resistance requirment | Substrate Warp | Cost effective |

|---|---|-------------------------------------------|-----------------|-------------------------------|------------------------------------|----------------|----------------|

|   | X | Substare edge(test Chuck with Carrier)    | Yes             | Yes                           | Yes                                | No             | No             |

| I | X | Combine Nozzle with Test Chuck            | No              | No                            | No                                 | No             | No             |

| ľ | X | Substrate corner(Test check with Carrier) | Yes             | Yes                           | Yes                                | No             | Yes            |

- 1<sup>st</sup> Substrate edge handling

- High land/ball pad depopulate

- Not cost effective due to increase in substrate real estate

- 2<sup>nd</sup> Combine Nozzle with Test Chuck

- Thermal resistance not met, need longer soak time to start of test

- Change equipment handler handling method, cost concern

- 3<sup>rd</sup> Substrate corner handling

- Cost effective

- Minimum solder ball depopulate

- Maintain current thermal performance and run rate

3/2013

Tooling Stack-up Process Margin Improvement

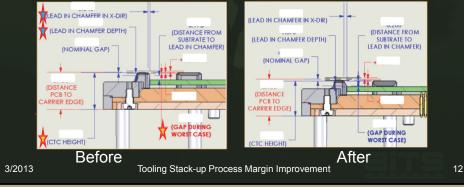

- Solution- problem 2 Test tooling stack up process margin and test interface challenges

- Re-design the Guide Plate to gain tooling stack up process margin

- · Optimize socket total height Increase Z-height Gap from negative to positive during unit to test socket pre engagement

- · Optimize Lead In chamfer depth Increase the X-directional allowance

- Solution- problem 2

Test tooling stack up process margin and test interface challenges

- Strengthen Seal plate guide hole of carrier with metal sheet reinforcement

- Carrier condition indication line to eliminate measurement

3/2013

|               |          | Ch                                   | eck resul              | ts             |             |

|---------------|----------|--------------------------------------|------------------------|----------------|-------------|

| D             | OOE      | Pusher Misalignment                  | Carrier' SP Guide hole | TS Guide plate | Chipping    |

|               | 1        | Worse case                           | degraded               | POR            | Yes         |

|               | 2        | Worse case                           | degraded               | New            | Yes         |

|               | 3        | Worse case                           | Good                   | POR            | Yes         |

| *             | 4        | Worse case                           | Good                   | New            | No          |

|               | 5        | No Worse case                        | degraded               | POR            | Yes         |

|               | 6        | No Worse case                        | degraded               | New            | Yes         |

| *             | 7        | No Worse case                        | Good                   | POR            | No          |

| $\rightarrow$ | 8        | No Worse case                        | Good                   | New            | No          |

|               |          | ummary                               |                        |                |             |

| - Unde        | er v     | vorst case Test                      | Check misalignm        | ient condition | i, substrat |

|               | <u> </u> | e will occur exce<br>ed socket guide | pt if carrier is in    | good conditio  | on + with   |

|               |          |                                      | not cause subst        |                |             |

- is in good condition, regardless of POR or optimized socket guide

- Conclusion •

- Controlling the carrier guide hole condition is crucial in determining the substrate damage risk

- Optimized socket guide will definitely buy additional process margin to prevent substrate damage

- 3/2013 Tooling Stack-up Process Margin Improvement 14

# Conclusion

### • Summary

- Optimized Test Socket Guide plate vertical wall and chamfer lead in depth demonstrated process margin improvement

- Carrier guide hole condition is key factor to ensure good quality tooling stack up

- Substrate Corner handling method is solution for Thermal concern, Substrate real estate and land pad/Ball depopulation issue

```

3/2013

```

Tooling Stack-up Process Margin Improvement

15

- LT Yew (Test Engineering Manager)

- TS Yeoh (Principal Engineer)

- Jensen, Morten S. (Committee member)

16