# **ARCHIVE 2012**

#### **ANALYZE THIS**

What good is it to have optimized test devices if the characterization and analysis processes aren't up to speed as well? This session focuses on the whole picture. We open with methods for taking device specifications and translating them into test contactor requirements to reduce the impact of testing the device in the contactor. Next we'll move on to the challenges of balancing signal integrity with power integrity through the socket and PC board. The session wraps up with two presentations investigating parameters; the first discusses key parameters of pulse current testing and their significance and the second shares some crucial parameters in thermal simulations.

# Understanding Specs to Better Simulate Solder-to-Board Performance

Jeff Sherry—Johnstech International

# Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

Thomas P. Warwick, Al Seier—R&D Circuits, Inc.

#### **Pulse Current Testing: Parameters and Their Significance**

Gert Hohenwarter—GateWave Northern, Inc.

#### **Key Parameters in Thermal Simulations**

Larry Furman, Joseph Ortega—Plastronics Sockets & Connectors

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the Proceedings of the 2012 BiTS Workshop. They reflect the authors' opinions and are reproduced here as they were presented at the 2012 BiTS Workshop. This version of the papers may differ from the version that was distributed in hardcopy & softcopy form at the 2012 BiTS Workshop. The inclusion of the papers in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication (occasionally a Tutorial and/or TechTalk may be copyrighted by the author). However, each presentation is the work of the authors and their respective companies: as such, it is strongly encouraged that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

**Analyze This**

Understanding Specs to

Better Simulate Solder-to-Board

Performance

# Jeff Sherry Johnstech International

2012 BiTS Workshop March 4 - 7, 2012

**Johnstech**°

#### Agenda

- Changes in Contactor performance

- -Inductance effects

- -Thermal or current carrying effects

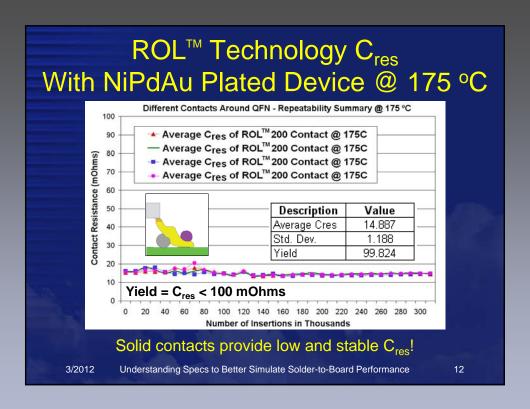

- Cres and repeatability

- Importance of design margins

- Effects of device configurations

- Mechanical considerations

- Test methods

- Conclusion

3/2012

Understanding Specs to Better Simulate Solder-to-Board Performance

**Analyze This**

#### Causes of Changes in Performance

- Variations in signal path

- Variations in insertion position

- Variations in oxides and debris buildup

- Variations in package platings

- Variations in I/O pitch

- Variations in location of ground or return path

- Variations in insertion forces and speed

3/2012

Understanding Specs to Better Simulate Solder-to-Board Performance

3

#### High Gain Amplifier Spec Sheet Тур. 2.4 GHz Transmit **Front End Module** IEEE802.11b, IEEE802.11g, FGC CFG 15.247, .205,.209, EN, and JDEC Power Supp 3.0 3.3 V<sub>REG</sub> Voltage PA in "ON" state **Schematic** OFF 0.00 PA in "OFF" state Output Power 54Mbps, OFDM 54Mbps, V<sub>CC</sub>≥3.0V 18.5 dBm 19.5 54Mbps, OFDM 54Mbps, V<sub>CC</sub>≥3.3V 11Mbps, CCK, V<sub>CC</sub>≥3.0V 11b 22 3.3 $P_{OUT(g)}$ =Rated Output Power, 54Mbps OFDM, 50 $\Omega$ , se P<sub>OUT(b)</sub>=20dBm 1Mbps CCK, note 2 Adjacent Channel Power V<sub>CC</sub>≥3.3V, meeting 11b spectral mask 6000 -51 4.2 Testing at hot will stress device if die temperature is exceeded! Understanding Specs to Better Simulate Solder-to-Board Performance

|                                                | Specification |      | Unit | Condition |                                                                                                                                                       |

|------------------------------------------------|---------------|------|------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                      | Min.          | Тур. | Max. | Oilit     | Condition                                                                                                                                             |

| Typical Conditions                             |               |      |      |           | Temp=25°C, Frequency=2.3GHz to 3.8GHz<br>depending on the evaluation board tune,<br>V <sub>CC</sub> =V <sub>PC</sub> =6.0V unless otherwise specified |

| Frequency                                      | 2.3           |      | 2.5  | GHz       | Tune A                                                                                                                                                |

|                                                | 2.5           |      | 2.7  | GHz       | Tune B                                                                                                                                                |

|                                                | 2.7           |      | 2.9  | GHz       | Tune C                                                                                                                                                |

|                                                | 3.3           |      | 3.8  | GHz       | Tune D                                                                                                                                                |

| Output Power                                   |               | 30   |      |           | Tune A, B, C, D                                                                                                                                       |

| EVM                                            |               | 3.0  |      | %         | 802.16e 16QAM 3/4 modulation,<br>P <sub>OUT</sub> =+30dBm                                                                                             |

| Stability                                      | 0             |      | 33   | dBm       | PA should be stable when P <sub>OUT</sub> is measured<br>from OdBm to 33dBm                                                                           |

| Gain                                           |               | 11   |      | dB        |                                                                                                                                                       |

| Gain Flatness                                  |               |      | 3    | dB        | Peak-Peak over any 300 MHz bandwidth                                                                                                                  |

| Noise Figure                                   |               | 5    |      | dB        |                                                                                                                                                       |

| Operating Current                              |               | 1.3  |      | Amp       | RF P <sub>OUT</sub> =+30 dBm, V <sub>O0</sub> =6V                                                                                                     |

| Quiescent Current                              |               | 900  |      | mA        |                                                                                                                                                       |

| _VPC Current                                   |               | 10   |      | mA        | No RF                                                                                                                                                 |

| Leakage Current                                |               | 100  |      | uA        |                                                                                                                                                       |

| Turn-on Time from Setting of V <sub>BIAS</sub> |               |      | 400  | ns        | Output stable within 90% of final gain                                                                                                                |

| input Return Loss                              |               | -15  | -10  | dB        | In tune band                                                                                                                                          |

| Output Return Loss                             |               | -10  | -7   | dB        | In tune band                                                                                                                                          |

| Stable into Output VSWR                        |               |      | 4:1  |           | No spurs above -47 dBm                                                                                                                                |

**Analyze This**

# Material Softening/Melting Voltages

| <u>Material</u> | Softening Volts (V) | Melting Volts (V) |

|-----------------|---------------------|-------------------|

| Aluminum        | 0.10                | 0.30              |

| Iron            | 0.19                | 0.19              |

| Nickel          | 0.16                | 0.16              |

| Copper          | 0.12                | 0.43              |

| Zinc            | 0.10                | 0.17              |

| Silver          | 0.09                | 0.37              |

| Cadmium         | 0.15                | 0.16              |

| Tin             | 0.07                | 0.13              |

| Gold            | 0.08                | 0.43              |

| Palladium       | 0.57                | 0.57              |

| Lead            | 0.12                | 0.19              |

| 60Cu,40Zn       | 0.20                | 0.25              |

Source: Timron Scientific Inc., Electrical Contacts And Electroplates In Separable

Connectors

The low melting voltage of Matte Tin can cause test problems!!

3/2012 Understanding Specs to Better Simulate Solder-to-Board Performance

7

#### **Current Carrying Example Calculations**

#### For Matte Tin Plated Device

| Contact Resistance | Current to Soften | Current to Melt |

|--------------------|-------------------|-----------------|

| 20 mOhms           | 3.5 A             | 6.5A            |

| 50 mOhms           | 1.4 A             | 2.6 A           |

| 100 mOhms          | 0.7 A             | 1.3 A           |

| 150 mOhms          | 0.47 A            | 0.87 A          |

| 200 mOhms          | 0.35 A            | 0.65 A          |

| 250 mOhms          | 0.28 A            | 0.52 A          |

| 500 mOhms          | 140 mA            | 260 mA          |

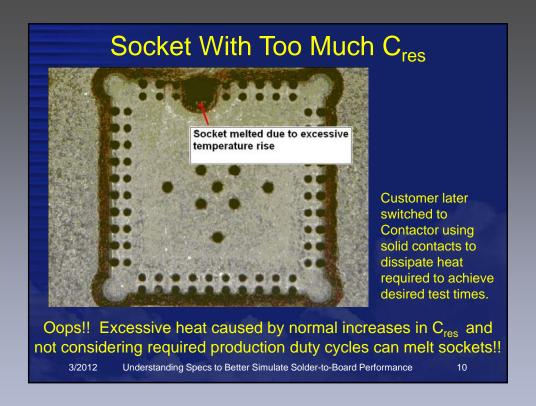

Lower  $C_{\text{res}}$  solutions enable higher current carrying capability!!

3/2012 Understanding Specs to Better Simulate Solder-to-Board Performance

turn-in & Test Strategies Workshop

**Analyze This**

#### Importance of Design Margin

- Contact resistance will increase over time

- Debris or oxides may impact C<sub>res</sub> or ground inductance path

- IR drop across interfaces could cause softening or melting of device plating

- Variation in signal path and ground location will vary electrical performance

# All of these will affect Guard Bands and Test Limits

NOTE: The contactor will always add more ground inductance and resistance to the path than solder-to-board performance!

3/2012 Understanding Specs to Better Simulate Solder-to-Board Performance

**Analyze This**

#### **Mechanical Considerations**

- Wiping action vs. no wiping action effects MTBA and cleaning intervals

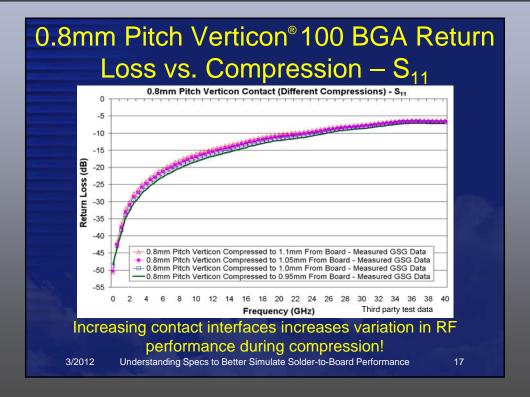

- One piece vs. multiple parts : more parts = more variability

- Handler interface issues insertion speed

- Maintenance of parts

- Test conditions affect performance

Mechanical features also affect RF performance!

3/2012

Understanding Specs to Better Simulate Solder-to-Board Performance

urn-in & Test Strategies Workshop

#### C<sub>res</sub> Test Method Differences

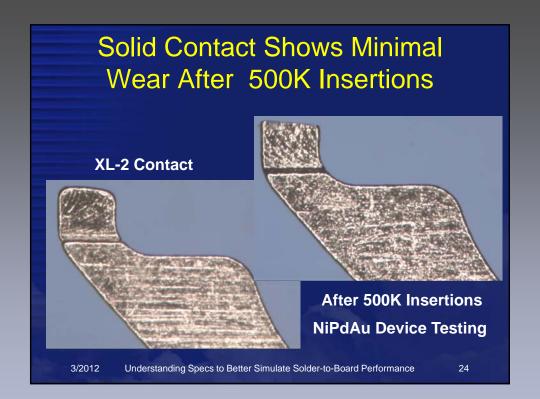

- Testing with correct device plating

- Gold on gold gives best results. Majority of package use other platings (i.e. Matte Tin and NiPdAu)

- Hardness of plating affects performance

- Oxide level affects performance

- Wear and contaminants affect life

- Wiping or self cleaning action affect MTBA

- Testing at correct forces and insertion speeds

- Higher the force the lower the C<sub>res</sub>

- Higher the force the shorter the contact life and MTBA

3/2012

Understanding Specs to Better Simulate Solder-to-Board Performance

25

#### Conclusion

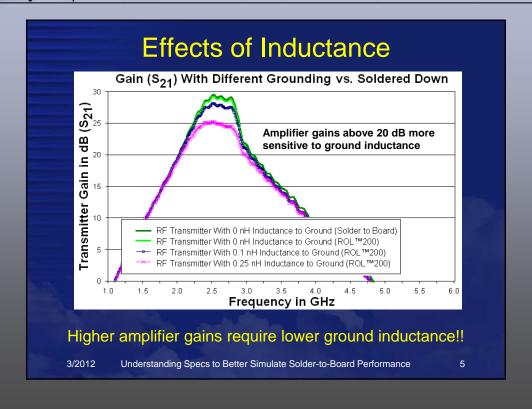

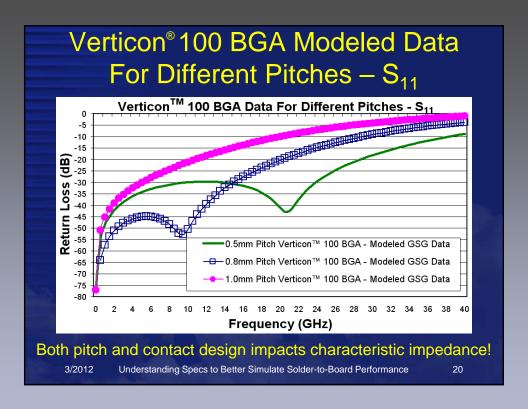

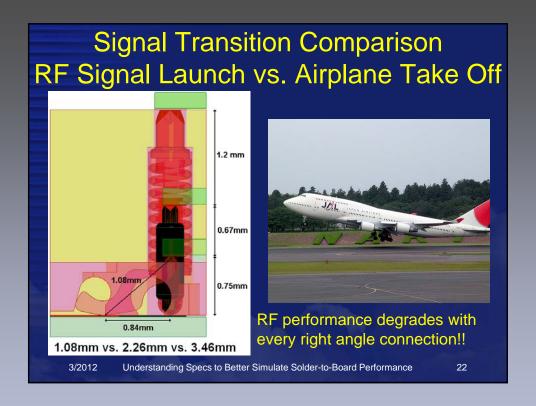

- Ground inductance is extremely important when measuring high frequency signals and devices with high gain

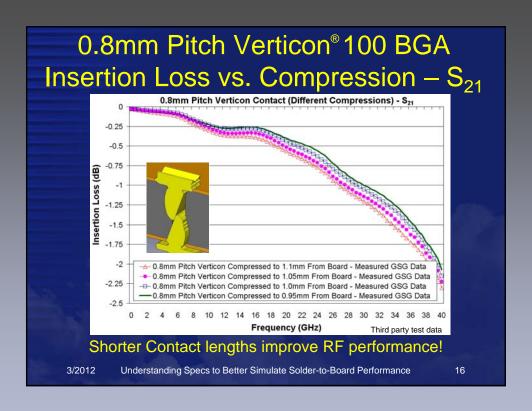

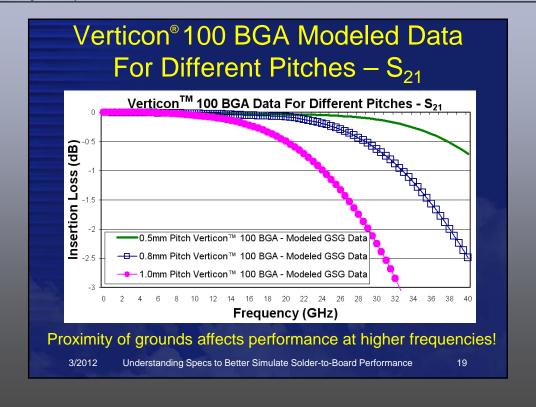

- Shorter paths result in better electrical performance (hypotenuse shorter than sum of legs)

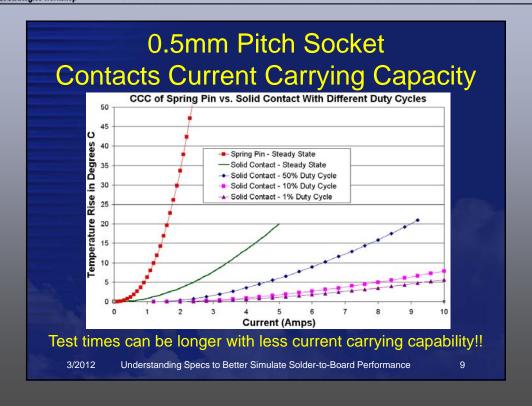

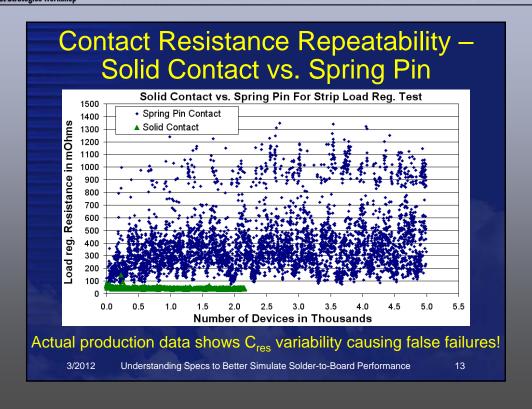

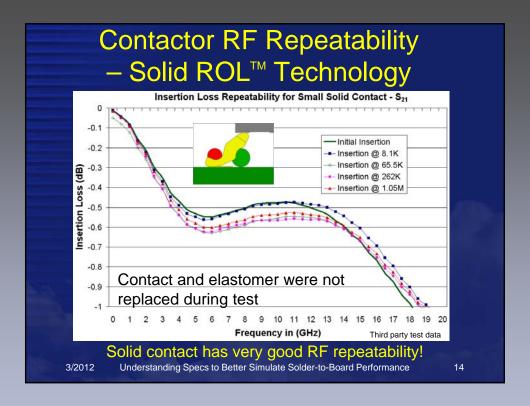

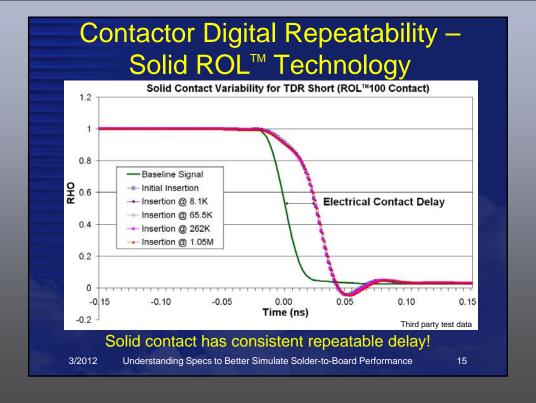

- Solid contacts have current carrying advantages over contacts with multiple parts

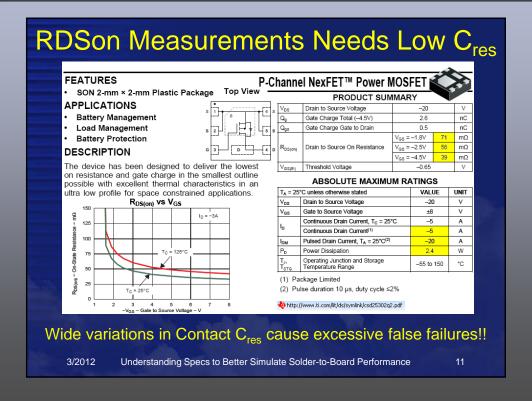

- Fewer contact interfaces result in lower Cres

- Repeatability improves both electrical and mechanical data accuracy resulting in higher yields

- Not all specifications are created equal

3/2012

Understanding Specs to Better Simulate Solder-to-Board Performance

**Analyze This**

# Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

Thomas P. Warwick, Al Seier R&D Circuits, Inc.

2012 BiTS Workshop March 4 - 7, 2012

#### **Purpose and Content**

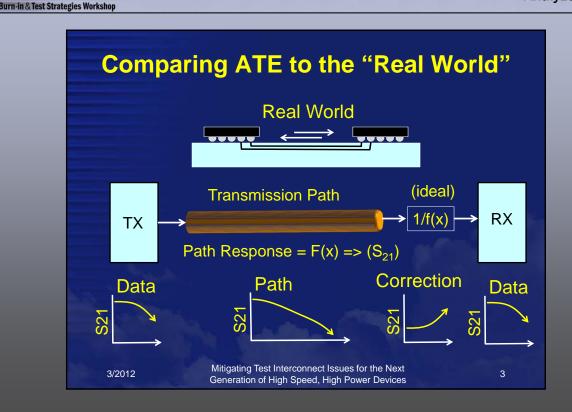

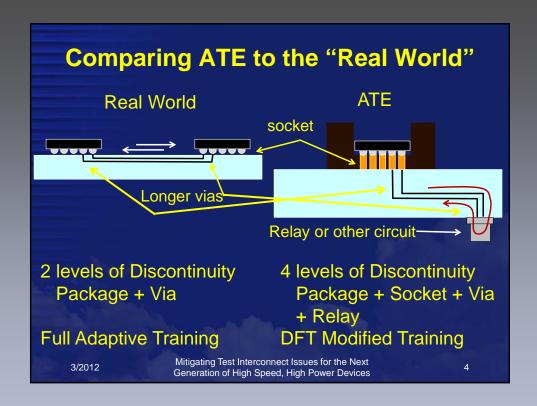

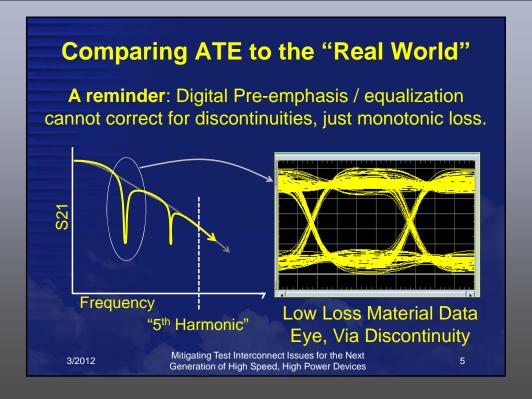

This Presentation discusses ATE-Specific Interface Issues for >25GB/s Devices

- Comparing ATE to the "Real World"

- Signal and Power Integrity Conflicts

- Compromises

- Concluding Comments

3/2012

Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

**Analyze This**

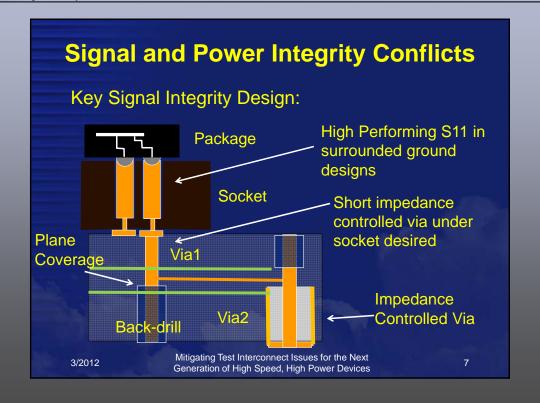

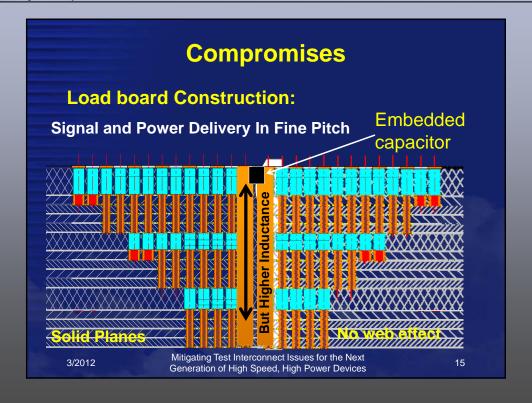

#### **Signal and Power Integrity Conflicts**

Key Signal Integrity Requirements:

- 1. Minimize Discontinuities

- a) Socket + Entry Via

- b) Via + Relay or circuitry

- c) Impedance Controlled or Coaxial Vias

- 2. Improve Isolation / Reduce Crosstalk

- a) Increased Spacing

- b) Better Ground Plane Coverage

- c) Increased Quantity Ground Vias

3/2012

Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

**Analyze This**

#### **Signal and Power Integrity Conflicts**

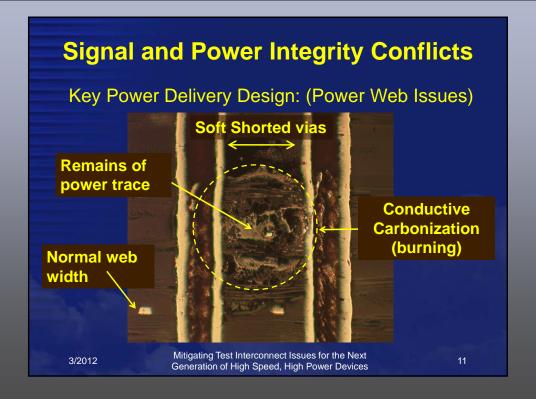

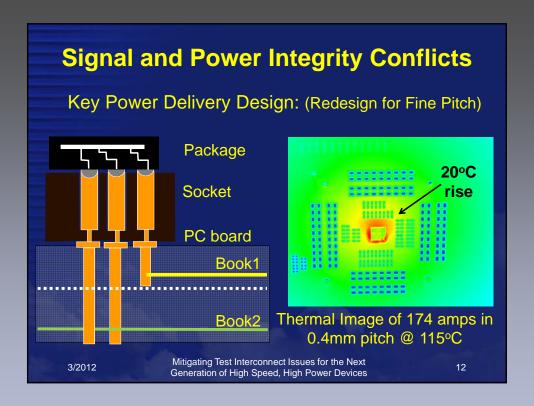

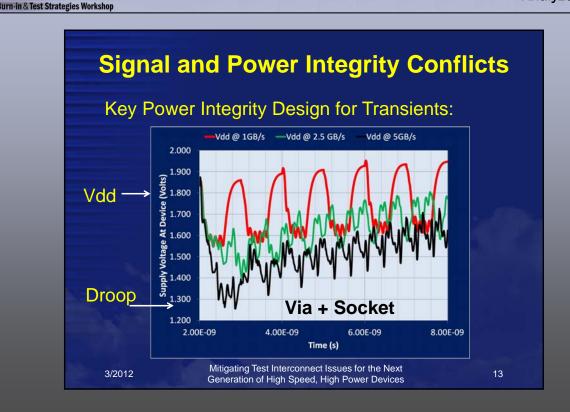

**Key Power Integrity Requirements:**

- 1. High Current Power Delivery

- a) Via Size, Plane Thickness, and Plane Redundancy

- b) "Web" or "Swiss Cheese" Effect

- c) Power Dissipation in the Socket pin

- 2. Transient Suppression

- a) Via and Socket Inductance

- b) Cres and ESR

3/2012

Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

9

#### **Signal and Power Integrity Conflicts** Key Power Integrity Design: Ultra-low Impedance for **Package** Transient Response Short via (for low impedance / inductance) Socket Significant Issues at fine pitch Via1 **Plane** Coverage Mitigating Test Interconnect Issues for the Next 3/2012 10 Generation of High Speed, High Power Devices

**Analyze This**

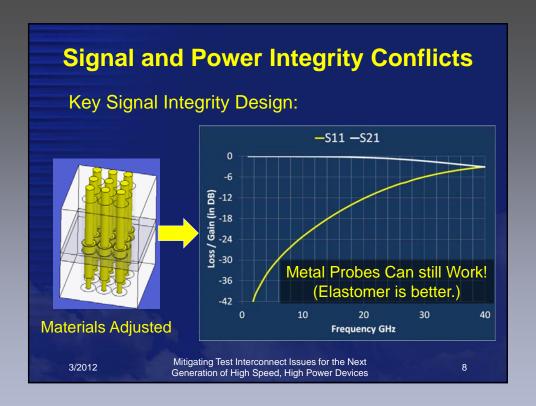

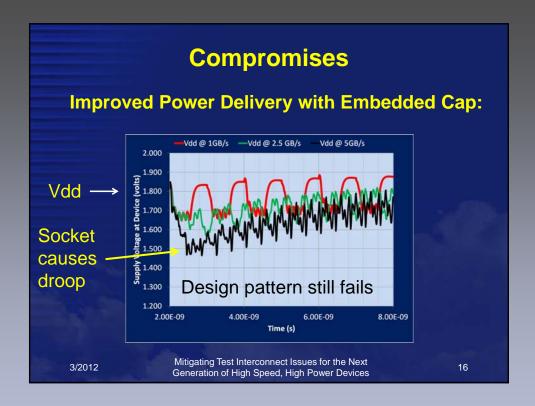

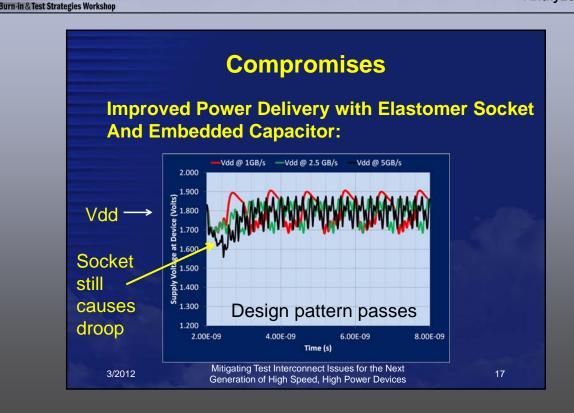

#### **Concluding Comments**

- > Test will likely always compromise relative to any "real world" environment.

- Attention to Signal integrity issues over the past few years make ultra high data rates possible in pinned sockets.

- Power remains a challenge both for the PC board, especially in high power and fine pitch.

- Elastomer contactors, while not "production worthy", remain the best choice for transient power management.

3/2012

Mitigating Test Interconnect Issues for the Next Generation of High Speed, High Power Devices

**Analyze This**

# Pulse Current Testing: Parameters and Their Significance

**Gert Hohenwarter GateWave Northern, Inc.**

2012 BiTS Workshop March 4 - 7, 2012

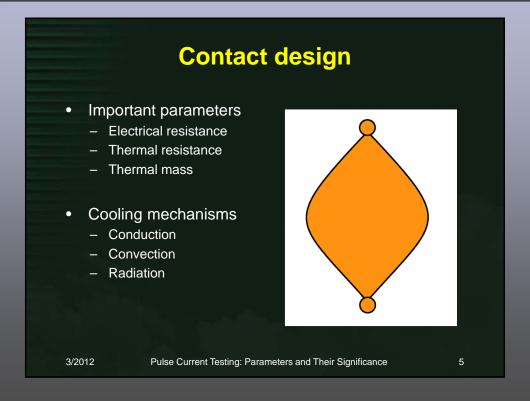

#### **Background**

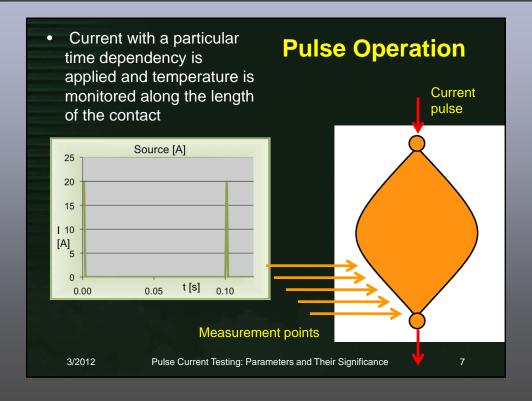

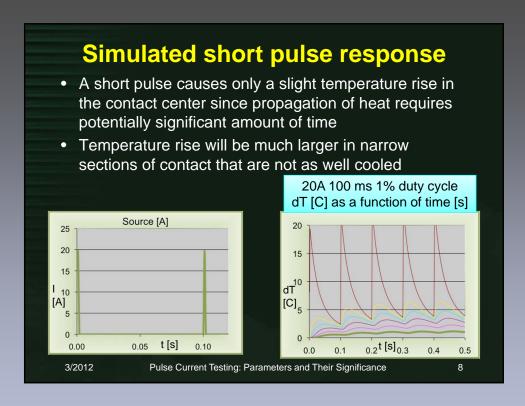

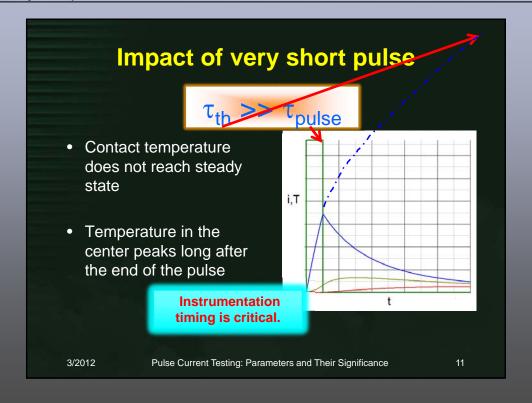

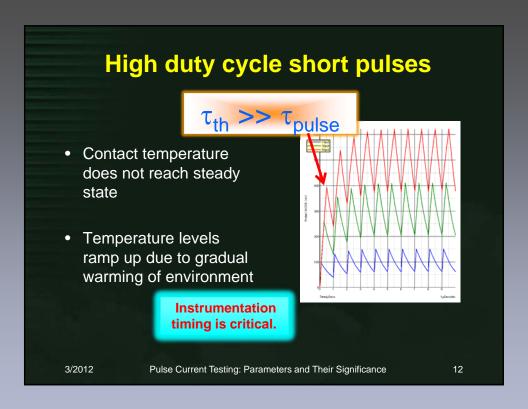

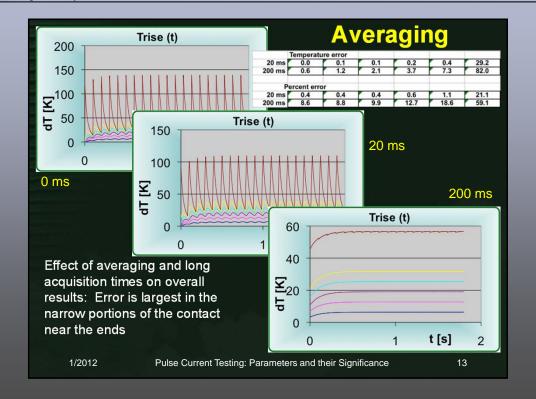

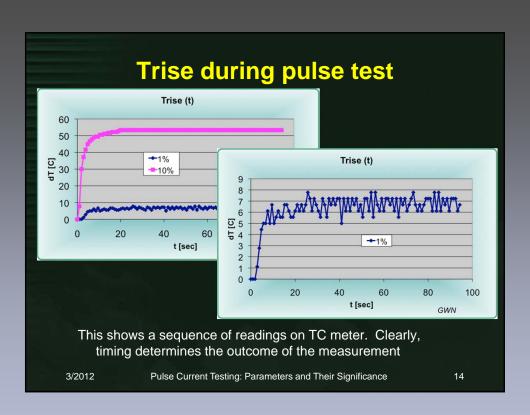

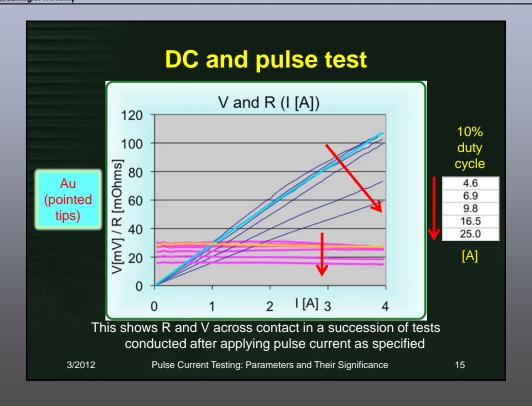

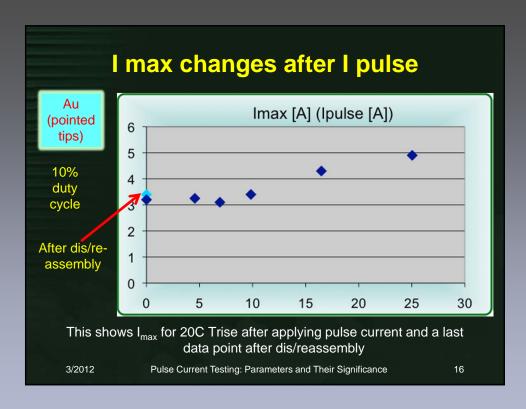

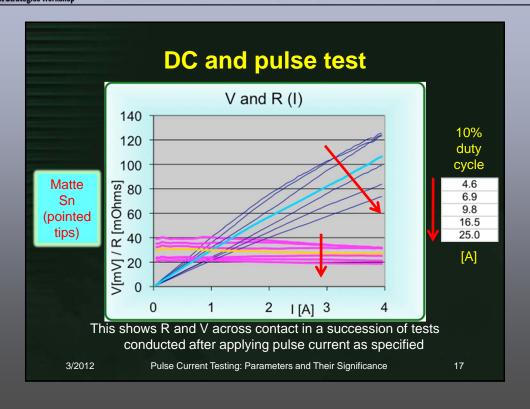

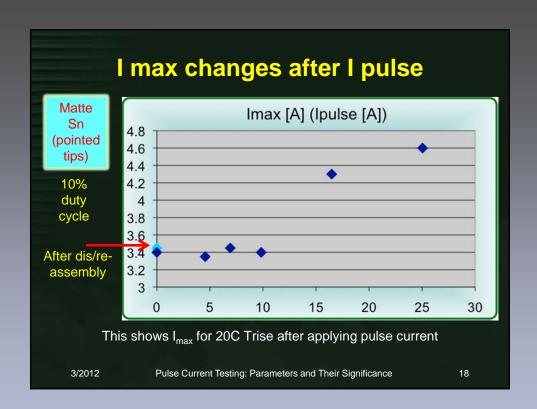

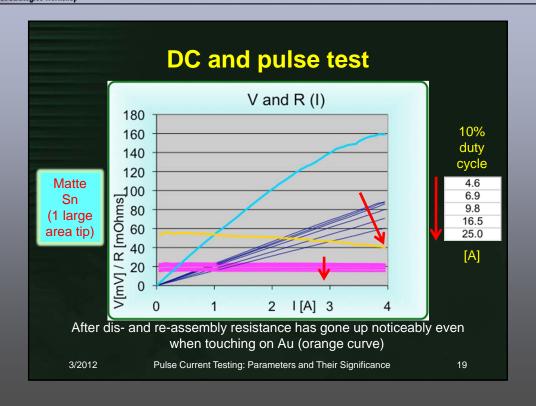

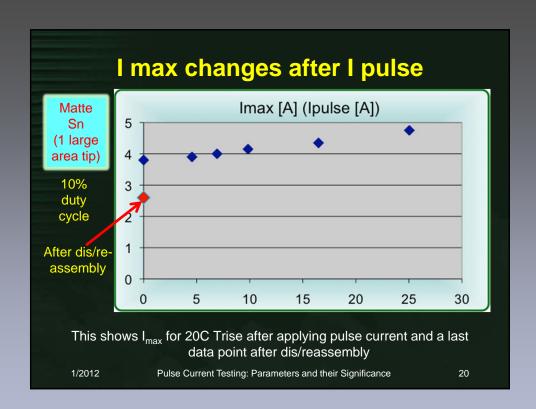

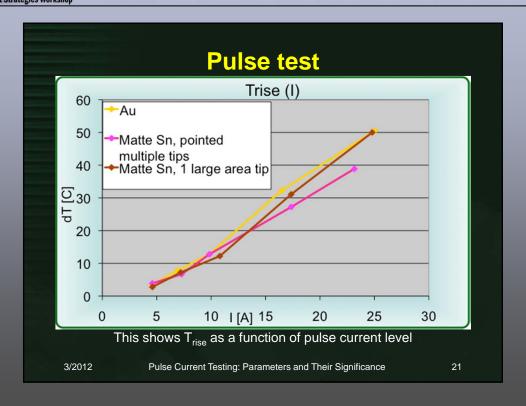

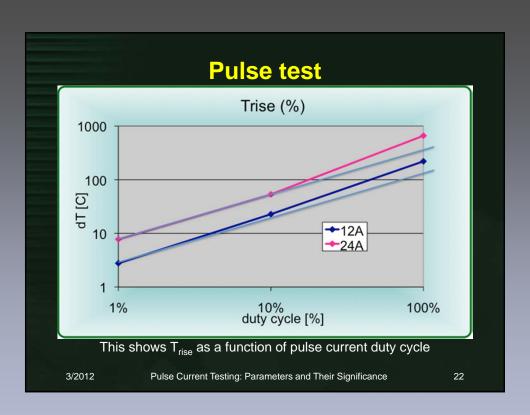

- Pulse testing of contacts can generate a wide variety of responses and results for critical parameters like

- · Current handling capability

- Contact temperature rise

- Interpretation of measurements depends on

- Test parameters

- Test environment

- Instrumentation

- Test methods

3/2012

Pulse Current Testing: Parameters and Their Significance

**Analyze This**

#### **Objective**

- · Identify potential pitfalls in pulse current testing

- Instrumentation

- Measurement techniques

- Test specimen

- Provide some guidelines for performance assessment

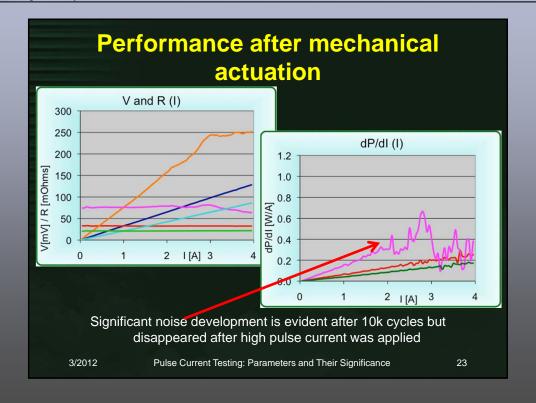

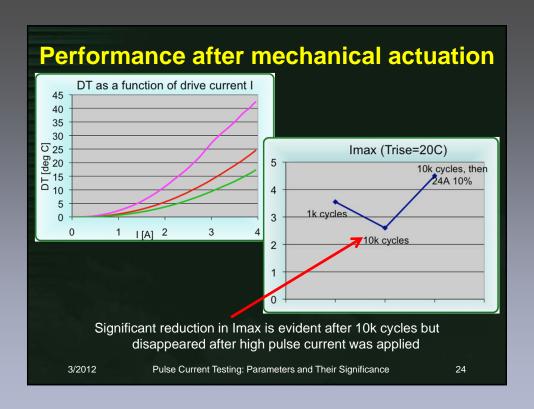

- Highlight impact of pulse current exposure of contacts on measured performance

3/2012

Pulse Current Testing: Parameters and Their Significance

વ

#### **Approach**

- Provide overview of basic parameters

- Utilize test results to demonstrate significance of full understanding required for pulse test models and procedures

- Engage computer simulations to demonstrate impact of test environment and parameters

- SPICE circuit simulator

- ANSYS HFSS field modeler

- 2.5D modeler for thermal problems

3/2012

Pulse Current Testing: Parameters and Their Significance

**Analyze This**

#### **Operating parameters**

- What a contact may be subjected to:

- DC (steady state) current

- AC (alternating / RF) current

- Short term loads

- Spikes from malfunctions

- Ambient temperature

- Consequences of exceeding design envelope

- Parameter changes

- Bulk

- Surface

- Premature (longer term) wear/failure

- Immediate failure

3/2012

Pulse Current Testing: Parameters and Their Significance

**Analyze This**

#### **Conclusion**

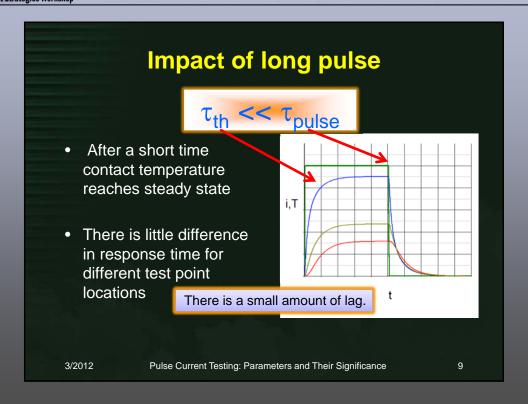

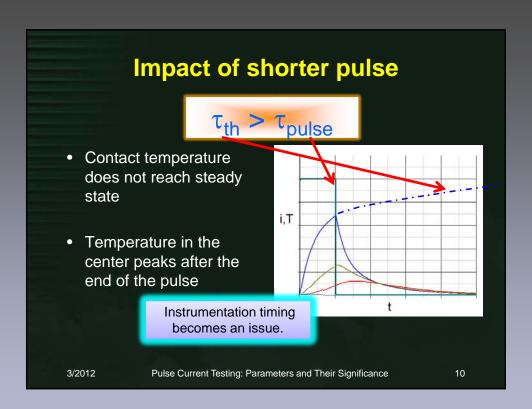

- Pulse test requires accurate knowledge of system time constants

- Source

- Load

- Thermal time constants of specimen

- Instrumentation

- Assessment of maximum current capability is not straightforward

- Measurement point for highest temperature rise may not be accessible

- A force based criterion may be more descriptive measure

3/2012

Pulse Current Testing: Parameters and Their Significance

**Analyze This**

# Key Parameters in Thermal Simulations

Joseph Ortega, Larry Furman

**Plastronics Sockets & Connectors**

2012 BiTS Workshop March 4 - 7, 2012

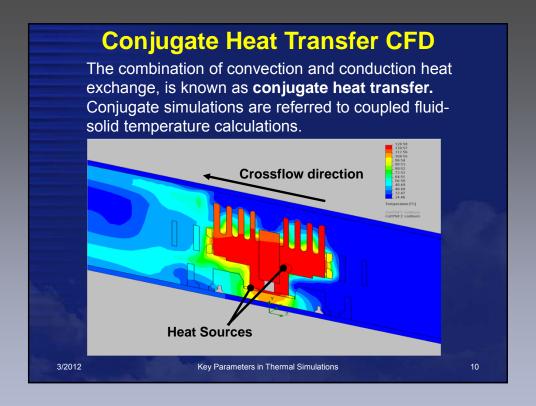

### **Outline**

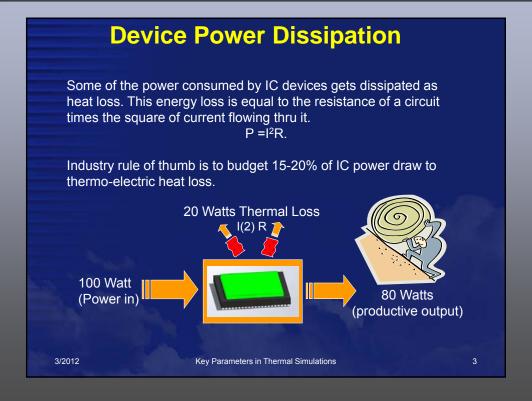

- Device Power Dissipation

- DUT Heat Variance is Increasing

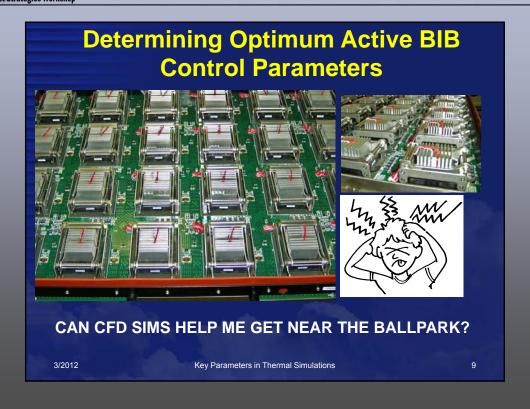

- BIB Active Control Parameters Challenge

- CFD Conjunctive Heat Transfer Simulation

- Modeling The System

- Establishing Target Guidelines

- · Tuning Parameters / Heat Sink Size

- Summary / Conclusion

3/2012

Key Parameters in Thermal Simulations

**Analyze This**

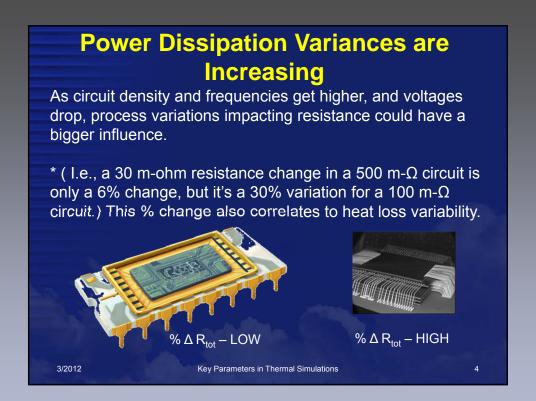

# Power Dissipation Variances are Increasing (cont'd)

- At Higher frequencies -> current travels increasingly near conductor surface ("skin effect"), contributing to increased to circuit resistance.

- Other internal die effects contributing to increased heat loss variability, (i.e., leakage currents, gate switching) and also tend to have a cumulative effect In heat loss variance<sup>(1)</sup>.

(1) ref. Freescale Semi BiTS 2008 Session 4, paper #2

3/2012

Key Parameters in Thermal Simulations

5

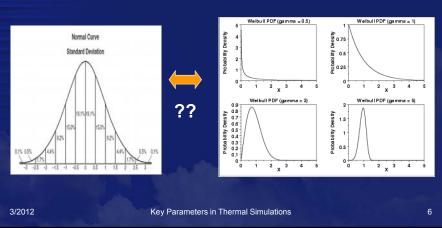

### +/- 50% Variance In Same Lot?

- Really ??

- Need Higher Precision Inputs / Verification

- What is the sample distribution, std. deviation, etc. ?

- Can we get lot sample measurement data and stats?

**Analyze This**

## What About Sample Size & Confidence Values?

\* WHAT ABOUT SAMPLE SIZE?

What if we sampled 4 parts and measured 30W, 40W, 50W, and 65W of heat dissipation, what is the 95% confidence interval for the mean of the population?

Ans:  $46.25W + /- 23.75W = [22.5W - 70W]^*$

Conclusion: With a limited data set which also has a large standard deviation, we can't really predict much about a population, so Burn In Test Engineer is forced to evaluate "worse case" extremes.

\* Normal Distribution, theorem 9.3.2 Introduction Eng. Stat., Wiley, 2<sup>nd</sup> Ed. Ref. Appendix

3/2012

Key Parameters in Thermal Simulations

7

# Power Density Trend and Higher Dissipation Variances = Burn-in Test Engineer Migraine DUT Power Density Roadmap - PROCESS MAX - PROCESS AVG. - PROCESS MIN 100 107 107 1080' 1990' 2000' 2010' 2020' Key Parameters in Thermal Simulations 8

**Analyze This**

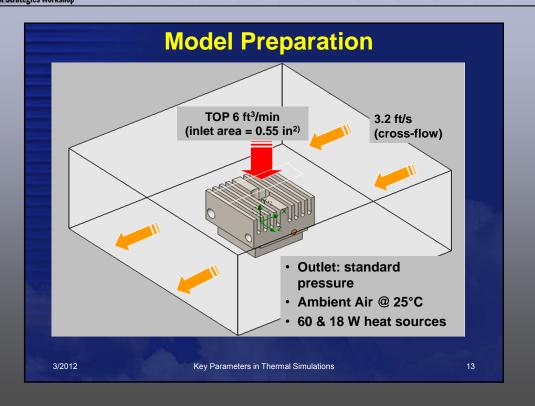

### **Model The System**

Fortunately, today's software technology assists greatly in modeling most of the thermal challenges of burn-in. A good checklist for modeling is as follows:

- Thermal resistance of the die and case (or package)

- Wattage range of the device

- Die size

- Size of the case or heat spreader

- Ambient oven temperature

- Inlet air temperature

- Box or envelop size of the system

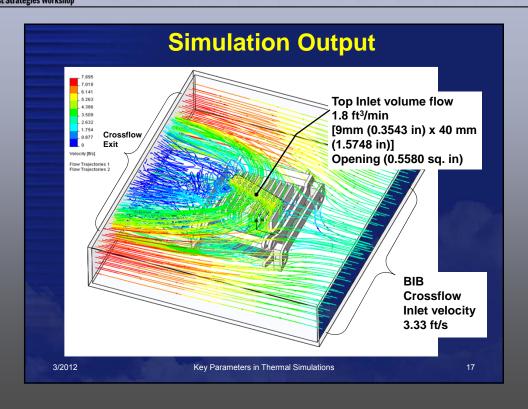

- Air velocity and direction or cross-flow, and or inlet valve size if directly over the heat sink

3/2012

Key Parameters in Thermal Simulations

11

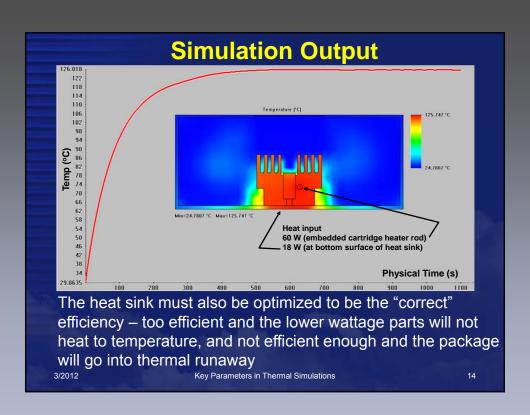

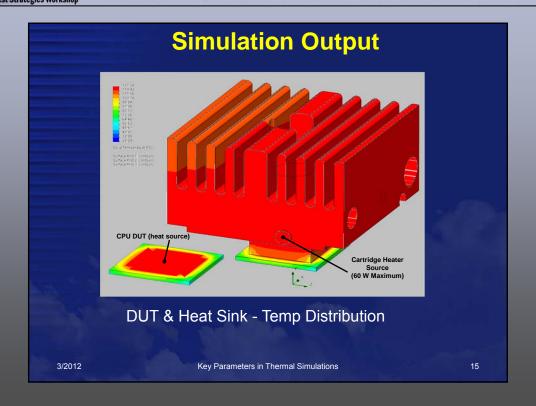

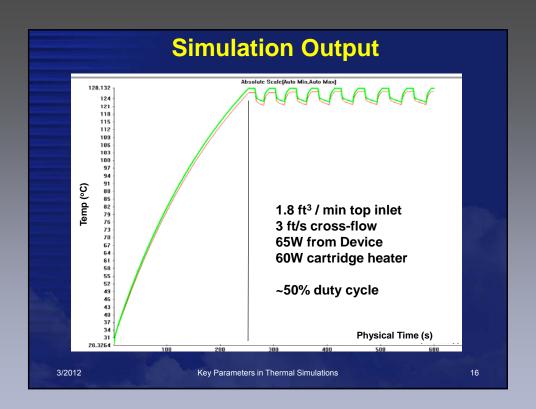

### **Model The System (cont'd)**

With this information, a proper heat sink can be constructed, as well as determining if the heater cartridges imbedded in the heat sink will properly bring the device to temperature quickly enough within the recommend working duty cycle of the cartridge. If there is a controller on the fan speed or valve, a calculation can also be performed to ensure it's not overworked as well.

An added benefit to the model also includes a finite element analysis (FEA) on the heat sink force to ensure there is not an excessive load on the die

3/2012

Key Parameters in Thermal Simulations

**Analyze This**

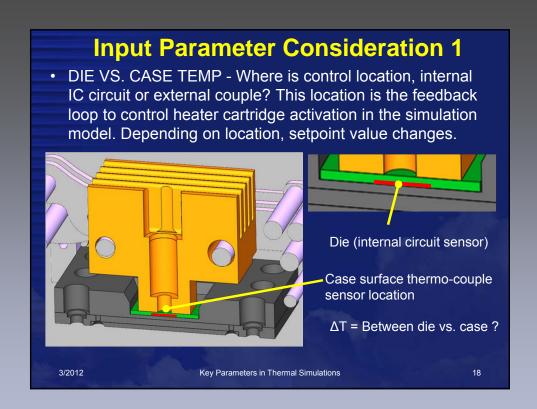

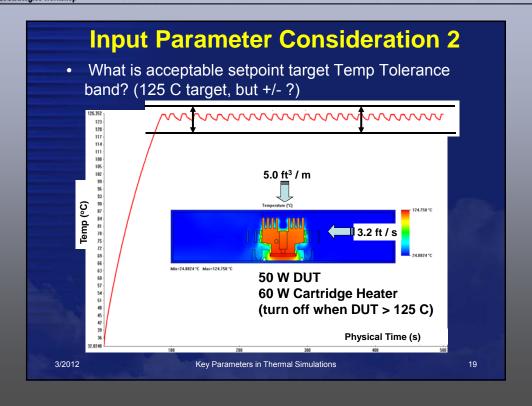

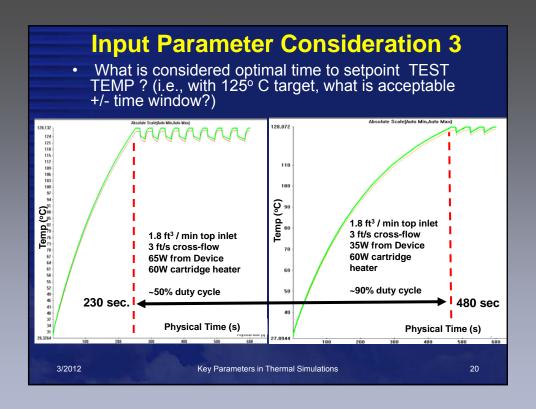

### **Input Parameter Consideration 4**

- Cartridge Heater Output vs. Rating Consideration

- Input voltage drives cartridge heat power output (Voltage supply can be on lower end of rated +/- 15% nominal value).

- Since output Power relative to input voltage is P=V<sup>2</sup>/R a 15% lower voltage results in >25% less Power output from the cartridge heater.

Key Parameters in Thermal Simulations

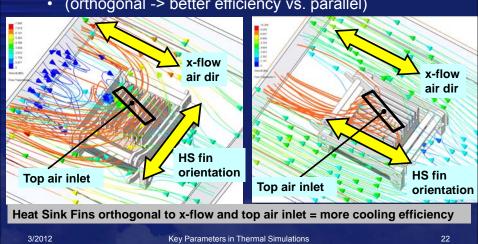

### **Input Parameter Consideration 5**

- Top air Inlet Orientation vs. Heat Sink Fins length-wise arrangement vs. cross-flow direction

- Orientation impacts Heat Sink efficiency

- (orthogonal -> better efficiency vs. parallel)

**Analyze This**

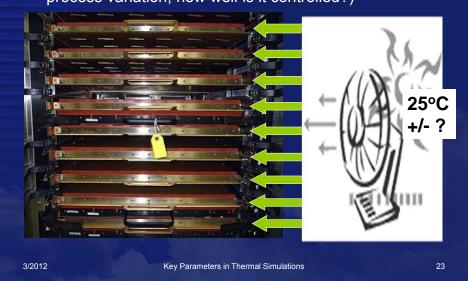

### **Input Parameter Consideration 6**

• Test OVEN AIR TEMP "AMBIENT" (what's the process variation, how well is it controlled?)

### **Summary / Conclusions**

- Industry trending towards higher variances with DUT heat dissipation

- Increases in Circuit Density and resulting power draw in combination with larger variances in heat dissipation result in greater (max., min ) test conditions.

- A "one size fits all" solution with nominal heat sink & active Burn-in oven control parameters may not always be adequate, tuning of control parameters and/or heat sink could be necessary.

- Pro-active CFD simulations of set up parameters and heat sink adjustments can help Test Engineers better prepare for various "game time" situations (i.e., plan "a", "b", etc.)

3/2012

Key Parameters in Thermal Simulations

**Analyze This**

### **Summary / Conclusions (cont'd)**

With growing thermal concerns, using modeling tools can assist in solving issues. Diligence is needed in the selection of capital equipment on the front end in to make sure it can handle the range of devices that need to be tested, but once selected, additional hardware that includes boards, heat sink and sockets can be accurately modeled to achieve the goal – burn-in at the exact temperature needed.

Better inputs -> More accurate CFD simulations -> Less time spent "tuning" BIB parameters = <u>Faster product</u> time to market!

3/2012

Key Parameters in Thermal Simulations

25

### **Appendix**

\* Normal Distribution, theorem 9.3.2 Introduction Eng. Stat., Wiley, 2nd Ed.

If  $\overline{x}$  and  $s^2$  are the mean and variance of a sample of size n from a normal distribution N( $\mu$ ,  $\sigma^2$ ), where  $\mu$  and  $\sigma^2$  are unknown, then:

$$\overline{x} \pm [(t_{n-1:\alpha/2}) * (s) \div (sq. root (n))]$$

Is a  $100(1 - \alpha)\%$  confidence interval for  $\mu$ .

Ref. t = Student t distribution (approaches normal distribution  $\sim$ z when (n -1) is large

For sample parts measuring 30, 40, 50, 65 Watts. Then:

$\overline{x}$  = 46.25, n = 4, and s = 14.9; therefore (s) ÷ (sq. root (n))] = 14.9 / 2 = 7.45

For confidence interval:  $1 - \alpha = 0.95$ , then  $\alpha = .05$  and  $\alpha \div 2 = 0.025$  and n - 1 = 3, we then find from t distribution reference table for t  $_{3 \cdot 0.025} = 3.182$

So confidence interval =  $46.25 \pm (3.182) * (7.45) = 46.25 \pm 23.7 = [22.5 - 70]$

3/2012

Key Parameters in Thermal Simulations