## **ARCHIVE 2010**

by

Brandon Prior

Senior Consultant

Prismark Partners

#### **ABSTRACT**

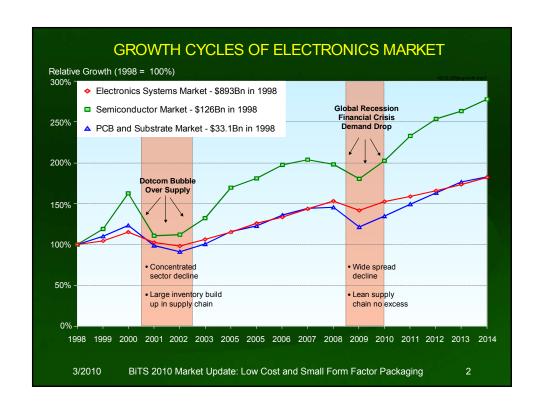

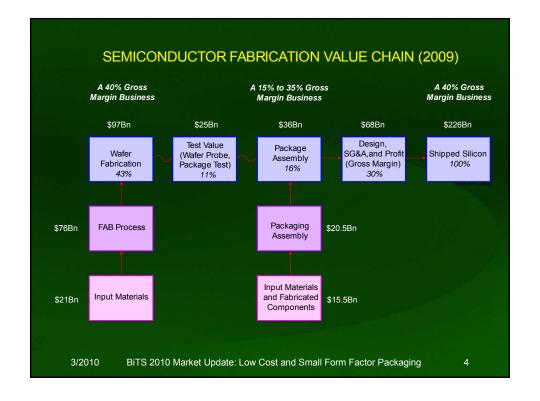

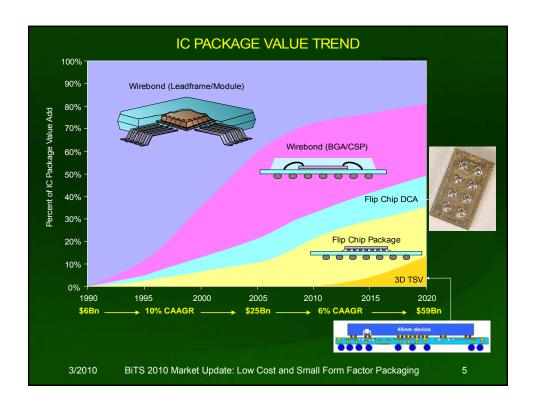

While size reduction and performance improvement are often the drivers of new package and interconnect solutions, cost reduction strategies have become an even more critical factor to further enable continued profitability through challenging times. Although those times are hopefully (albeit temporarily) behind us, many companies large and small have adopted strategies to reduce package, interconnect and test cost. This presentation paper will look at leading package trends driven by cost reduction.

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2010 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

### WHY LOW COST PACKAGES? Cost Reduction is always a priority, but industry downturns increase the stress put into cost reduction strategies Various approaches can be applied - Raw Material Cost (e.g. Copper vs. Gold wire) - Package Size Reduction (QFN/DFN, tighter pitch FBGA, WL-CSP) Outsourcing and Regional Shifts - Efficiency Improvements (throughput, strip test, etc)

3/2010 BiTS 2010 Market Update: Low Cost and Small Form Factor Packaging

| TILO               | LINI VVL           | OSF AFFLICATI                                                  | ON EXAMPLES                                                                               |  |

|--------------------|--------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|

| Mobile Phone       | Total Wafer<br>CSP | WLCSP Applications                                             | Comments                                                                                  |  |

| Palm Pre           | 10                 | ESD/EMI, EEPROM,<br>Bluetooth, WLAN                            | 6 – 25 I/O on board<br>WLAN, BT, EEPROM on module                                         |  |

| Panasonic P901i TV | 7                  | ESD/EMI,<br>analog/power, other?                               | Up to 5mm die with 119 I/O at 0.4mm pitch                                                 |  |

| LG KM900 Arena     | 3                  | ESD/EMI, GPS                                                   | 4.7mm, 64 I/O at 0.4mm pitch                                                              |  |

| Apple iPhone 3GS   | 6                  | ESD/EMI,<br>Bluetooth, WLAN, GPS                               | Up to 4.7mm die with 69 I/O at 0.4mm pitch on board, 6.4 x 5.7mm die at 320 I/O on module |  |

| Panasonic P905i    | 6                  | Transceiver,<br>Bluetooth, power,<br>TV tuner (two chips), GPS | 5 die use copper post tech,<br>up to 185 I/O at 0.4mm pitch                               |  |

| Nokia 6220 Classic | 7                  | ESD/EMI, power, other?                                         | Up to 5mm die                                                                             |  |

| Nokia N95          | 8                  | EMI/ESD, analog,<br>Bluetooth, FM radio                        | Up to 4mm die with<br>47 I/O at 0.5mm pitch                                               |  |

| Nokia N97          | 8                  | EMI/ESD, GPS, WLAN,<br>analog                                  | Up to 4.4mm on module (104 I/O) Up to 3.5mm die on board (61 I/O)                         |  |

3.141bp

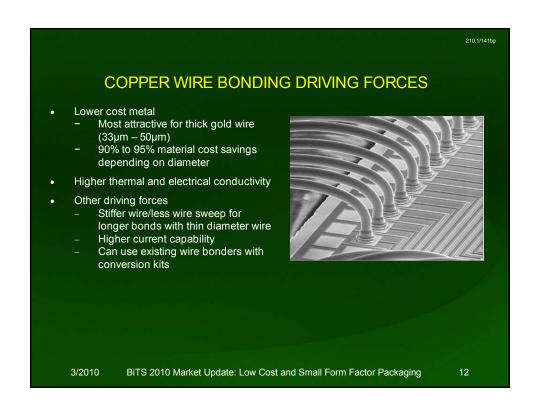

#### COPPER WIRE ENABLES LOWER COST

Leadframe and CSP Examples

No argument that copper wire is lower cost than gold wire. Two example products and differences between copper and gold wire are shown below:

| SO-14 (33µm wire)          |         |         |  |  |

|----------------------------|---------|---------|--|--|

|                            | Cu Wire | Au Wire |  |  |

| Wire Cost                  | 0.1¢    | 1¢      |  |  |

| Wire Bonding Cost          | 0.6¢    | 0.5¢    |  |  |

| Other Package Costs        | 1.1¢    | 1.1¢    |  |  |

| Total Cost (not price)     | 1.8¢    | 2.6¢    |  |  |

| Total Savings: 0.8¢ or 30% |         |         |  |  |

| 350 FBGA (20µm wire)     |         |         |  |  |

|--------------------------|---------|---------|--|--|

|                          | Cu Wire | Au Wire |  |  |

| Wire Cost                | 3¢      | 13¢     |  |  |

| Wire Bonding Cost        | 17¢     | 15¢     |  |  |

| Other Package Costs      | 37¢     | 37¢     |  |  |

| Total Cost (not price)   | 57¢     | 65¢     |  |  |

| Total Savings: 8¢ or 12% |         |         |  |  |

- Savings with copper wire as a percent of package are more pronounced with thicker wire, not more wires.

- Concerns with yield are less noticed with low I/O, low-value devices.

3/2010 BiTS 2010 Market Update: Low Cost and Small Form Factor Packaging 13

210.1/141bp

#### **COPPER WIRE BOND STATUS**

- In 2009, copper represented 4% to 5% of all bonding wire by length, up from < 1% in 2006</li>

- This is expected to reach 15% or more by 2014

- Driving applications are power discretes (i.e., power transistors, rectifiers, thyristors), "power/logic mixed signal devices", and now logic and memory

- Justification

- Lower cost than thick gold

- Faster bonding than aluminum

- Possibility to do corners easily (unlike aluminum)

- Possibility to place function under pads (unlike aluminum)

- However, copper wire may be slow to penetrate mainstream IC market as the following items are addressed:

- Yield parity with gold

- Establish comprehensive reliability database

- Pad structure compatibility

- Qualification risk and expense mitigated

3/2010 BiTS 2010 Market Update: Low Cost and Small Form Factor Packaging

'-

### **CONCLUSIONS**

- Semiconductor companies always searching for cost reduction strategies

- · Various approaches can and have been applied

- Copper vs. Gold wire, Lower cost EMC, laminate, etc

- Smaller packages such as QFN/DFN, tight pitch FBGA, and WL-CSP as bare die

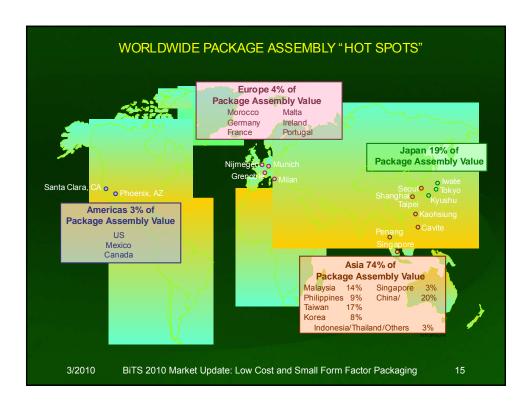

- Outsourcing and Regional Shifts Asia already dominates, but continued growth in China, India, Philippines and Vietnam

- Efficiency Improvements (throughput, strip test, etc) are never sufficient

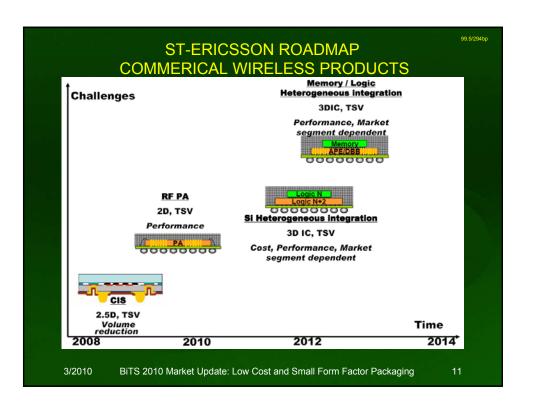

- · 3D/TSV approaches are still searching for cost effective test

- Pitches approach 50um

- Test before die to die or die to wafer assembly often required

3/2010 BiTS 2010 Market Update: Low Cost and Small Form Factor Packaging