# **ARCHIVE 2010**

RISING TO THE 3D TSV TEST CHALLENGE: WILL YOU BE READY?

bv

Françoise von Trapp

Editorial Director

3D InCites

### **ABSTRACT**

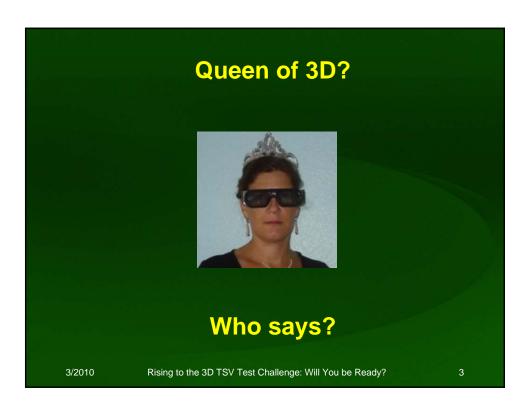

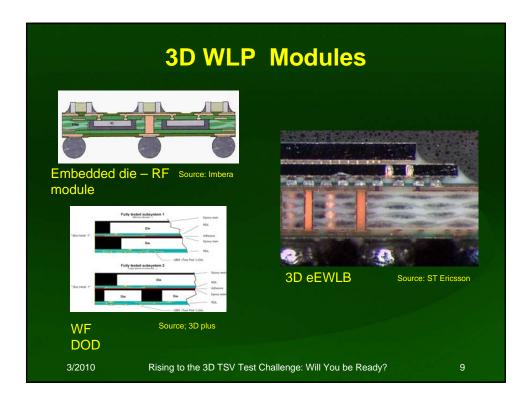

**3** Dintegration is not a novel concept. Veterans in the industry will tell you it's been around for 20 years. In fact many 3D integration configurations, such as package-on-package (PoP) configurations, stacked die interconnected with wirebond or flip chip, and other 3D wafer-level packaging (WLP) technologies that utilize the existing WLP supply chain such as fan-out WLP, Freescale's redistributed chip package (RCP), and Infineon's eWLB; are already being manufactured in volume. While these configurations have most assuredly posed challenges to the test community, the technology proving to be most elusive is naturally the newest kid on the block: 3D ICs stacked using through silicon via (TSV) interconnects.

However, while test solutions are high on the list of limitations yet to be overcome, experts agree that such deficiencies won't slow down market adoption of 3D TSVs, and that when the time comes, solutions will be available. Indeed, one giant step towards assuring this is communication between the manufacturing and test communities, and in turn, an increased awareness in the test community of what the challenges are, and what issues they'll be asked to solve.

As such, this talk will offer a brief overview of the 3D roadmap, the technology benefits of 3D TSV adoption, the test obstacles TSV stacking presents, R&D efforts addressing these solutions thus far, alternatives being suggested, and other information to help you decide if your company should take up the gauntlet.

### COPYRIGHT NOTICE

The papers in this publication comprise the proceedings of the 2010 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Francoise von Trapp

Co-founder and Editorial Director,

3D InCites

2010 BiTS Workshop March 7 - 10, 2010

### **Agenda**

- How I became Queen of 3D

- Defining 3D

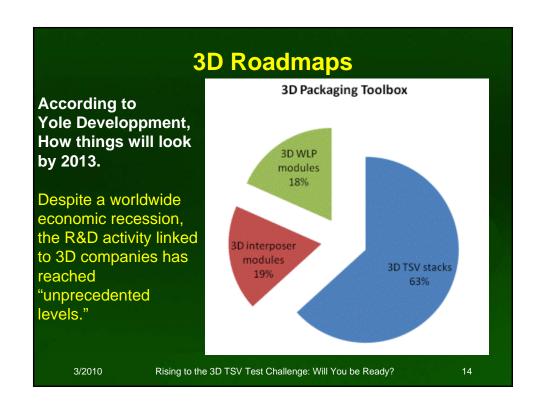

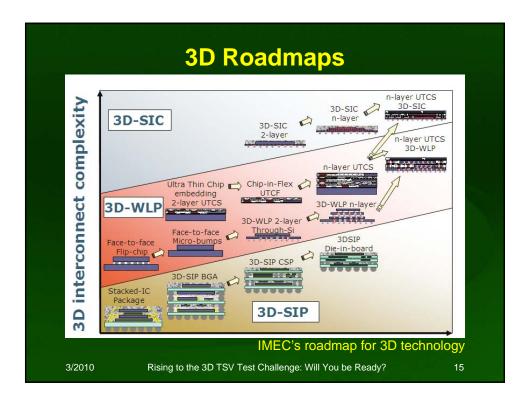

- 3D Roadmaps

- 3D TSV: the new kid on the block

- The role of test in 3D TSVs

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?

# Queen of 3D Where I got the name I'm NOT an engineer I'm a JOURNALIST focused on 3D integration and packaging Information here gathered at various 3D events, from the true 3D experts.

# 3D 101: A review Basic Truths: 3D has been around for 30 years (Lee Smith at Amkor) 3D integration refers to architecture. TSV alone is NOT 3D – it ENABLES 3D. 3/2010 Rising to the 3D TSV Test Challenge: Will You be Ready?

# 3D 101: A review Why 3D? Performance Form factor Cost benefits Board real estate Wafer real estate 3/200 Rising to the 3D TSV Test Challenge: Will You be Ready?

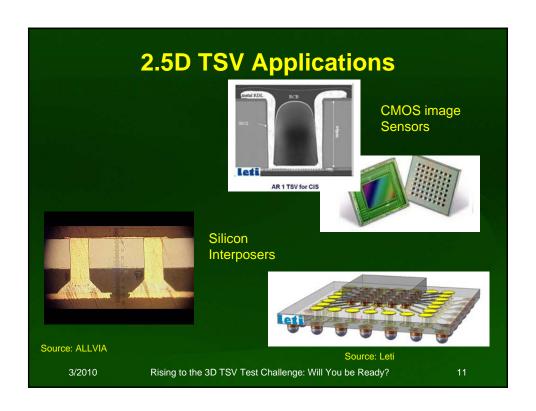

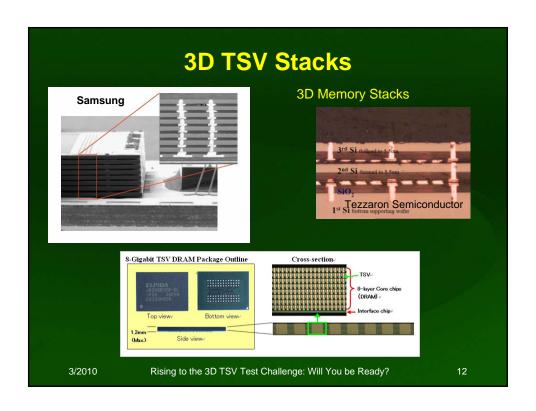

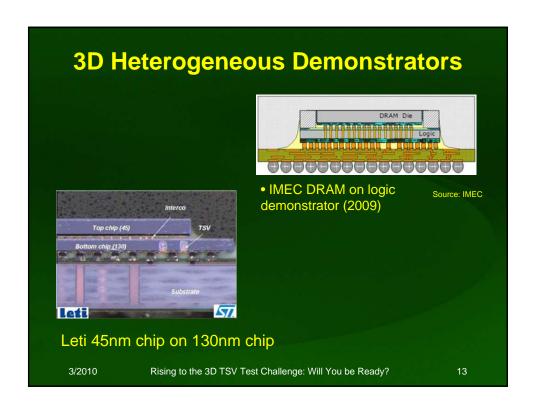

# 3D 101: A review 3D Packaging vs. 3D Silicon 3D Packaging already in volume production 3D silicon – TSV and non-TSV approaches 3D comes in many varieties 3D PoP 3D SiP 3D WLP 3D ICs 3D SICs 3D SICs

### **Limitations to TSV Adoption**

The experts agree, while there are variations, these three issues still stand out:

- Design Tools are still lacking

Progress is well underway here

- Thermal solutions must be developed

- Not a show stopper and some see thermal advantages to TSVs

- Test issues must be addressed and resolved

3/2010 Rising to the 3D TSV Test Challenge: Will You be Ready?

### **Test: The TSV Black Hole**

- If there's work being done in the test community, not much information is being circulated to the manufacturing community

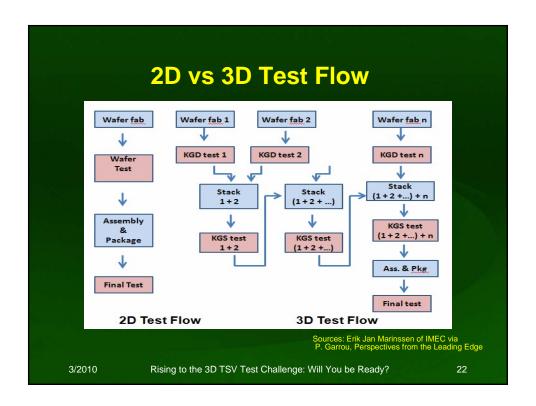

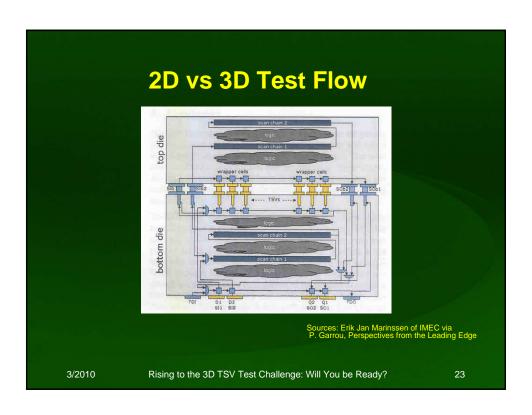

- Current test methodologies won't work with TSV stacks

- Contact testing (probe cards) damage TSV wafers

- Probing doesn't scale

- Known Good Die or at least Pretty Good Die are needed for suitable yields.

- Do we test each strata or the whole stack?

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?

17

### **Test: The TSV Black Hole**

- New processes mean new defects to be tested for.

- Thin wafers and pads on both sides will need testing

- Current probe technologies are not effective on tight-pitch TSVs (5-10 micron)

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?

### **TSV Test Solutions**

- New Test Flow

- Test both before and after bond

- Built in self test (BIST)

- Repair and Redundancy

- Clean partitioning

- Scan to edge

- Design for Test solutions

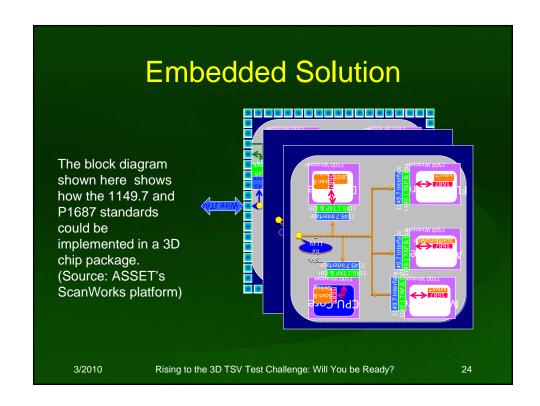

- Use iJTAG to permit testing TO the TSV interface before assembly

3/2010 Rising to the 3D TSV Test Challenge: Will You be Ready?

### Tezzaron's Bi-Star

- Improves yield of highly parallel structures such as memory

- Basis: integration of intelligent self test, self repair

- Performs greater level of testing than normally available during normal chip or wafer level testing

- Bi-STAR™tests and compares >300,000 nodes or bits/clock cycle; more than 1,000 times faster than can be achieved by any external memory tester

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?

### **Summary**

- •3D Integration comes in many flavors. One is right for you.

- •TEST is an area of critical concern that must be addressed.

- •The community has been made aware, and the rumblings of activity can be heard

- 3D spells opportunity for those tenacious enough to pick up the gauntlet.

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?

25

### References

P. Garrou, Ph.D; 3D IC Integration: Status and Overview.; proc. 3-D Architectures for Semiconductor Integration and Packaging Burlingame CA; DEC 2009; 3-D IC Test, Perspectives from the Leading Edge, December 8, 2009; http://www.semiconductor.net/blog/Perspectives\_From\_the\_Leading\_Edge/29137-3\_D\_IC\_Test.php

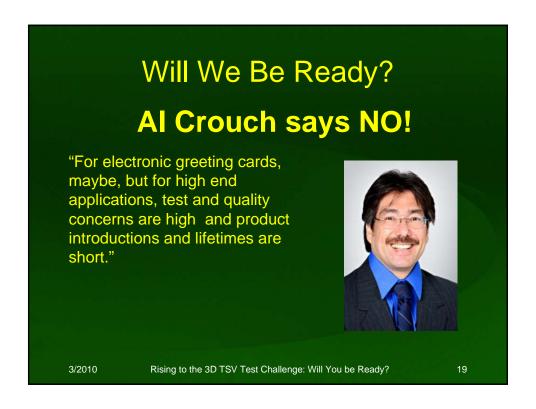

A. Crouch; Synergy of two emerging standards will drive 3D chip and circuit board test into high gear; White Paper, ASSET InterTech, Inc.

P. Franzon, Ph.D.; Creating 3D Specific Systems: A 10 Step Program; proc. 3-D Architectures for Semiconductor Integration and Packaging Burlingame CA; DEC 2009

Bob Patti, CTO; 3D Finds the Road, Dec 2009; proc. 3-D Architectures for Semiconductor Integration and Packaging Burlingame CA; DEC 2009

3/2010

Rising to the 3D TSV Test Challenge: Will You be Ready?