# **ARCHIVE 2009**

### **ADVENTURES IN TEST & BURN-IN OPERATIONS**

#### **Parallel Logic Test Interface Solutions**

YH Jeon, Sang-II Kwon—TSE Gary Westendorf, Chris Mack—Pragmatics

#### **CID: A New Breakthrough Solution For Contactor Hardware Tracking**

Jonathan Mondero—Texas Instruments Philippines Kevin Tiernan, Mike Guenther—Texas Instruments Houston Eugene Batilo—Everett Charles Technologies – STG Singapore

#### Mechanical Reliability Test as Part of Final Test of a Packaged Chip

Che-Yu Li, Tia Korhonen—Che-Yu Li & Co. Tim Wooden—Protos Electronics SM Low—ADE Technologies

# Substrate Bias: Application in Final Test and Burn-in of High-Power CPU's

Max Paransky—Texas Instruments

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2007 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

YH Jeon, TSE Sang-II Kwon, TSE Chris Mack, Pragmatics Gary Westendorf, Pragmatics

2009 BiTS Workshop March 8 - 11, 2009

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

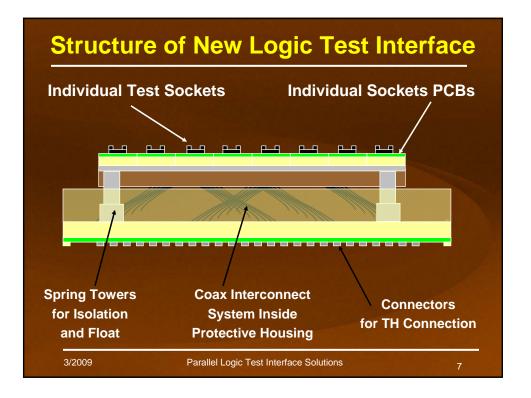

#### Why We Chose This Subject... Lessons learned from years of producing high parallel memory & MCP test interfaces are being applied to production Logic / SOC testing. Economics often require Logic / SOC production test without new capital spending on ATE. The real estate inside parallel test interfaces can be utilized to expand ATE resources. There are more Logic / SOC devices emerging that require high volume production. Parallel Logic Test Interface Solutions 3/2009

## **Enabling Technologies**

- Increasing density ATE PEs & interconnects.

- DFT/BIST/SCAN reduces ATE I/O requirements.

- Logic load boards are transitioning to parallel test interfaces with real estate for fan-out circuitry & additional DUT power supplies.

- Advancements in lithography & packaging provides denser, smaller Logic / SOC devices that can be handled by memory test handlers.

3/2009

Parallel Logic Test Interface Solutions

4

3/2009

# **Session 3**

**Adventures in Test & Burn-in Operations**

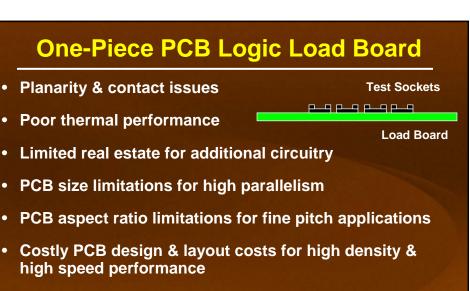

PCB yield & cost issues for high density & performance

Parallel Logic Test Interface Solutions

Very limited repair & maintenance options

Adventures in Test & Burn-in Operations

**Adventures in Test & Burn-in Operations**

# <section-header><section-header><text><image><text><page-footer>

# CID: A New Breakthrough Solution for Contactor Hardware Tracking

Jonathan D. Mondero – TI (Philippines) Kevin Tiernan – TI (Houston) Mike Guenther – TI (Houston) Eugene Batilo – ECT (Singapore)

2009 BiTS Workshop March 8 - 11, 2009

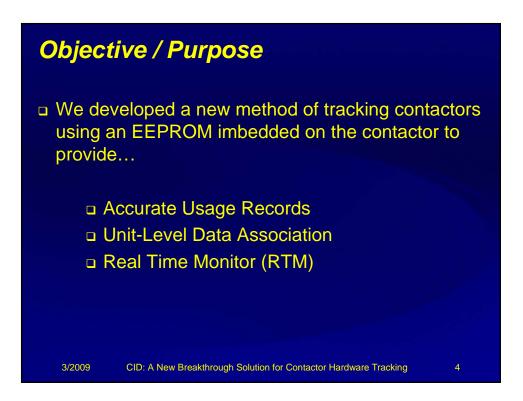

## **Presentation Topics**

- **Background**

- Objective / Purpose

- Case for Action The Current process

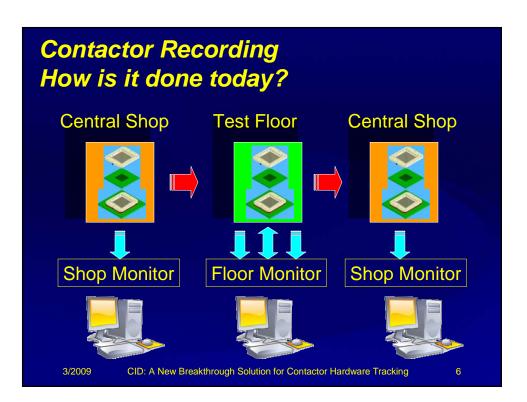

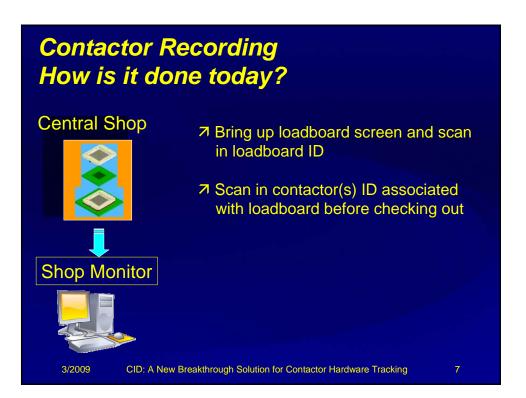

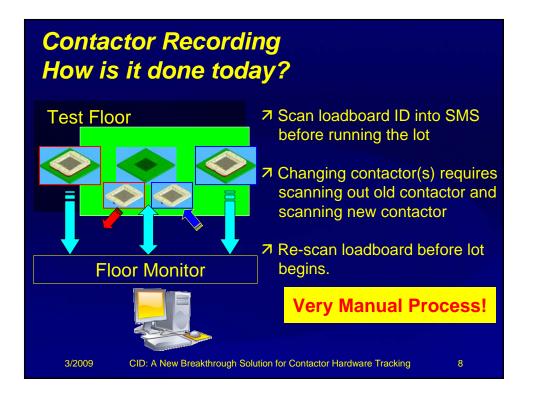

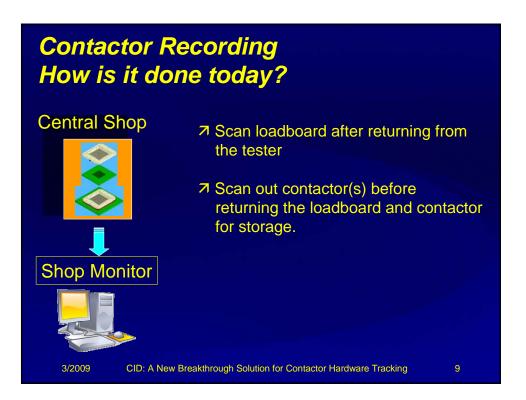

- Contactor Recording How is it done today?

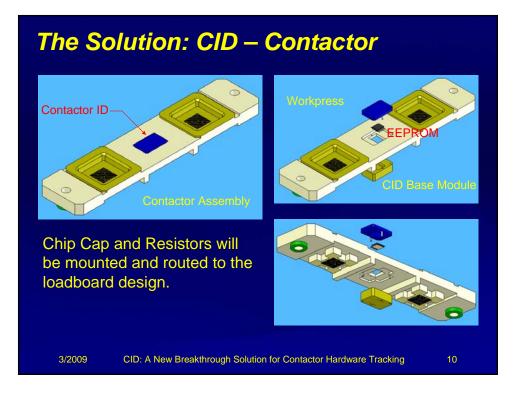

- The Solution: CID Contactor

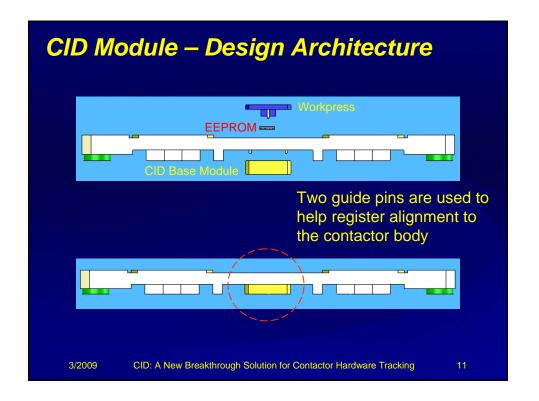

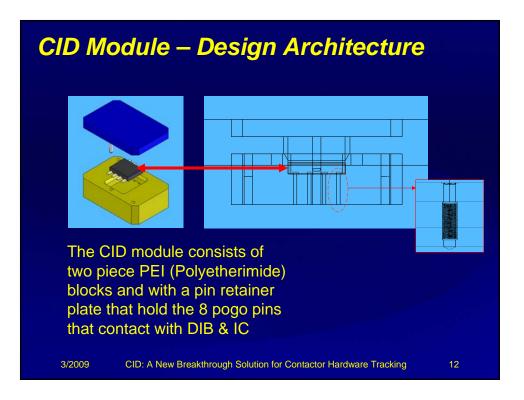

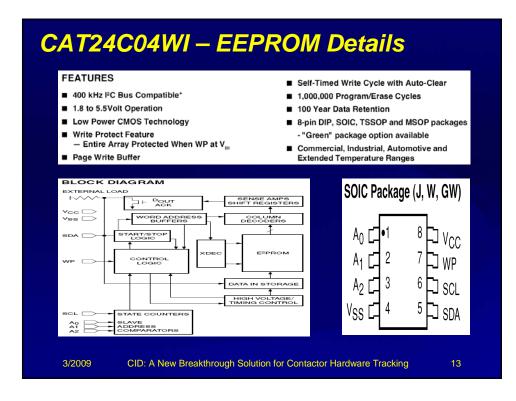

- **CID Module Design Architecture / Details**

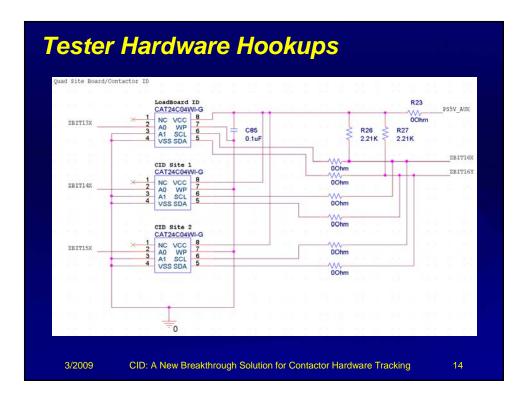

- Tester Hardware Hookups

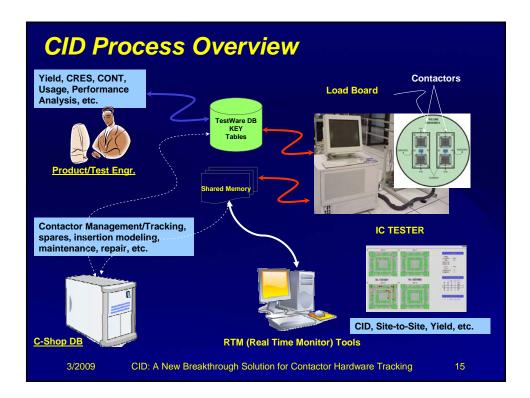

- Methodology CID Process Overview

- Results / Conclusions

3/2009 CID: A New Breakthrough Solution for Contactor Hardware Tracking

**Adventures in Test & Burn-in Operations**

## Background

- Contactor tracking is important for better inventory management and control – for better planning and cost reduction

- Accurate usage records are needed for proactive scheduling of maintenance

- To date, TI had used barcodes to manually track contactors and no accurate usage records exist to associate each contactors on how often it is used

## **Case for Action – Current Process**

Current practices uses sticker barcodes that are not permanent – They lose valuable information (history, insertion, setup issues).

The barcode peel off and fade when run under extreme conditions.

<sup>3/2009</sup> CID: A New Breakthrough Solution for Contactor Hardware Tracking

**Session 3**

**Session 3**

**Adventures in Test & Burn-in Operations**

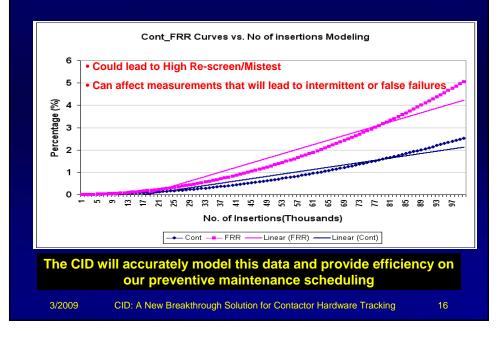

## **CID Insertion Modeling - Results**

Adventures in Test & Burn-in Operations

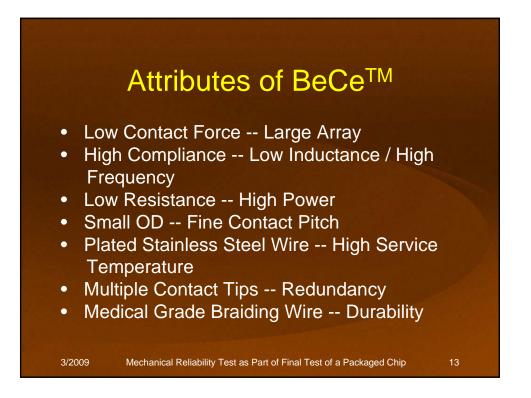

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

# Mechanical Reliability Test as Part of Final Test of a Packaged Chip

C-Y Li, T Wooden, SM Low, TM Korhonen Che-Yu Li and Co, Ithaca, NY Protos Electronics, Santa Clara, CA ADE Technologies, Singapore

2009 BiTS Workshop March 8 - 11, 2009

- Luu Nguyen's team at NSC have shown that power cycle test can be used and is 10x faster compared to thermal cycling test

- Integrated as a part of test socket,

- Stand-alone power cycle system, with many samples at a time

**Adventures in Test & Burn-in Operations**

**Adventures in Test & Burn-in Operations**

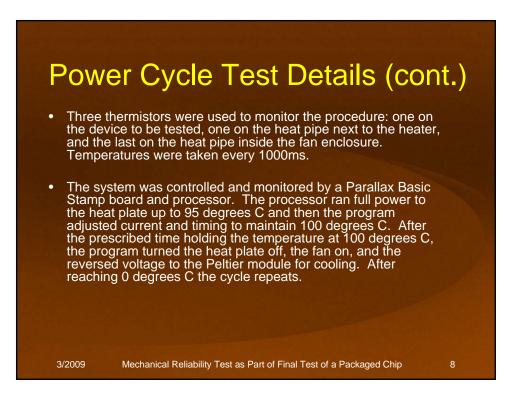

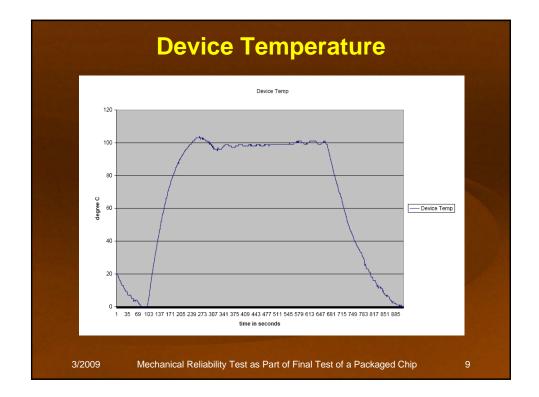

## Power Cycle Test Details

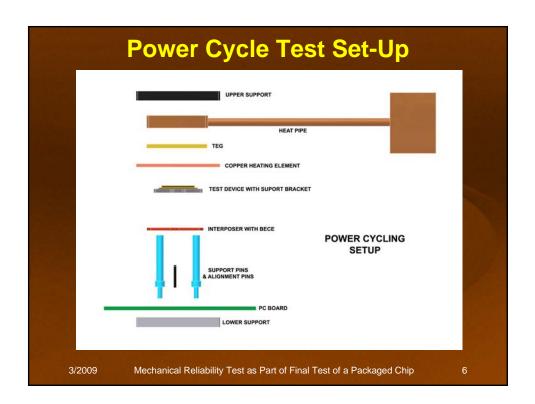

- Heating plate was made from 90 mil thick copper plate. Grooves were cut in the copper plate in which nichrome 60 resistance wire was inserted. The heating element was driven by HB-25 motor controller with PWM frequency of 9.2khz and a load current limit of 25 amps.

- 42 watt Thermoelectric/Peltier Module was placed next to heating plate. The device was used in the heating cycle to heat the device on one side with the added advantage of cooling the heat pipe and the upper aluminum support on the other side. By reversing the power to the Peltier module we were able to shorten the heating and cooling times.

- The heat pipe was placed on top of the Peltier module. To quickly remove the heat, the other end of the heat pipe was put in an enclosure with a fan.

3/2009 Mechanical Reliability Test as Part of Final Test of a Packaged Chip

Adventures in Test & Burn-in Operations

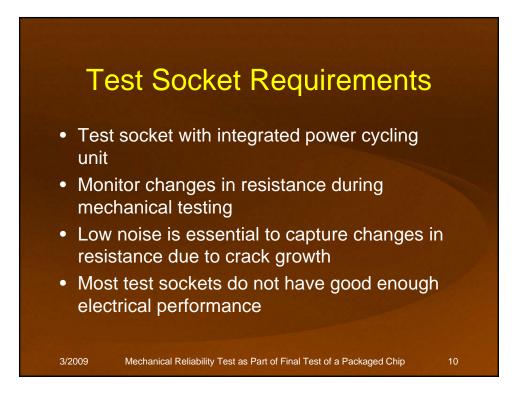

| Test Socket Requirements                                                                                                                                                                                                                                                                           |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <ul> <li>Low &amp; stable resistance of electrical contact <ul> <li>Failure monitoring</li> <li>High service temperature</li> <li>High power, high current</li> </ul> </li> <li>Other requirements <ul> <li>High frequency</li> <li>Large array</li> <li>Fine contact pitch</li> </ul> </li> </ul> |    |

| 3/2009 Mechanical Reliability Test as Part of Final Test of a Packaged Chip                                                                                                                                                                                                                        | 11 |

**Adventures in Test & Burn-in Operations**

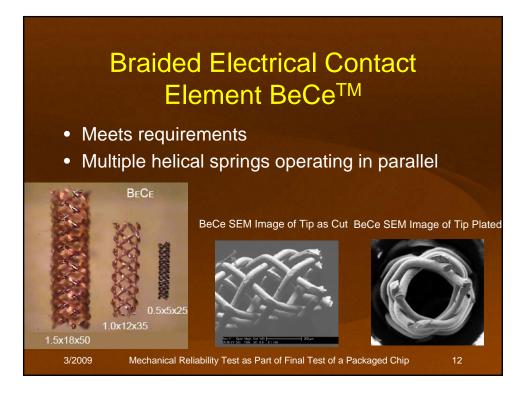

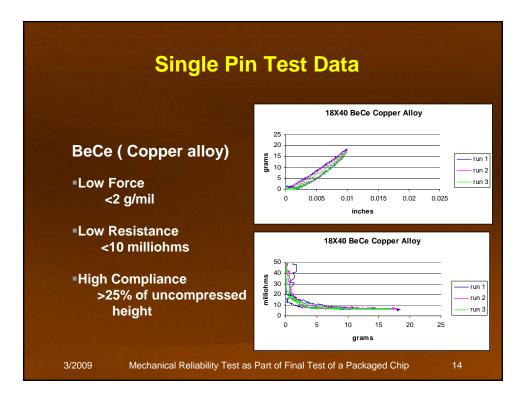

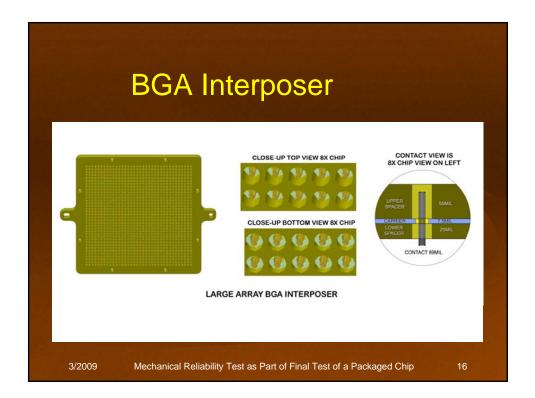

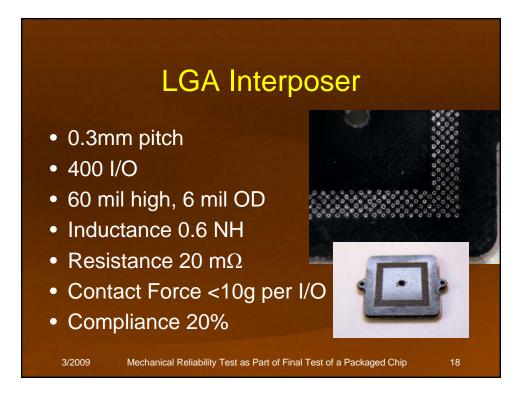

# BeCe Data for BGA Interposer

- 1 mm or 0.8 mm pitch

- 1.5 on 8 copper alloy BeCe

- 80 mil BeCe height

- 14 mil OD

- Resistance 7 m $\Omega$

- Inductance 0.6 nH

- Compliance 20%

- Array to 5000 I/O

3/2009 Mechanical Reliability Test as Part of Final Test of a Packaged Chip

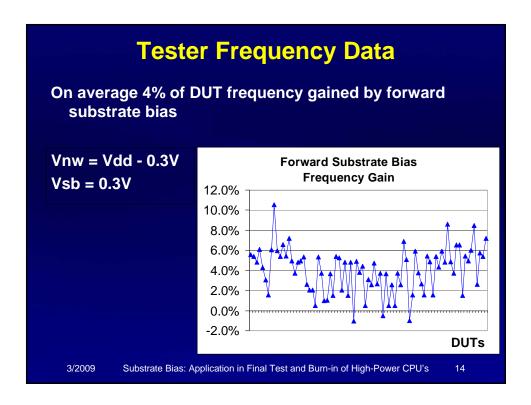

# Substrate Bias: Application in Final Test and Burn-in of High-Power CPU's

### Max Paransky Texas Instruments

2009 BiTS Workshop March 8 - 11, 2009

🐺 Texas Instruments

# High-Power Burn-in

Conditions determined by process technology and reliability requirements:

- Chip area coverage

- > Exercise all key structures (logic, memory, IO's)

- Time duration

- Voltage levels

> All transistors types powered above their normal use conditions

- Temperature

- > Silicon Tj above use conditions

3/2009 Substrate Bias: Application in Final Test and Burn-in of High-Power CPU's

**Session 3**

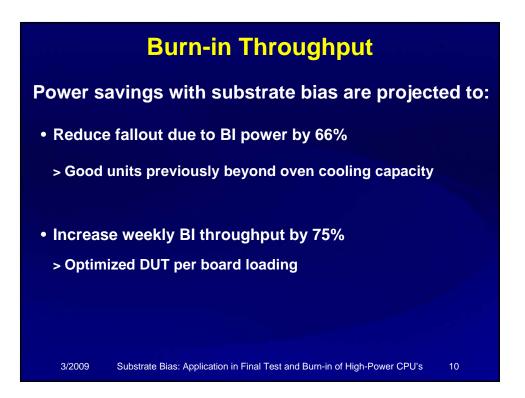

| Burn-in Oven                                                                       |  |

|------------------------------------------------------------------------------------|--|

| Burn-in ovens, boards and sockets have<br>constraints:                             |  |

| Thermal budget                                                                     |  |

| > Finite cooling capability per DUT                                                |  |

| Power budget                                                                       |  |

| > Only so many power supplies and amps per board                                   |  |

| Problem!                                                                           |  |

| These constraints limit how many units can be                                      |  |

| loaded at a time                                                                   |  |

| 3/2009 Substrate Bias: Application in Final Test and Burn-in of High-Power CPU's 3 |  |

|                                                                                    |  |

|                                                                                    |  |

|                                                                                    |  |

Adventures in Test & Burn-in Operations

**Session 3**

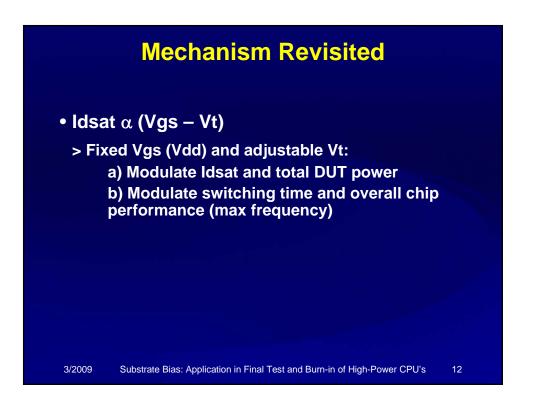

| Oven Complications                                                                        |

|-------------------------------------------------------------------------------------------|

| Vnw is positive                                                                           |

| > But occupies oven power supplies that could otherwise<br>be used for core Vdd           |

| Vsb is negative                                                                           |

| > Oven doesn't have a negative power supply                                               |

| > A custom board-level circuit was added for +DC/-DC<br>conversion                        |

| <ul> <li>Adjust thermal control to avoid under-temps for<br/>low-power samples</li> </ul> |

| > Tune oven heat/cool rate of response                                                    |

| > Tune oven ambient temperature                                                           |

| 3/2009 Substrate Bias: Application in Final Test and Burn-in of High-Power CPU's 8        |

**Adventures in Test & Burn-in Operations**

**Adventures in Test & Burn-in Operations**

**Session 3**