# **ARCHIVE 2009**

#### IC PACKAGING: GLOBAL TRENDS, TECHNOLOGIES AND NEXT GENERATION 3D SOLUTIONS

by

Brandon Prior Senior Consultant Prismark Partners

#### ABSTRACT

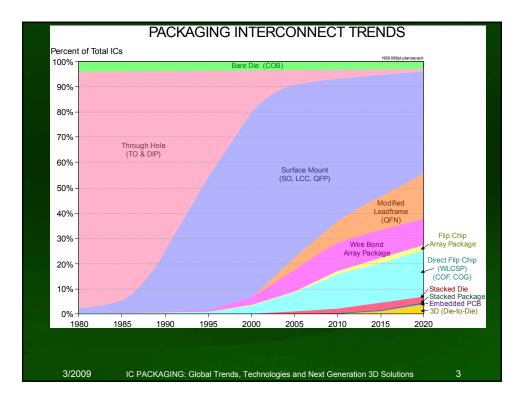

**IC** packaging solutions have been evolving in many ways that were forecast, and in some ways not predicted by any analysts. This presentation will look at the recent trends of IC packages in terms of package type, pitch, and integration for multi-chip and 3D solutions. In preparing for the next decade of innovations, this brief synopsis will provide a forecast for current advanced packages, and a look into future developments in 3D and package integration that may have an impact on overall test strategies and challenges going forward.

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2007 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

IC PACKAGING: Global Trends, Technologies and Next Generation 3D Solutions

#### Brandon Prior Prismark Partners

BiTS Workshop March 2009

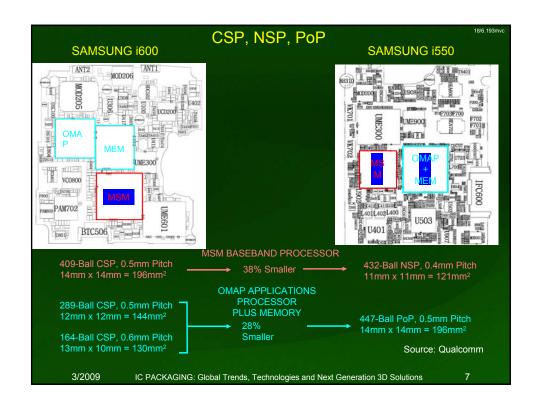

| QUALCOMM MSM6260 NS                                                                                                                                                                                                                                                                                              | SP PACKAGE 38.6/193mvc                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| <ul> <li>Qualcomm Baseband Processor</li> <li>HSDPA and EDGE phones</li> <li>Multimedia/applications processing</li> <li>Two stacked die: digital and analog</li> <li>11 x 11 x 0.85mm CSP, 432 balls</li> <li>Nanoscale package (NSP): 0.4mm pitch</li> </ul>                                                   |                                               |

| <ul> <li>11 x 11mm Two-Layer PCB Carrier</li> <li>90µm glass-reinforced dielectric</li> <li>115µm diameter laser vias</li> <li>22µm copper layers</li> <li>Min. line width 20µm</li> <li>Min. space 45µm</li> <li>38µm soldermask top</li> <li>48µm soldermask bottom</li> <li>Total thickness: 193µm</li> </ul> |                                               |

| <ul> <li>Total Package Thickness: 860µm</li> <li>Mold cap over carrier: 533µm</li> <li>Mold cap over top die: 213µm</li> <li>Mold cap over wire: 150µm</li> <li>Collapsed ball height: 135µm</li> </ul>                                                                                                          |                                               |

|                                                                                                                                                                                                                                                                                                                  | Photos source: Prismark/Binghamton University |

| 3/2009 IC PACKAGING: Global Trends, Technologies and N                                                                                                                                                                                                                                                           | Next Generation 3D Solutions 6                |

| NLOL               |                    | SP APPLICATION                                                | EAAIVIPLES                                                  |

|--------------------|--------------------|---------------------------------------------------------------|-------------------------------------------------------------|

| Mobile Phone       | Total Wafer<br>CSP | WL-CSP Applications                                           | Comments                                                    |

| Nokia N90          | 8                  | ESD/EMI, analog/power                                         | 6 – 25 I/O, largest die<br>3 x 4mm                          |

| Panasonic P901i TV | 7                  | ESD/EMI,<br>analog/power, other?                              | Up to 5mm die with 119 I/O<br>at 0.4mm pitch                |

| LG SB120           | 1                  | Power                                                         | 5.5mm, 72 I/O at<br>0.5mm pitch                             |

| Apple iPhone       | 4                  | ESD/EMI,<br>Bluetooth, WLAN                                   | Up to 4.7mm die with 69 I/C<br>at 0.4mm pitch               |

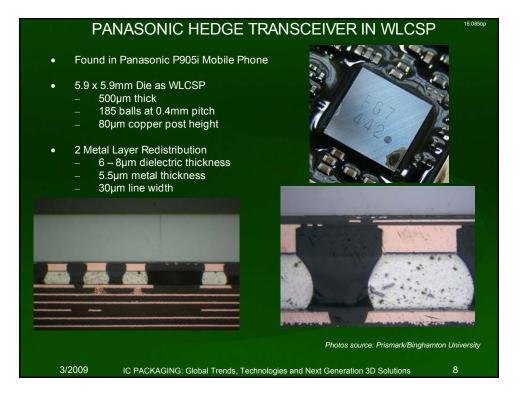

| Panasonic P905i    | 6                  | Transceiver,<br>Bluetooth, power,<br>TV tuner (two chips),GPS | 5 die use copper post tech,<br>up to 185 I/O at 0.4mm pitcl |

| Nokia 6220 Classic | 7                  | ESD/EMI, power, other?                                        | Up to 5mm die                                               |

| Nokia N95          | 8                  | EMI/ESD, analog,<br>Bluetooth, FM Radio                       | Up to 4mm die with<br>47 I/O at 0.5mm pitch                 |

| QUALCOMM MSM7200 fcPiP PACKAGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 48.6/193mvc |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| <ul> <li>15 x 15 x 1.4mm fcPiP Package</li> <li>543 balls, 0.5mm pitch</li> <li>Includes three die</li> <li>Digital baseband</li> <li>Analog baseband</li> <li>Memory</li> <li>Underfilled</li> <li>Packaged by STATS ChipPAC</li> <li>fcPiP Package Concept</li> <li>FC package base</li> <li>Digital baseband</li> <li>Internal stacked module</li> <li>Memory in LGA package</li> <li>Placed upside down in flip chip die</li> <li>Bare die</li> <li>Analog baseband placed on ISM</li> <li>Wire bonding of ISM and bare die</li> <li>To FC package base</li> </ul> |             |

| Overmold     Wire Bond Die     ISM     Flip Chip Die                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | TATSChipPAC |

| 3/2009 IC PACKAGING: Global Trends, Technologies and Next Generation 3D Solutions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20          |

|                                                                                                                                                                                                                                                                           | 108.1/085bp |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| FREESCALE REDISTRIBUTED CHIP PACKAGE<br>(RCP)                                                                                                                                                                                                                             |             |

| Freescale Fan-Out Wafer Level CSP Solution                                                                                                                                                                                                                                |             |

| <ul> <li>Ultra Low-k Compatible         <ul> <li>Pb-free</li> <li>Ultra-thin package approach (&lt; 0.5mm)</li> <li>No package substrate</li> <li>No wire bond/bumps</li> <li>Multichip solutions can still be done as backend process (PoP, etc.)</li> </ul> </li> </ul> |             |

| <ul> <li>Volume Production Planned in 2009         <ul> <li>Low volume production in Tempe</li> <li>First production in Q1 2009 using SMARTMOS die for consumer application</li> <li>Wireless handset devices to start production in 2H 2009</li> </ul> </li> </ul>       |             |

| Looking for Manufacturing Partners                                                                                                                                                                                                                                        |             |

| Die Encapsulant Routing BGA                                                                                                                                                                                                                                               |             |

| Source: Freescale                                                                                                                                                                                                                                                         |             |

| 3/2009 IC PACKAGING: Global Trends, Technologies and Next Generation 3D Solutions                                                                                                                                                                                         | 26          |

|                     | 108.1/105bp                                                                                                                                                                                                                                                       |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FAN-                | OUT WAFER LEVEL CSP – SUMMARY                                                                                                                                                                                                                                     |

| Process:            | Leading processes are based on reconfigured wafer that use fab-like redistribution process (photolithography/plating). 200 and 300mm wafer sizes.                                                                                                                 |

| Costs:              | RDL solutions for a 300mm wafer (at ~ \$250) are cost effective when die I/O density is high. However, a reconfigured wafer may have half as many die, doubling cost.                                                                                             |

| Production Status:  | Approaching volume production at Freescale and Infineon/ASE. Q1<br>2009 – Iow volumes, Q4 2009 – high volumes.                                                                                                                                                    |

| Business Logistics: | "Assembly" yield is drawback that has plagued this concept since<br>the 1980s or earlier. If process does not achieve better than 99.5%<br>yield, then must be reworkable, or a very low value die. Die sourcing<br>from multiple companies can also be an issue. |

| Other Limitations:  | A solution to support multiple die of various configurations is where this technology fits. Also, offers extension of WLCSP for pad limited die.                                                                                                                  |

| 3/2009 I            | C PACKAGING: Global Trends, Technologies and Next Generation 3D Solutions 27                                                                                                                                                                                      |