#### **ARCHIVE 2008**

2008

#### Key Challenges and Technology Trends in Socket Design

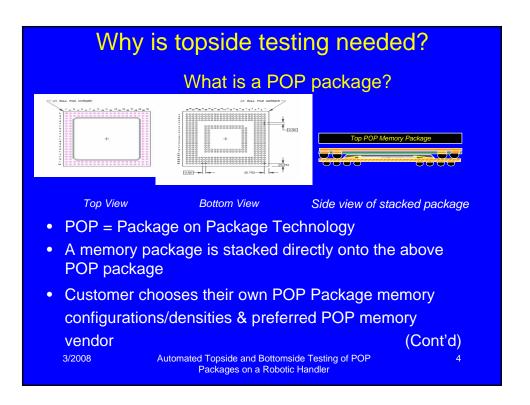

"Automated Topside and Bottomside Testing of POP Packages on a Robotic Handler" Eric Pensa, Willie Jerrels Texas Instruments

"High Speed Contactor Interconnect" David Mahoney Xilinx, Inc. Hongjun Yao Antares Advanced Test Technologies

"Particle Interconnect: Simple and Effective Socket Solution" Robert Howell Exatron

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2008 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Key Challenges and Technology Trends in Socket Design

TEXAS INSTRUMENTS

# Automated Topside and Bottomside Testing of POP Packages on a Robotic Handler

Eric Pensa Willie Jerrels Co-author Texas Instruments MAKE Test Handler-Interface Engineering

March 12, 2008

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

3/2008

Automated Topside and Bottomside Testing of POP Packages on a Robotic Handler 5

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

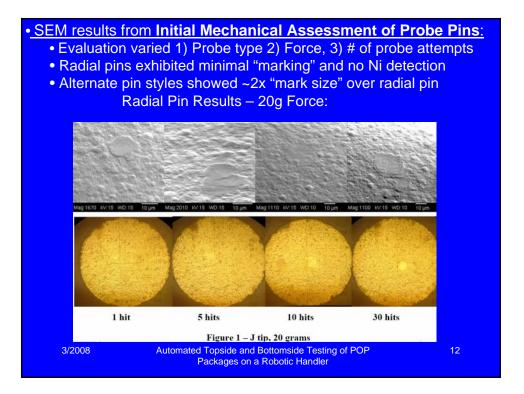

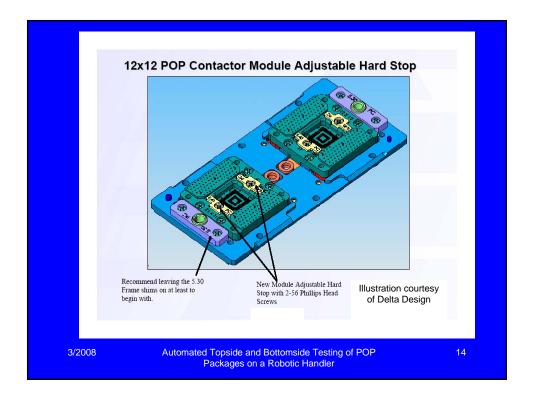

**Current Status of Topside Testing** a) "Retainers" were added to the handler nest for pogopin to pad alignment b) Nest "ceiling" was lowered to counter any package warpage c) Single ended BGA pogopins replaced w/ double ended as used on 14x14 kit d) Adding hardstop height with Kapton tape helped; therefore variable hardstops on the contactor were offered [5.30 thru 5.45mm in .05 steps] to deal with package thickness variances e) Variable hardstops also added to the contactor modules to replicate the success of hand test lids w/ hardstops closer to the POP unit under test by reducing package flexing possibility finally both chucks for the 1st time recorded 0% Bin 8 for 1st pass test! f) Same chuck/nest assemblies were transferred to TI Asia; 0% Bin 8 was achieved with same units tested in Dallas (Cont'd) Automated Topside and Bottomside Testing of POP 3/2008 16 Packages on a Robotic Handler

**Key Challenges and Technology** Trends in Socket Design

#### Future Requirements of Topside Testing

Where are we/what have we learned:

- Performing both top and bottomside testing is a "very fine balancing act"

- Nest issues contributed to miscontact in the following ways: a) new nest material was needed to avoid expansion due to moisture

b) nest pogopin tip shape, size & XY movement required much attention

c) nest pocket design & QC process required enhancements over existing approaches that have served bottomside nests well for vears

POP package issues contributed to miscontact in the following ways: a) using daisy chained devices were not as helpful in kit design for topside test

b) package warpage caused offsets to topside pads

c) sawing process was changed to reduce offsets to topside pads d) dimensions and warpage need to be better controlled than for

packages only needing bottomside test; topside nests are less tolerant of package variations than typical nests (Cont'd) 3/2008 17

Automated Topside and Bottomside Testing of POP Packages on a Robotic Handler

#### Future Requirements of Topside Testing

- Will new nest designs be needed for thinner POP packages that are more prone to warpage?

- Topside nests and hand test lid assemblies are very expensive with long lead times; they need to have maximum flexibility to accommodate package thickness differences

- Will new nest designs be needed for POP packages with bare die on topside?

- Current testing is for single site; what challenges will multi-site testing present?

(Cont'd) 18

Automated Topside and Bottomside Testing of POP Packages on a Robotic Handler

3/2008

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

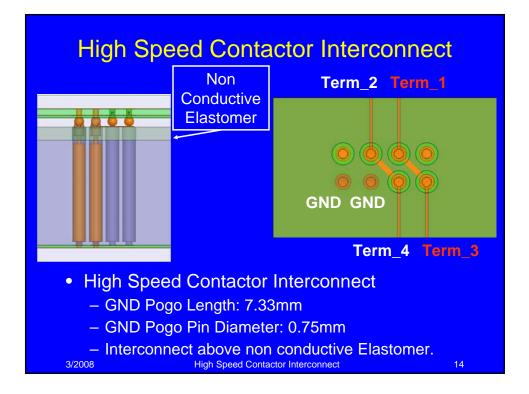

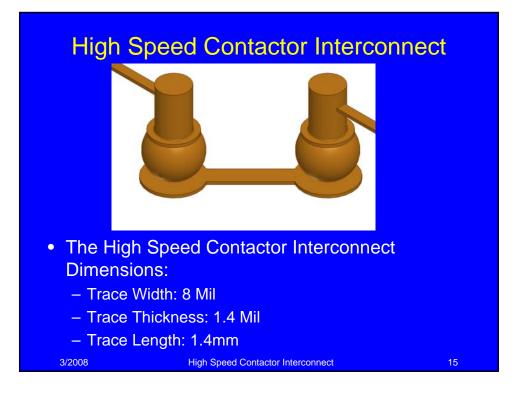

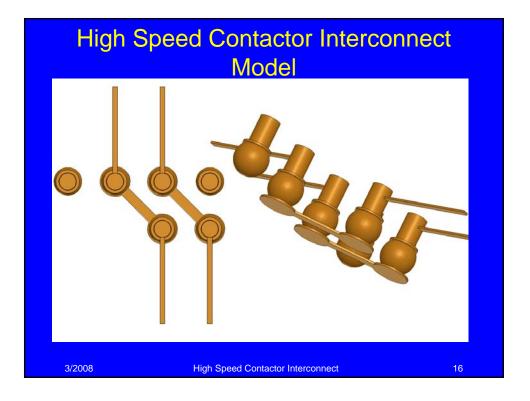

#### High Speed Contactor Interconnect

2008 Burn-in and Test Socket Workshop March 9 - 12, 2008

David Mahoney Xilinx, Inc. Sr. Product Engineer Hongjun Yao Antares Advanced Test Technology Signal Integrity Manager

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

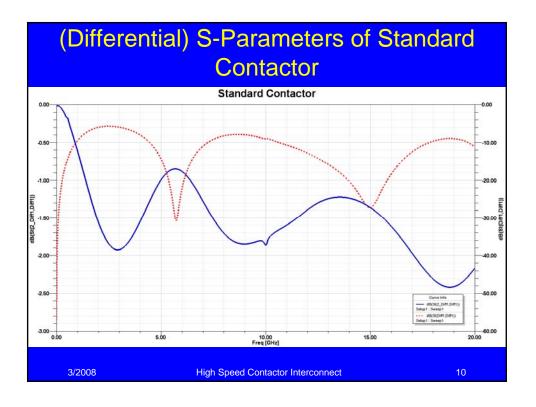

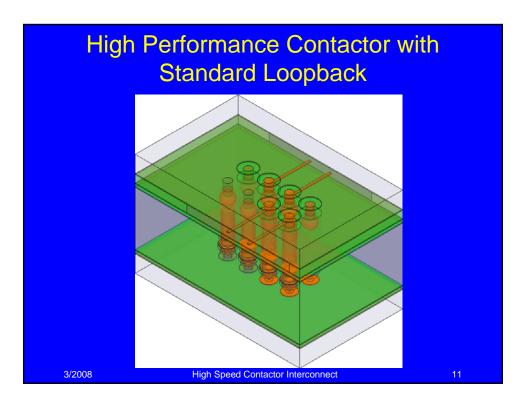

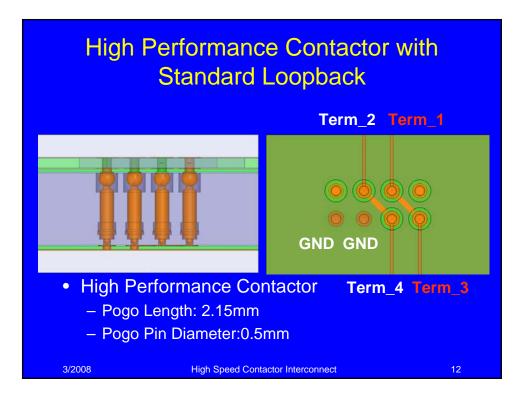

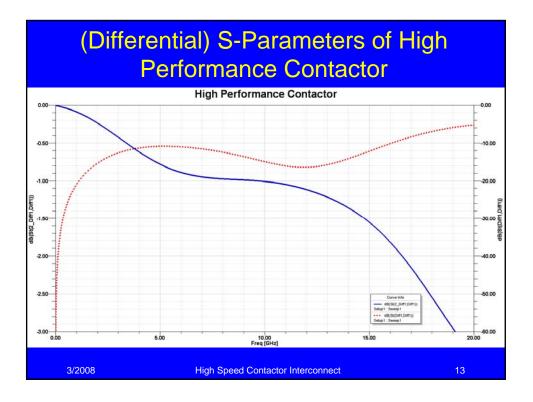

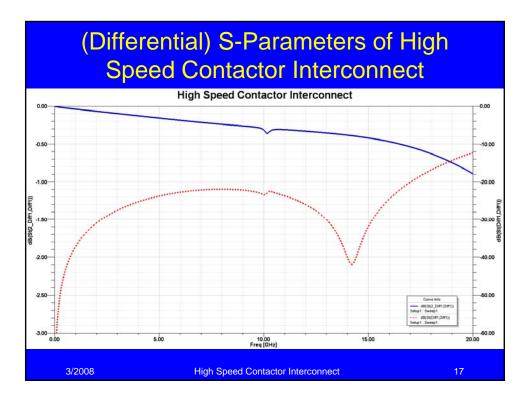

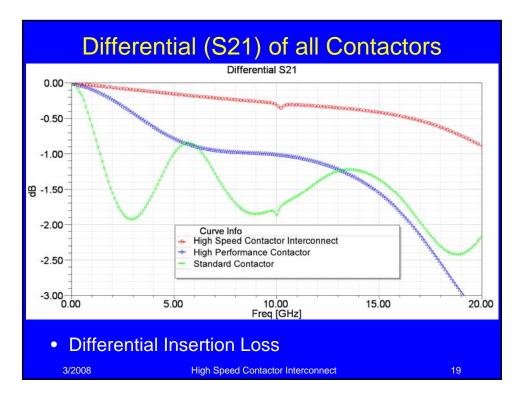

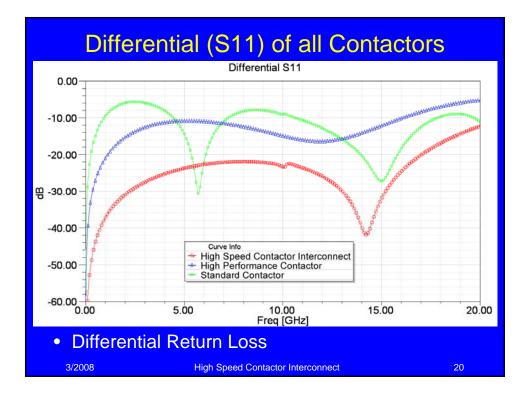

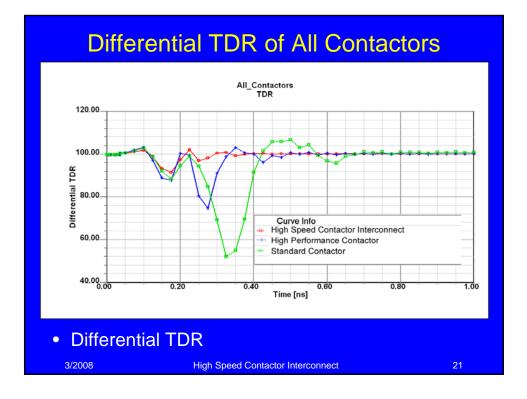

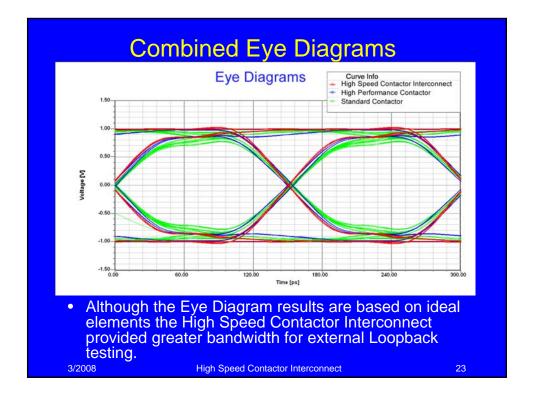

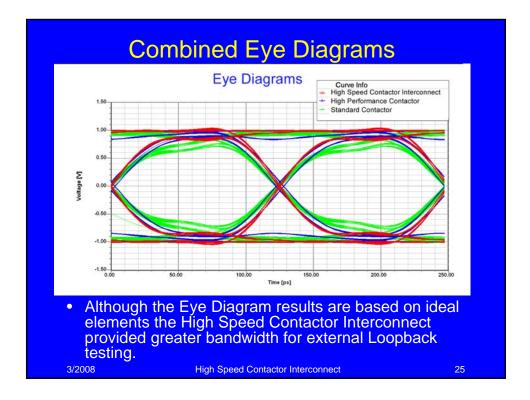

#### High Speed Contactor Interconnect Summary • The High Speed Contactor Interconnect

- demonstrated greater Bandwidth than a High Performance Contactor with standard loopback traces on the PCB.

- The High Speed Contactor Interconnect maintained both greater working range and higher bandwidth than the High Performance Pogo Pin Contactor.

- The addition of an interconnect in the socket provides greater bandwidth for loop back testing purposes without having to change the entire socket to high performance pogo pins.

3/2008

High Speed Contactor Interconnect

Paper #2

26

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

3/2008

# **Session 6**

Key Challenges and Technology Trends in Socket Design

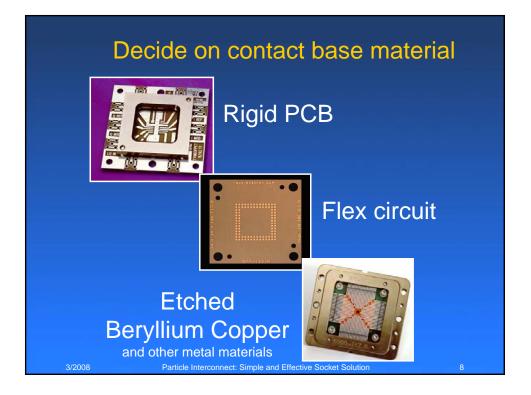

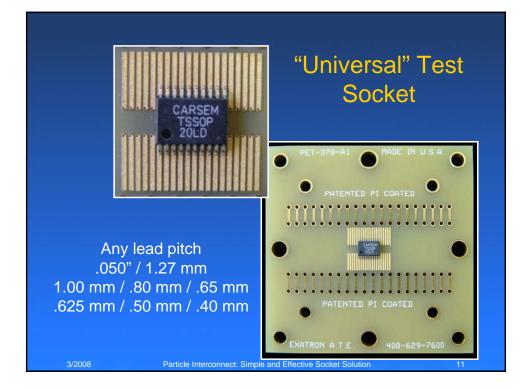

#### Rigid PCB Applications

- Typically 0.010" or thicker

- Standard FR-4 is the most popular material

- Ceramic, Teflon, G-10 and other special base materials are available

- Works best for devices with flexible leads

SOIC, SSOIC, TSOP, SOT, PLCC, Power Transistors

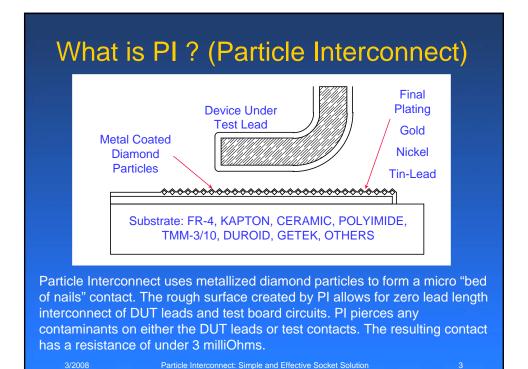

Particle Interconnect: Simple and Effective Socket Solution

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

# <section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

Key Challenges and Technology Trends in Socket Design

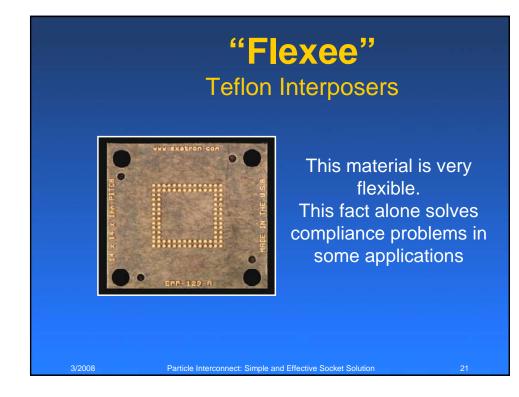

|         | Which materials?                                                                                               |

|---------|----------------------------------------------------------------------------------------------------------------|

| Teflon: | Best electrical properties (best for RF / 40 GHz)<br>Most flexible<br>Shortest mechanical life                 |

| Kapton: | Good electrical properties (includes most RF)<br>Most popular to date<br>100K contacts minimum mechanical life |

| FR-4:   | Basic electrical properties<br>Allows for best mechanical compliance<br>100K contacts minimum mechanical life  |

| 3/2008  | Particle Interconnect: Simple and Effective Socket Solution 17                                                 |

Key Challenges and Technology Trends in Socket Design

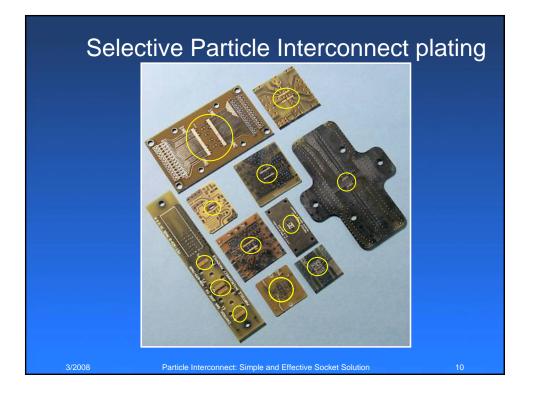

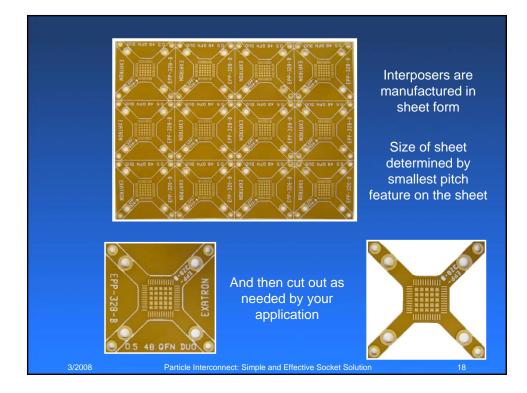

|            | Kapton Interp         | osers              |

|------------|-----------------------|--------------------|

|            | Simple 2 sided Gerb   | er File            |

| Easily ada | apted to ANY existing | g socket footprint |

| Multip     | ole socket patterns o | n one sheet        |

|            | Pitch to 0.3mn        | n                  |

|            |                       |                    |

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design

Key Challenges and Technology Trends in Socket Design