2008

**Session 1**

#### **ARCHIVE 2008**

#### FINE PITCH PCB CHALLENGES

"Super-Sockets: Integration of Technology From Test Board Into Socket Assembly"

Darren Young

Anestel Corporation

Tom Bresnan

R&D Circuits, Inc.

"Column Failure on Memory Burn-In Boards"

Yogesh Ahuja

Pycon, Inc.

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2008 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

**Fine Pitch PCB Challenges**

# Super-Sockets: Integration of Technology from Test Board into Socket Assembly

March 9 - 12, 2008

Tom Bresnan

Sales Manager

#### **Fine Pitch PCB Challenges**

#### **Overview**

- Smaller, Faster, Less Expensive

- Shifting the Burden

- Removing Restraints

- Integrating Components

- Impact on Cost of Test

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

3

# Smaller, Faster, Less Expensive... The Trend Continues

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

#### **Fine Pitch PCB Challenges**

#### **Needs of Manufacturers Smaller** Faster Less Expensive Packages Board Costs Higher Freq Socket Costs Pitches Lower Inductance (price per pin) Lower Down Time Contact Resistance Super Sockets: Integration of Technology from Test Board into Socket Assembly 3/2008

## Robbing Peter to Pay Paul

- There are currently individual solutions to each need

- Where is the comprehensive solution?

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

7

# Have Load Board Manufacturers Met Their Match?

#### 0.4 mm pitch:

- 100 microns drilled holes + no change in board thickness = High Aspect Ratio

- How do we get to 0.4 mm pitch and beyond for high layer count, thick load boards?

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

# What if We Could Shift the Burden?

- What if...

- ...the footprint of the DUT no longer dictated the pitch and layout of the load board

- ...test board design could remain static

- ...standard test boards could be used

- ...there was no compromise to performance or space of the socket

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

9

# Removing Footprint Restraints

- By incorporating test board technology into the socket assembly:

- Footprint restraints are removed

- Pitch is no longer an issue!

- How is this done?

- Two methods

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

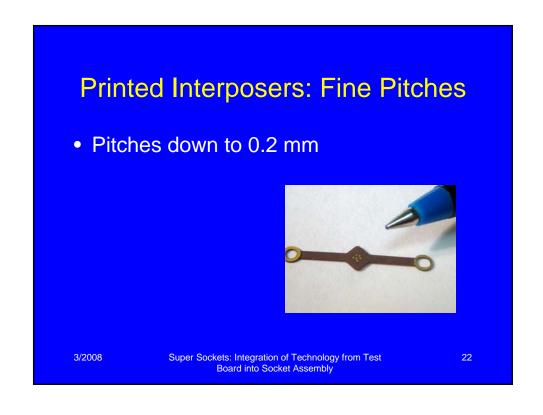

**Fine Pitch PCB Challenges**

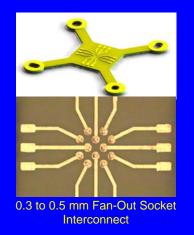

- Traces are printed on a polyimide substrate

- Traces transform pitch and footprints (ie. 0.3 mm device pitch to 0.8 mm board pitch)

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

11

# Method 1: Fan-Out Using Printed Interconnect

- Ideal for QFN/MLF style packages

- Can also be used for low pin count BGA packages

0.3 to 0.5 mm Fan-Out Socket Assembly

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

**Fine Pitch PCB Challenges**

Printed fan-outs as a socket insert

**Top View**

**Bottom View**

Fan-Out Socket Insert: 0.3 mm

Device Pitch to 0.5 mm Socket Pitch

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

13

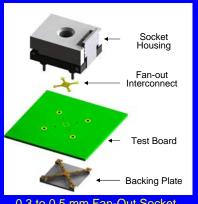

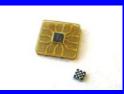

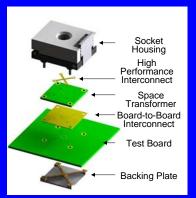

# Method 2: Space Transformer

- Multilayer PCB in the socket assembly

- Transforms pitch and footprint or descrambles pin layout

Socket Assembly with Space Transformer

- Compression mounts to load board

- Can be used with most compression mount sockets

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

## **Space Transformer Applications**

- Descrambler

- Pin out change

- Re-utilization

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

## **Space Transformer Attributes**

- Organic Materials

- Matched to load board

- Impedance Controlled

- 63.5µ Line/Space

- Hi Pin Count 400+

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly 17

# **Space Transformer Attributes**

- .25mm pitch capable

- Thru Hole to HDI Buildup

- Micro-drilling to laser micro-via's

- Zero 'Z' axis increase

- Integrated in socket

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

**Fine Pitch PCB Challenges**

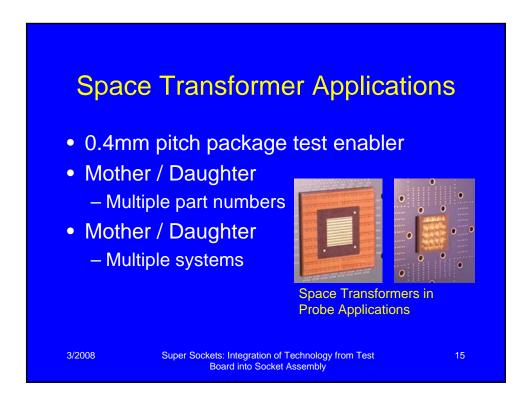

## Solution For High-Performance, Fine Pitch Socket Assemblies

- High performance socket housing and interconnect

- Space Transformer with impedance control

- Low inductance compression mount board-to-board interconnect

ConnectFlex™ with Space Transformer High Performance, 0.3 mm Device Pitch, 0.8mm Board Pitch Socket Assembly

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly 19

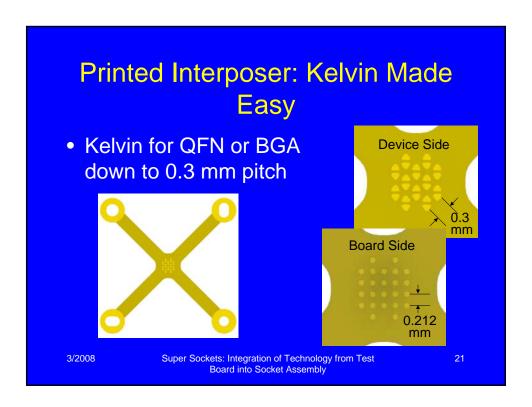

# Printed Interposer: An Enabling Technology

- Fan-out uses printed interposer technology

- Pin contactors are printed on polyimide

- No spring pins or stamped contactors

- Uses a conductive compliant material

Conductive Compliant Material

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

**Fine Pitch PCB Challenges**

# Integrating Other Elements of the Test Board

- Decoupling under the DUT (bottom side)

- Decoupling near the device (top side)

- Resistors to tune circuits

- What if you could put these in the socket?

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

23

#### Passives in the Socket Assembly

- Passives can be placed right next to devices under test

- Possibilities of increased performance for high speed devices

- Benefits are still under debate

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

**Fine Pitch PCB Challenges**

#### Cost of Test

- Current economic driver

- Price per pin

- Socket Pitch

- Number of insertions

- Load Board Pitch

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

25

#### Cost of Test

- Changing the socket architecture creates a new economic driver

- Price per insertion

- New factors that lower costs

- Less expensive machined socket housings

- Less expensive molded socket tooling costs (\$10,000 vs \$100,000)

- Standard Test Boards

- Less expensive test boards

- Reusable test boards

- Increased life of test boards

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

## **Summary**

- Need for smaller, faster, and less expensive

- Integration of technology from test board into socket assembly

- Burden shifted away from load board

- A new paradigm in test socket architecture will enable IC Manufacturers

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

27

# Acknowledgements

Afshin Nouri, Contech Solutions, Inc

3/2008

Super Sockets: Integration of Technology from Test Board into Socket Assembly

#### **Fine Pitch PCB Challenges**

# Column Failure on Memory Burn-In Boards

2008 Burn-in and Test Socket Workshop March 9 - 12, 2008

Yogesh Ahuja Pycon Inc. Santa Clara, CA

#### Introduction

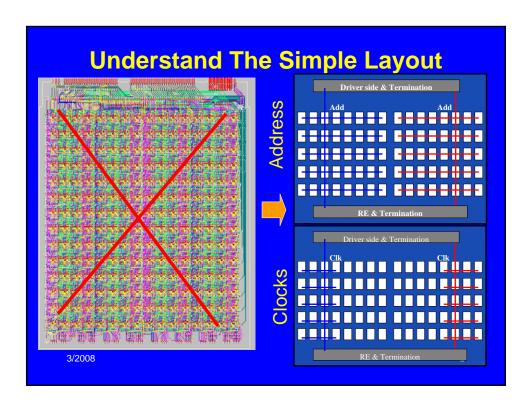

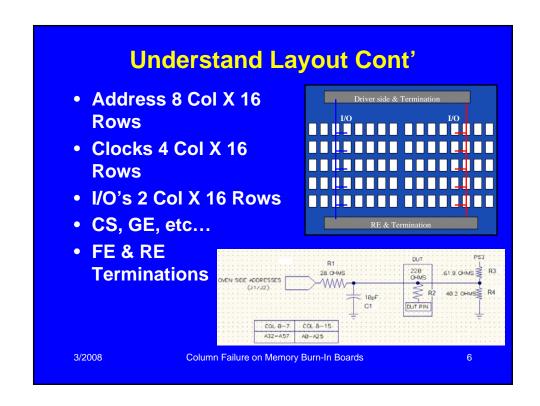

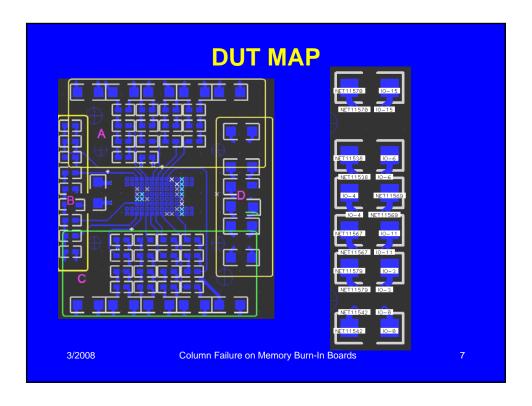

- Capacity, Capacity, & Capacity determines Burn-in Board design.

- Large boards crowded with up to 400 sockets

- Average design ties half the board address lines. (200 devices)

- Average design ties two columns together for I/O's. (50 devices)

- Phantom failures can take out 15% or 50% of capacity

- Severe problems lead to complete abandonment of the Vendor, Engineer or Product Line

3/2008

Column Failure on Memory Burn-In Boards

#### **Assumptions**

- Fully functioning design

- Tuned

- Bring-Up problems eliminated

- System Reads/Writes to the Complete Memory Map

- System reports Good Vs. Bad devices

- Monitored BI

- All Channels on the DUT are isolated with Resistors

3/2008

Column Failure on Memory Burn-In Boards

3

## Part 1

**Gather Information**

#### **Fine Pitch PCB Challenges**

#### **Fine Pitch PCB Challenges**

# Part 2

Eliminating Simple Failures

**Fine Pitch PCB Challenges**

#### **Uni-Directional Signal Failures**

- Address, Clock & CS propagate from Driver to DUT only

- DUT is protected using isolation resistors

- Device Failures

- Dead Short in the DUT: Adr to GND results in a loss of few mV of VOH to DUT. No Column Failures

- Dead Short in the DUT: Adr to VCC results in a gain of few mV of VOL to DUT. No Column Failures

#### **Uni-Directional Failures Cont'**

- If Column failures show up on Uni-Directional signals the problem is outside of the DUT region.

- Corrupt Tuning/Termination components.

- Bad VIAS

- Opens/shorts on traces

- Gross failures

3/2008

Column Failure on Memory Burn-In Boards

#### **Fine Pitch PCB Challenges**

#### **Solution**

- Corrupt Tuning/Termination components.

- Run a Static (RLC) test to find bad components

- Simple test, eliminates problems quickly

- Via Problem

- Run a Static test to find location

- Only board manufacturer can fix problem

- CAF & cracked barrels are mostly incurable

- Opens/shorts on traces

- Open traces are rare and signify mishandling

- Shorts are common on poorly maintained boards

- PM & Cleaning can eliminate problem

3/2008

Column Failure on Memory Burn-In Boards

11

#### Part 3

**Eliminating Complex Failures**

#### **Fine Pitch PCB Challenges**

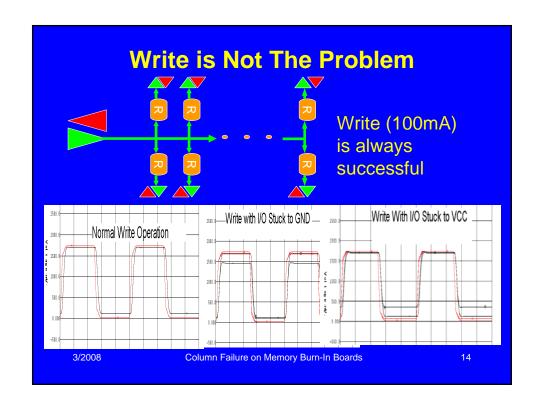

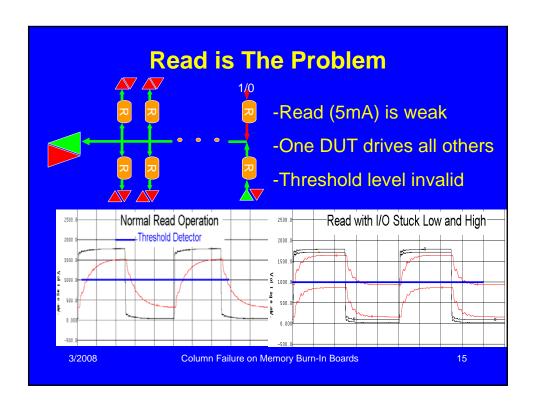

#### **BI-Directional Signal Failures**

- I/O Lines have bi-directional data

- DUT is protected using isolation resistors

- System Writes with >100mA of current

- Device Writes with <10mA of current</li>

- Frequency of failure (Ascending order)

- Gross Failures (See Uni-Directional Failures)

- Burn-In Board quality issues, CAF, PM

- Device I/O Stuck at High/Low

3/2008

Column Failure on Memory Burn-In Boards

#### **Fine Pitch PCB Challenges**

#### **Solution Without Devices**

- Line stuck High or Low

- The same error can also be caused by socket pins being physically shorted on the board

- PM, Cleaning Static test can eliminate the problem

- CAF cannot be eliminated

- Run an empty board with 0000 to weed out bad BIB

- Column failures predict physical damage with BIB

- Detects socket I/O pins shorted to VCC

3/2008

Column Failure on Memory Burn-In Boards

#### **Solution With Devices**

- Line stuck High or Low

- Run fully loaded bib with 0000 to weed out bad Devices

- Column failures predict device stuck high

- Run fully loaded bib with 1111 and lowering threshold level to weed out bad devices

- Column failures predict device stuck low

- Possible to continue BI with lower threshold level

- Physical Location Probe Using DMM

- All but one I/O will show the same Resistance to GND/VCC

- DUT side of Resistor on one location will be dead short

3/2008

Column Failure on Memory Burn-In Boards

17

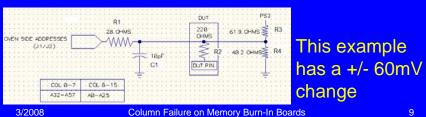

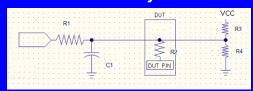

#### Add fault tolerance in the system

- Determine the amplitude of the signal with the fault.

- No Short

- Vh = (R4/((R3//R2)+R4)) x VCC

- VI = (R4//R2)/((R4//R2) +R3)) x VCC

- Short to GND

- Substitute R4 with Rx = R4//R2

- Short to VCC

- Substitute R3 with Ry = R3//R2

3/2008

Column Failure on Memory Burn-In Boards

#### **Fine Pitch PCB Challenges**

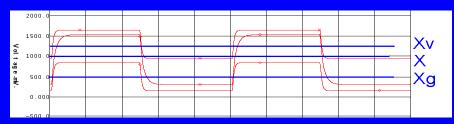

- Six values determine three threshold levels

- Vh VI Normal Operation: X

- Vh VI Short to Gnd: Xq

- Vh VI Short to VCC: Xv

- Dynamically adjust threshold level in system

- Set Threshold level to X

- If (2 Column Failures) then

- Xg -> X and retest

- If (2 Column Failures) then

- Xv -> X and retest

#### **Conclusion**

- Understand the simple style layout

- Almost all failures will resemble the channel assignment

- Unidirectional failures are outside of the socket region

- Bidirectional failures are inside the socket region

- Prescreen empty boards with 0000 to find BIB faults

- PM boards regularly to avoid debug hours

- Implement fault tolerance at system level

3/2008

Column Failure on Memory Burn-In Boards

**Fine Pitch PCB Challenges**