2008

### **Keynote Speaker**

### **ARCHIVE 2008**

# "Packaging & Assembly in Pursuit of Moore's Law and Beyond" Karl Johnson Ph.D.

Vice President and Senior Fellow Advanced Packaging Systems Integration Laboratory Freescale Semiconductor

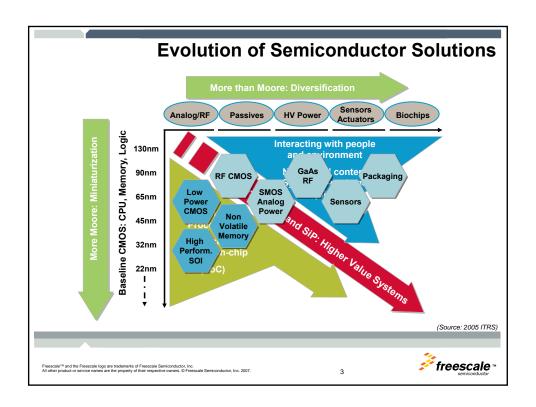

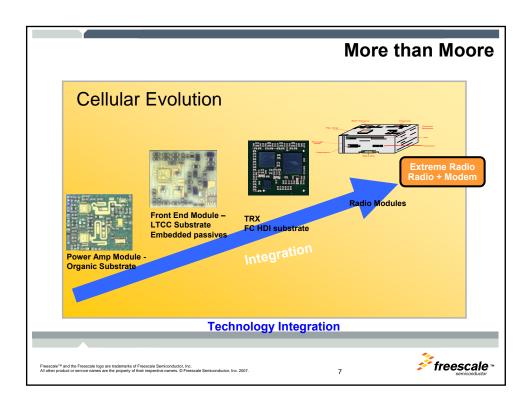

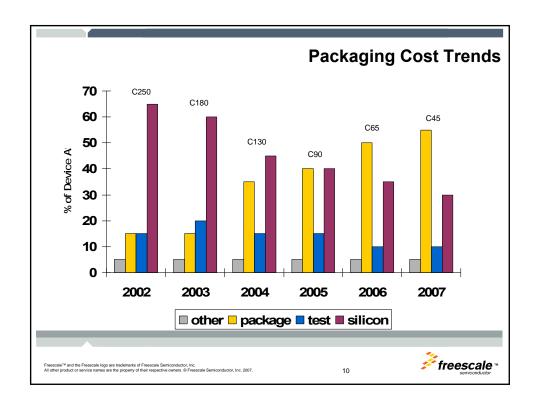

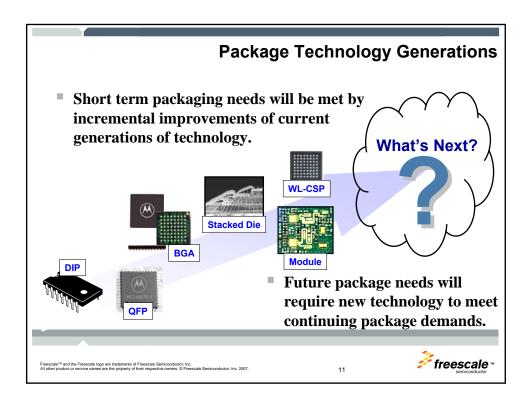

As the semiconductor industry continues in its pursuit along the curve of Moore's Law from 65 nm to 45 nm, 32 nm and beyond, the challenges for packaging and assembly technologies are becoming significant. Packaging can no longer be thought of as a back end process largely independent of the silicon and product definition. The assembly and packaging technologies have become an integral component in the overall performance, figures of merit and cost competitiveness of these new generations of products. Further, market trends and customer expectations are moving rapidly into higher levels of system integration and system solutions. This trend is moving products toward greater levels of integration and diversification beyond the scaling of Moore's Law.

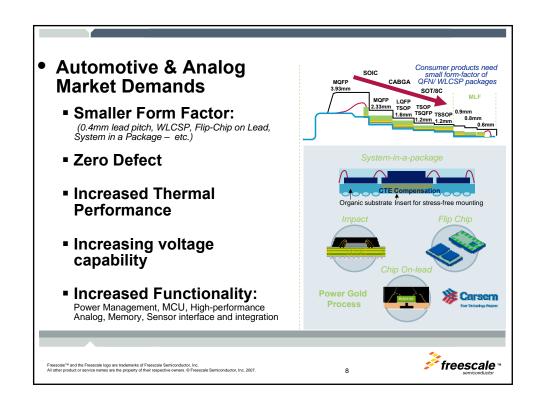

Rapid market growth in areas beyond the traditional drivers for the semiconductor industry, such as computer and industrial applications, into consumer applications with semiconductor based systems becoming pervasive in all aspects of our lives is placing additional demands on packaging. These demands include but are not limited to lower cost, shorter time to market and greater flexibility and reuse.

This presentation addresses these new challenges, the trends in packaging and assembly and some unique solutions that are being developed and implemented. A broad spectrum of products solutions from system-on-chip, 3D, system-in-package as well as "wafer level" assembly are discussed.

Dr. Johnson leads the Advanced Packaging Systems Integration Laboratory (APSL) within the Freescale Technology Solutions Organization. This laboratory is responsible for the development and implementation of a broad spectrum of packaging advances in support of Freescale Semiconductor's business and strategy. These innovations are in areas which include analog power, RF and sensor modules, automotive applications and advanced wirebond and flip chip packages.

### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2008 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

### **Agenda**

- Packaging Evolution

- Market / IDM Evolution

- Challenges

- Advanced Package Development

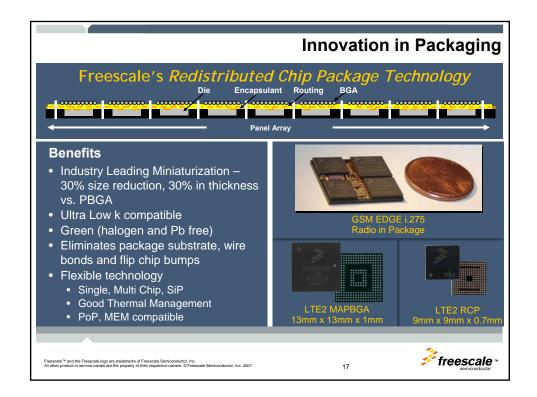

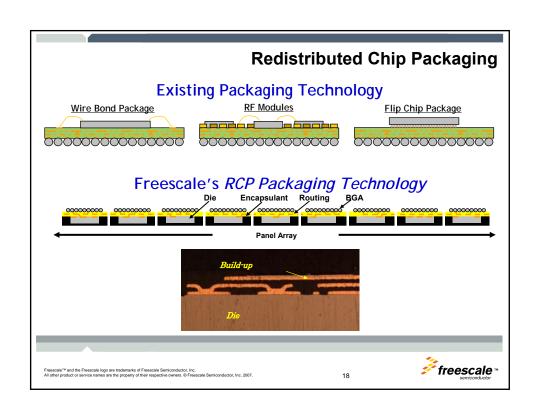

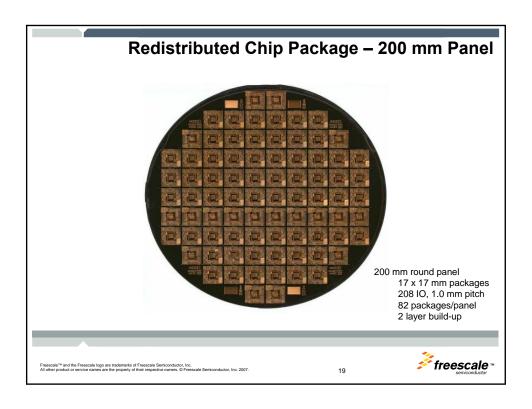

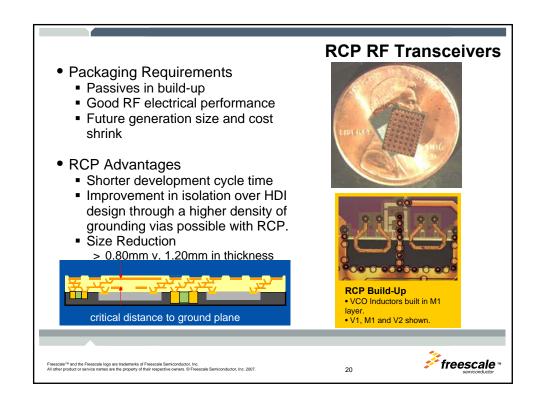

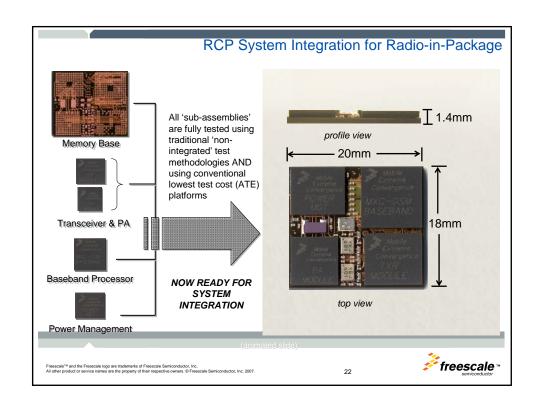

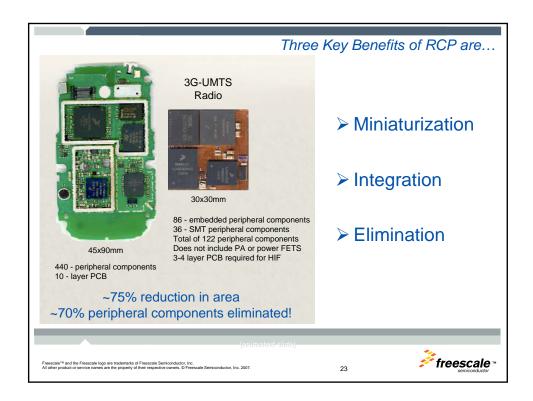

- Freescale's Redistributed Chip Package (RCP)

- Conclusion

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007

\*freescale

# Market / IDM Evolution • The market drivers have evolved: Industrial Computer Wireless Automotive Customer • The market demands system solutions • Greater functionality with software • Faster Time to Market (product refresh) • Cost, Cost, Cost • Flexibility and reuse • Society demands "Green" solutions

### **Challenges**

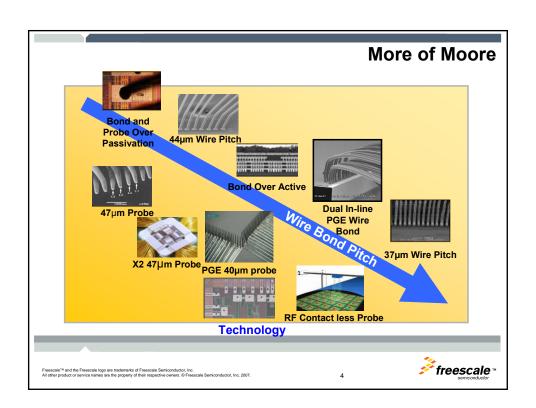

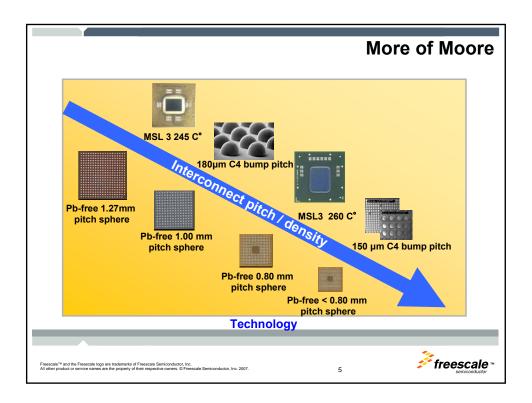

- System on a Chip (More of Moore)

- Compromised subsystem performance

- Signal integrity

- parasitics, cross coupling

- Power and ground (core @ 1.0 volt)

- Parasitics inductances to ground, IR drop

- Design Cost

- Time to Market

- Decreasing flexibility and reuse

- Pad Limited Designs

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007.

freescale •

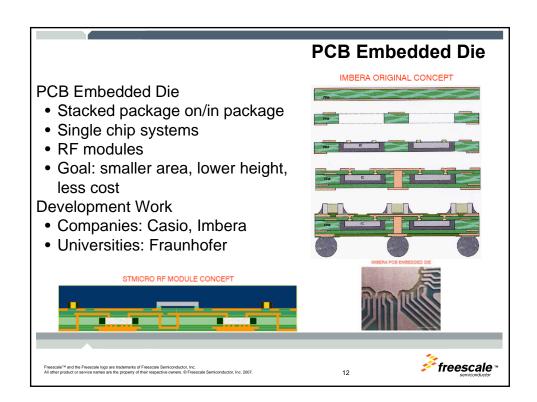

# Main die embedded in PCB (EWLP) • Other die on top of board (WLP) • Passives/packaged discretes on top of board (SMT) • Target: phones, Bluetooth, GPS, TV tuner • Joint development of Casio and CMK \*\*Passive Devices\*\* \*\*Passive Devic

### **Conclusions**

### **Market Demands:**

- Systems Integration with increasing functionality

- Speed of design (Time to Market)

- Flexibility

- Reuse

- Cost, Cost, Cost

Are necessitating a revolution in packaging and assembly technologies

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc.

All other product or service names are the property of their respective owners. © Freescale Semiconductor, Inc. 2007.

\*freescale