## ARCHIVE 2007

## SOCKET ANALYSIS AND CHARACTERIZATION METHODS

#### "Revolutionizing High-Speed Socket Test"

Michael de Bie Exotest Boris Coto, Rafiq Hussain Advanced Micro Devices

#### "Understanding Impact of Burn-in Sockets on Fragile Semiconductor Packages Using Finite Element Analysis"

Prasanth Ambady, Keith Crowe, Hide Furukawa Sensata Technologies

#### "Contact Resistance is Sexy Again"

Tim Swettlen, Morten Jensen Intel Corporation

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2007 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

| Got Enough Bandwidth?                                                                                                                     |                        |               |                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------|-----------------------|--|--|--|

|                                                                                                                                           | Standard               | Max Data Rate | Bandwidth<br>Required |  |  |  |

|                                                                                                                                           | DDR2-533               | 1.066Gbps     | 2.132GHz              |  |  |  |

|                                                                                                                                           |                        | 1.6Gbps       | 3.2GHz                |  |  |  |

|                                                                                                                                           | CHyperTransport (2.0)  | 2.8Gbps       | 5.6GHz                |  |  |  |

|                                                                                                                                           | C HyperTransport (3.0) | 5.2Gbps       | 10.4GHz               |  |  |  |

|                                                                                                                                           | Rapid <sup>I</sup> O.  | 3.125Gbps     | 6.25GHz               |  |  |  |

| Bandwidth is Important     Allows sufficient headroom for 3 <sup>rd</sup> and 4 <sup>th</sup> harmonics     Reduces path impact on jitter |                        |               |                       |  |  |  |

Socket Analysis And Characterization Methods

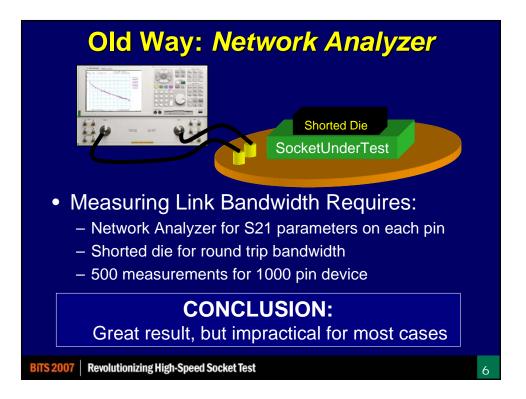

## Old Way: Opens & Shorts

- Test for Open and Short conditions on each pin

Typical DC measurements of voltage and current

- Great for basic wiring and gross errors

- Will not detect Bandwidth or impedance problems

### CONCLUSION:

Informative for gross errors, but won't catch other more critical errors

BITS 2007 Revolutionizing High-Speed Socket Test

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

11

Socket Analysis And Characterization Methods

## Old Way: TDR

- Measure line length of each pin

- Requires sampling oscilloscope and high bandwidth pulse generator

- Determine length of each trace, including socket

- Compare skew results to known good setup

- Measure each high speed signal

### **Conclusion:**

TDR can find opens and shorts, but not effective for high bandwidth applications

BITS 2007 Revolutionizing High-Speed Socket Test

# <section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item><table-row><table-row></table-row></table-row>

Socket Analysis And Characterization Methods

| <b>Risks of Current Methods</b>             |                          |  |  |  |  |

|---------------------------------------------|--------------------------|--|--|--|--|

| Open/Short Socket<br>Tester                 | Not enough test coverage |  |  |  |  |

| Network Analyzer                            | Too time consuming       |  |  |  |  |

| Oscilloscope                                | Too time consuming       |  |  |  |  |

| TDR                                         | Too time consuming       |  |  |  |  |

| Software                                    | Low pin coverage         |  |  |  |  |

| <b>Conclusion:</b> Time to shift paradigms! |                          |  |  |  |  |

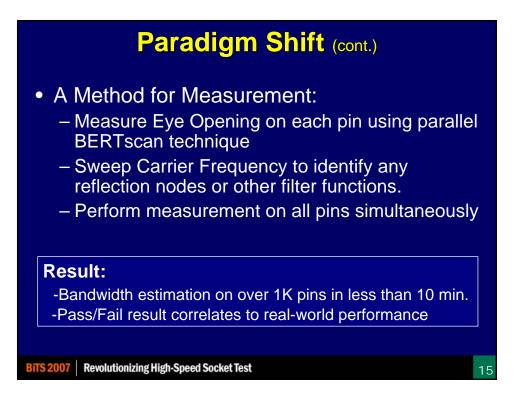

| Paradigm Shift                                                                                                                                                                                                                                                                                                  |   |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| <ul> <li>What is needed:         <ul> <li>Need to test as much as 500 pins for bandwidth</li> <li>Need to test beyond 800MHz Bandwidth</li> <li>Need to test reliability of socket in the development phase before production release</li> </ul> </li> </ul>                                                    |   |  |  |

| <ul> <li>Why?</li> <li>Sockets begin to lose bandwidth over time from repetitive insertions and environmental breakdown</li> <li>Lower bandwidth signal paths will reduce yield</li> <li>Remove guess work from determining a failed socket in production</li> <li>Reduce cost in socket development</li> </ul> |   |  |  |

| BITS 2007 Revolutionizing High-Speed Socket Test                                                                                                                                                                                                                                                                | 4 |  |  |

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

# <section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

## Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis

Burn-in & Test Socket Workshop March 11-14, 2007

> Prasanth Ambady Keith Crowe Hide Furukawa

Sensata Technologies Attleboro, MA

**REV 1.2**

<section-header><list-item><list-item><list-item><list-item>

Socket Analysis And Characterization Methods

# <section-header><section-header><text><image><image>

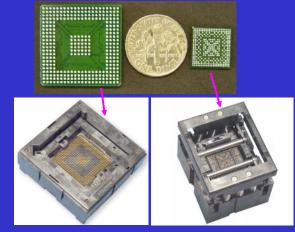

## BURN-IN CHALLENGES - SHRINKING SILICON AND PACKAGES

3

300~350 I/O, 1.00mm pitch BGA package

BiTS Workshop 2007, March 11-14

300~350 I/O, 0.50mm pitch BGA package

Packaging Trends:

•Extremely small and thin packages.

•High I/O count bumped and LGA.

0.65mm pitch and below.

•Bare die and POP style packages.

•Soft mold compound.

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

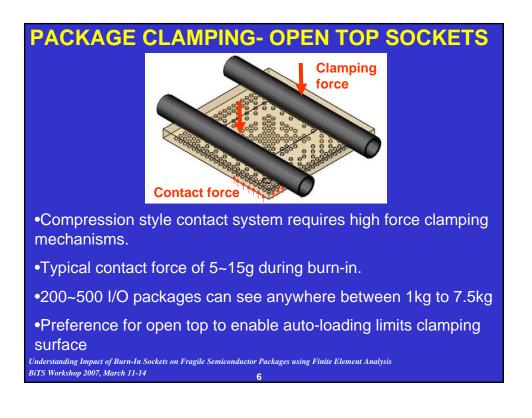

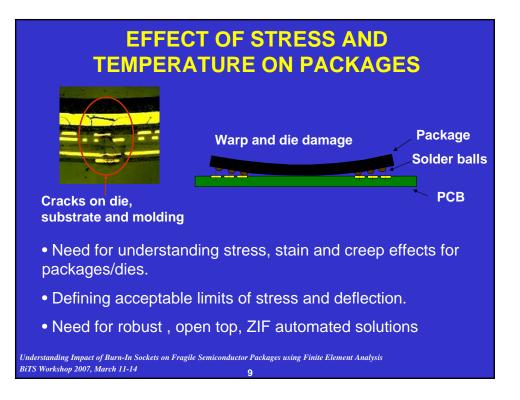

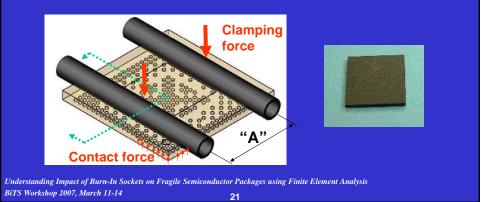

#### **UNDESIRABLE EFFECTS OF BURN-IN**

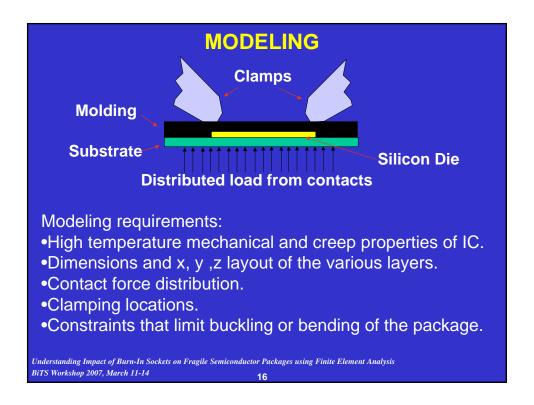

•Burn-in is an elevated temperature, long duration process in which the package is undesirably stressed by the loadings of the clamps and large number of electrical contacts.

• These loadings can cause distortion of the package and stress the circuitry on silicon.

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14 7

#### UNDESIRABLE EFFECTS OF BURN-IN

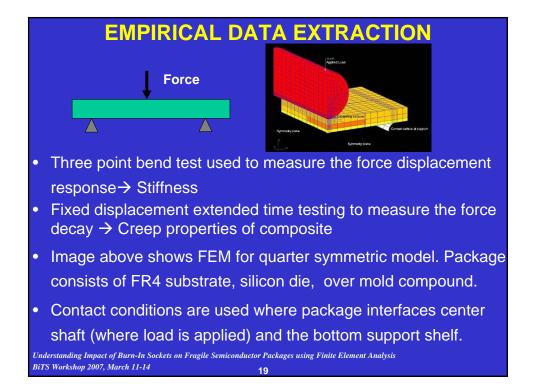

•The extended duration of these conditions can cause continual deformation (creep) of the softer materials in the package like PCB, over mold compound etc., leading to possibly significant permanent change of shape of the package even when the high temperature and forces are removed.

• This condition can render the package useless.

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

# <section-header><section-header><text><figure><text>

Socket Analysis And Characterization Methods

# <section-header><list-item><list-item><list-item>

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

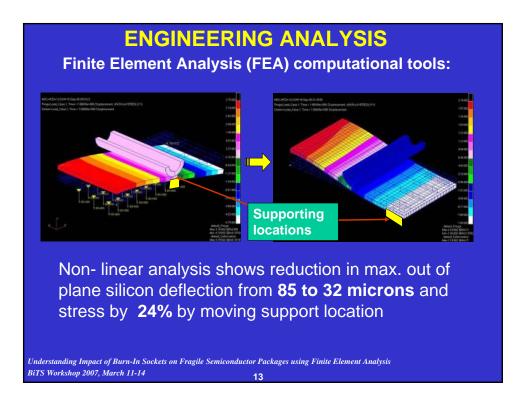

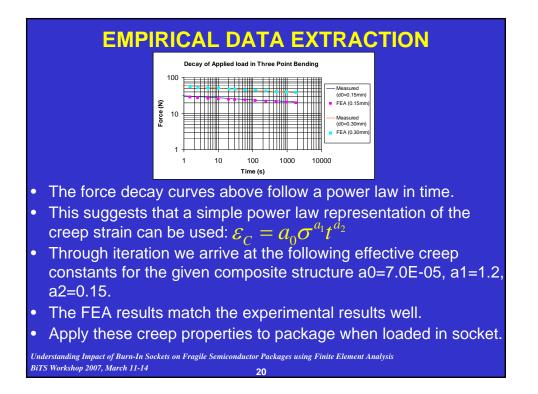

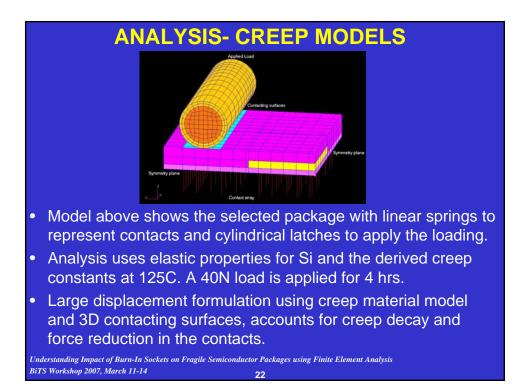

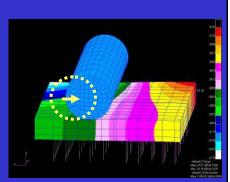

#### **ANALYSIS- CREEP MODELS**

Advanced features of our modeling and analysis :

- •3D Contacting surfaces

- •Creep material model

- •Non linear large displacement analysis

- •Variable force contacts

- •Computational and empirical properties extraction

Socket Analysis And Characterization Methods

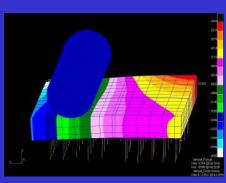

#### **ANALYSIS- CREEP MODELS**

Original design showed 90 micron out of plane permanent deflection

- Image to the left shows deformation of package over four hours of loading followed by unloading to give permanent deformation.

- FEA results of 90 um permanent deformation (creep) compared well with measured average of 96 um.

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14 23

#### **ANALYSIS- CREEP MODELS**

- To reduce the deflection, the latches were moved 0.65mm inwards as shown on the image to the right.

- Moving the latches inward by only 0.65mm shows a large improvement on the permanent set. FEA results of 32um deflection compared well with measured average of 42um.

- FEA can make a useful prediction of the performance of the package in actual socket conditions.

Improved design showed only 32 micron out of plane permanent deflection

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14 24

**Socket Analysis And Characterization Methods**

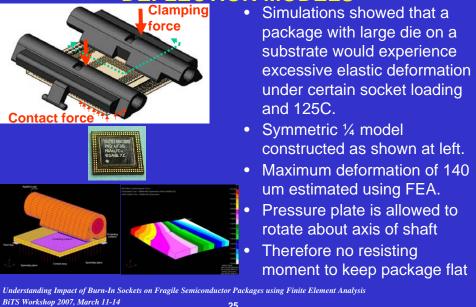

### **ANALYSIS- HIGH TEMPERATURE** DEFLECTION MODELS

## **ANALYSIS- HIGH TEMPERATURE DEFLECTION MODELS**

25

#### New latch shown on left where shaft location is moved inboard with a corresponding inward contact point.

- Total package out-of-plane deformation reduced to 60 um concentrated toward edge. Die located in the center saw a 8um deflection.

- The shaft location is the key factor.

60 micron out of plane deflection concentrated towards edges

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14 26

Socket Analysis And Characterization Methods

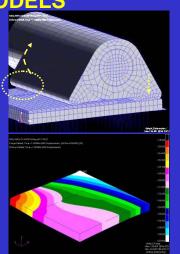

### ANALYSIS- HIGH TEMPERATURE DEFLECTION MODELS

- On the right, latch was modified to add a "foot" toward the package edge.

- Out-of-plane deformation reduced to 55 um, However die region deflection increased to 16um.

- Force applied by "foot" creates moment and causes additional rotation of latch → less force on die and more bending in that zone.

55 micron out of plane deflection more distributed on package.

Understanding Impact of Burn-In Sockets on Fragile Semiconductor Packages using Finite Element Analysis BiTS Workshop 2007, March 11-14 27

Socket Analysis And Characterization Methods

| Agenda                                        | 2 |

|-----------------------------------------------|---|

| • Impact                                      |   |

| <ul> <li>Trends and definitions</li> </ul>    |   |

| <ul> <li>Beyond the theory</li> </ul>         |   |

| <ul> <li>Measurement setup</li> </ul>         |   |

| – System fundamentals                         |   |

| <ul> <li>Required Support hardware</li> </ul> |   |

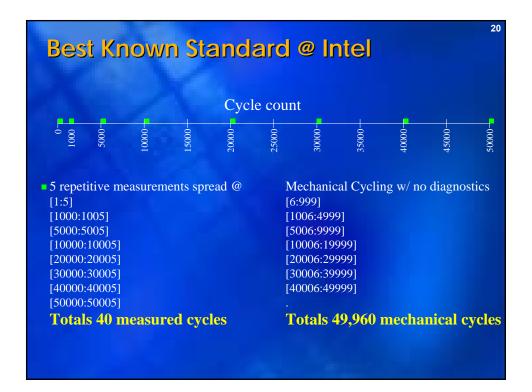

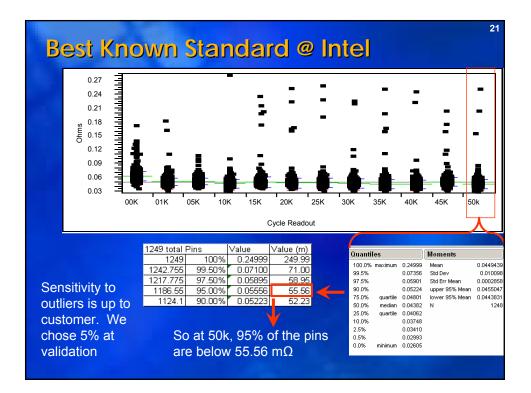

| <ul> <li>Intel's Best Known Method</li> </ul> |   |

| Summary                                       |   |

|                                               |   |

|                                               |   |

|                                               |   |

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

| Beyond theory, practical concerns |                                                                       |                                                                    |  |  |  |

|-----------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|--|--|--|

|                                   | Life Cycling a socket                                                 | Fleet of sockets                                                   |  |  |  |

| End usage condition               | Each socket "sees" 25-75k<br><u>unique</u> pristine packaged<br>parts | Product requires 10 –<br>2000 sockets to<br>support total volume   |  |  |  |

| Lab<br>validation<br>concern      | 25-75k unique package simulators?                                     | Cost & Time of<br>measuring 10 – 2000<br>sockets                   |  |  |  |

| Simple solution                   | Reuse device simulators                                               | small sample of<br>sockets, but tight limits<br>& every pin tested |  |  |  |

| Noise<br>factor                   | Life of device simulator<br>Topology of simulator                     | One outlier pin<br>Stability of supply<br>Pin lot-to-lot variation |  |  |  |

Socket Analysis And Characterization Methods

17

Socket Analysis And Characterization Methods

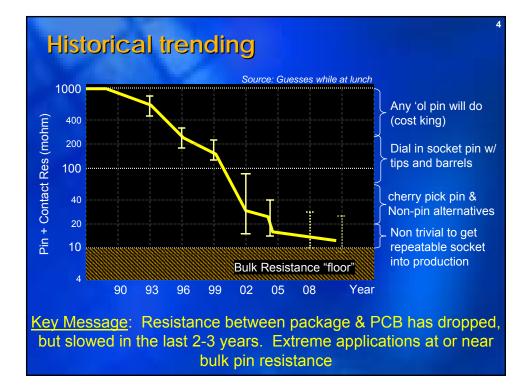

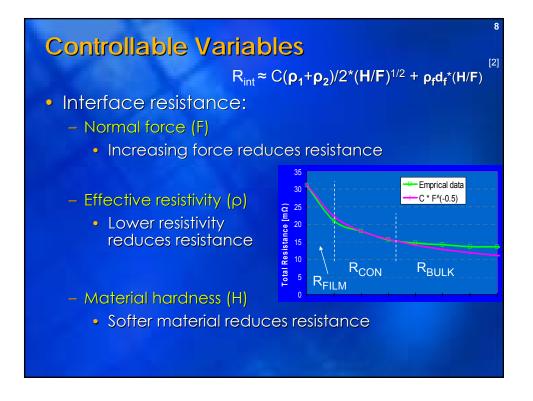

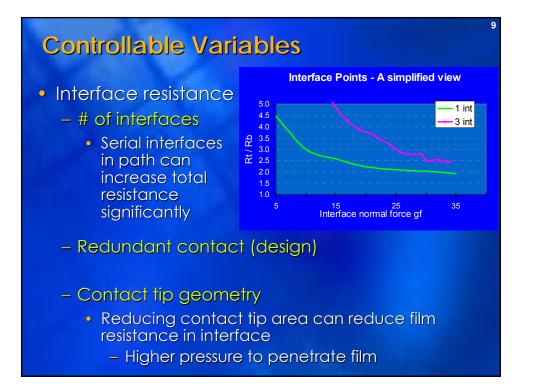

## Key takeaways so far

- Dialing in Contact Resistance on a high volume platform is a multi-million dollar variable

- Today's contact resistance targets require crisp definitions between the user and supplier

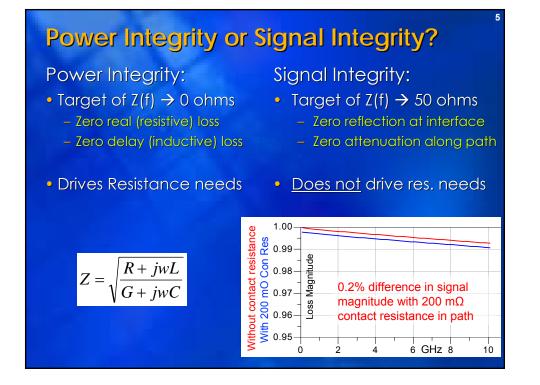

- Contact Resistance is predominantly a Power Integrity impact, not a Signal Integrity one

- There are few fundamental knobs to turn in the pursuit of optimized total resistance performance.

- Largest gain seemingly w/ interface resistance

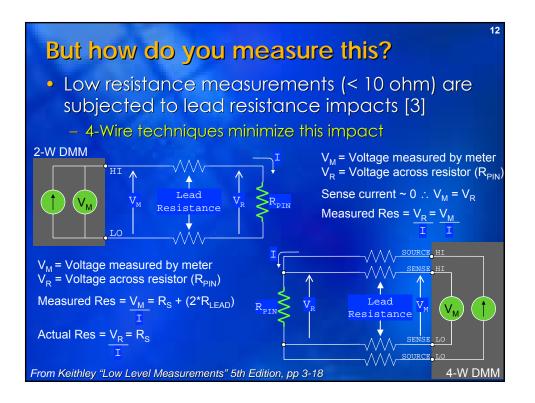

- 4 wire techniques must be used

- Mimicking end us conditions requires care in the selection of the device simulator and cycling

Socket Analysis And Characterization Methods

Socket Analysis And Characterization Methods

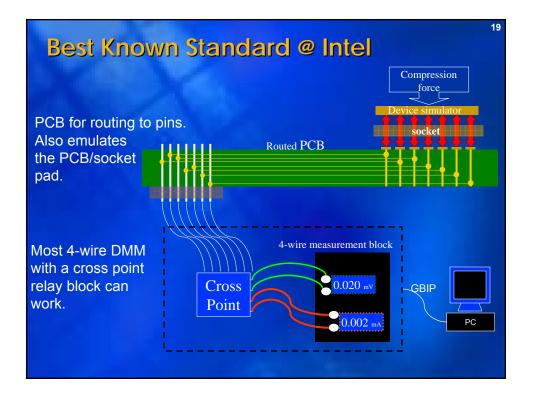

| 22<br>Best Known Standard @ Intel                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Positives <ul> <li>Simple in theory</li> <li>Most of the system is off the shelf hardware</li> <li>Effort to prove it matches end use conditions <ul> <li>Still more to go</li> </ul> </li> <li>Open to scrutiny</li> </ul></li></ul>                        |

| <ul> <li>Negatives</li> <li>Time from concept to data too long</li> <li>requires hardware to wrap around socket to test</li> <li>PCB, device simulator, compression force</li> <li>Currently no automation or standardization of cycling piece of the flow</li> </ul> |

23

24

Socket Analysis And Characterization Methods

## Where do we go from here

- Intel will share the following documents

- 1. Gage R&R DOE steps

- Used to help gather a metrology system accuracy

- 2. Reference design for resistance testing

- May choose to match Intel and become qualified

- 3. Reference metrology system details

- 4. Reference device simulators and plating recipes

- 5. Step by step validation testing

Key message, we are not contact physic experts nor do we wish to be. Our motivation is to make supplier results more meaningful so we can rapidly assess the fit of technologies to our needs

### Summary

- Contact Resistance is a widely used metric for sizing up, monitoring and validating a contact

- Today's requirements require crisp terminology and metrology between user and supplier

- We are not experts, but we have studied and will share our Best Known Methods with the goal to narrow future definitions and measurement methods

Socket Analysis And Characterization Methods

### References

- [1] Swettlen, Grossman, Berube "Qualifying a supplier, what one customer does", BITS Workshop March 2005

- [2] Slade, Paul G. "*Electrical Contacts : Principles and Applications*", New York: Cutler-Hammer, 1999

- [3] Keithley "Low Level Measurements" 5<sup>th</sup> Edition

- [4] Dunnett, C.W. (1955), "A multiple comparison procedure for comparing several treatments with a control" Journal of the American Statistical Association, 50, 1096–1121.

#### Paper #3

26