2007

#### **Session 1**

#### **ARCHIVE 2007**

#### **DESIGNING FOR SOCKET ELECTRICAL INTEGRITY**

#### "Determining Inductance In Contactors"

Ryan Satrom

Everett Charles Technologies STG

"Evaluation of a New Low Inductance Socket Technology - For High Speed Memory Device Testing"

Joachim Moerbt Advantest (Europe) GmbH

"Socket Life Cycle RF Testing"

**Gert Hohenwarter**GateWave Northern, Inc.

#### **COPYRIGHT NOTICE**

The papers in this publication comprise the proceedings of the 2007 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

All photographs in this archive are copyrighted by BiTS Workshop LLC. The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Designing For Socket Electrical Integrity

#### Introduction

- Inductance

- Critical to contactor performance

- Often interpreted incorrectly.

- Industry specs

- Good for relative comparisons between probes

- Not helpful when modeling and determining inductance through contactor

- Must increase our understanding to improve our models and better predict performance

Designing For Socket Electrical Integrity

# The Problem • Loop inductance does not change depending on the type of signal passing through the network • Therefore, these two inductance definitions cannot both be completely accurate. • Must develop an understanding that doesn't break down, regardless of application • Must be consistent with electromagnetic theory

Designing For Socket Electrical Integrity

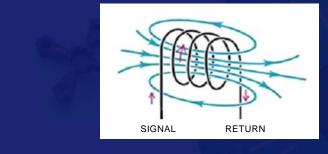

**Principles of Inductance**

- Inductance is the quantity of magnetic field lines per amp of current

- Magnetic field lines encircle all currentcarrying conductors

- Current only flows in a loop. Likewise, inductance can only be measured in a loop

- Self-inductance and mutual-inductance are strictly mathematical concepts that cannot be explicitly measured.

##

#### **Session**

Designing For Socket Electrical Integrity

#### **Principles of Inductance**

• Equation for loop inductance:

$L_{LOOP} = L_{SIG} + L_{RTN} - 2 \times L_{MUTUAL}$

- $L_{SIG,} L_{RTN}$ : Self-Inductance of signal path, return path

- L<sub>MUTUAL</sub>: Mutual Inductance between signal path and return path

- Loop inductance, L<sub>LOOP</sub> is the only value that can actually be measured

- Self-inductance or mutual-inductance alone provides little or no value

- Loop inductance is primary concern

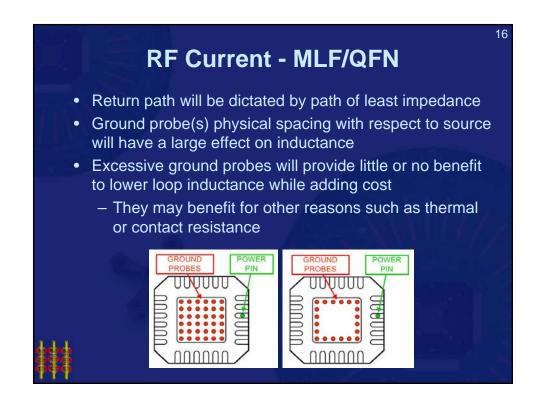

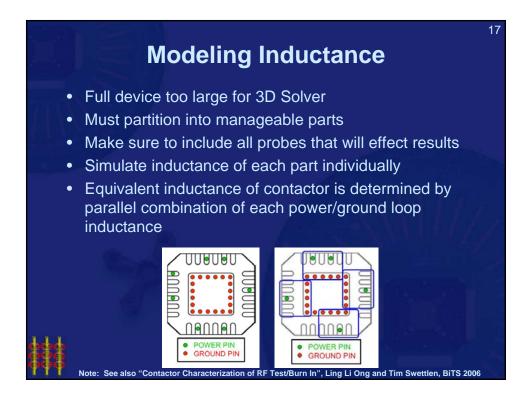

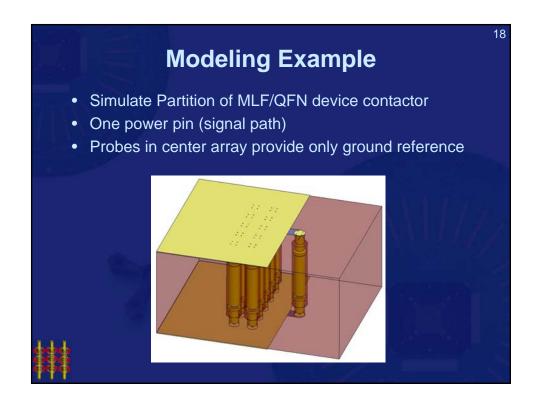

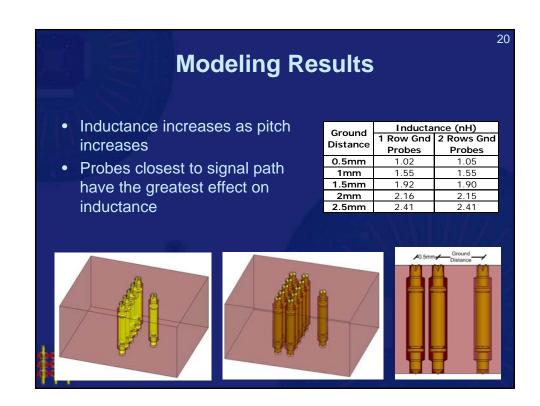

#### **Inductance in Contactors**

- Inductance in contactors is:

- Defined in a loop

- Signal-Ground loop for Signals

- Power-Ground loop for Power Delivery

- Power pins are the signal path for power delivery nets

- A function of pitch

- A function of ground proximity and number of adjacent ground pins

- The quantity and positioning of ground probes is best evaluated through 3D simulation

- Loop inductance can be optimized for the application and cost trade-offs

Designing For Socket Electrical Integrity

**Probe-Inductor Comparison**

- Reason for Comparison

- For Power Delivery, many engineers assume that a probe acts as an inductor

- Using this assumption, circuit theory is applied to derive the contactor inductance as being equal to the inductance spec divided by the number of ground probes

- Probes cannot be accurately modeled as inductors

- To determine inductance through contactor, must consider all source probes and ground probes

##

11

Designing For Socket Electrical Integrity

**Wire-Wound Inductors**

Majority of magnetic fields are contained inside windings

- Inductance is a function of number of turns, size of loop, and thickness of conductor

- Inductance value is determined by <u>loop</u> inductance from input lead (signal) to output lead (return)

12

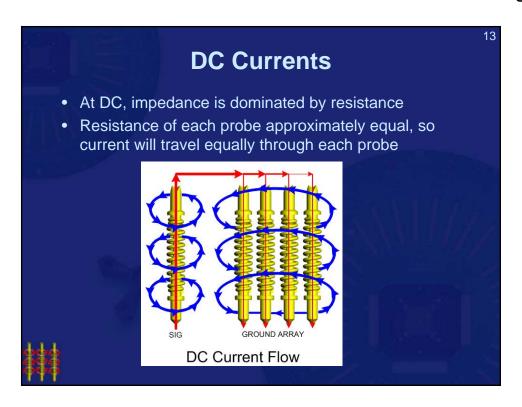

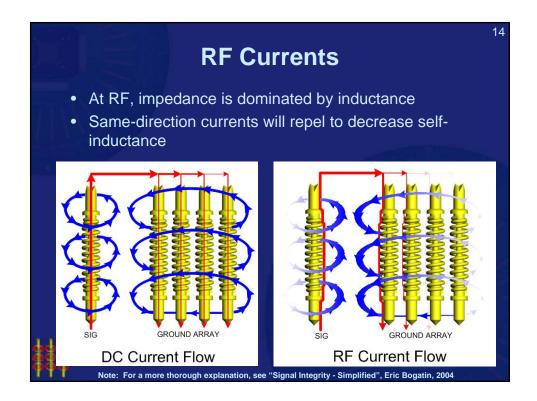

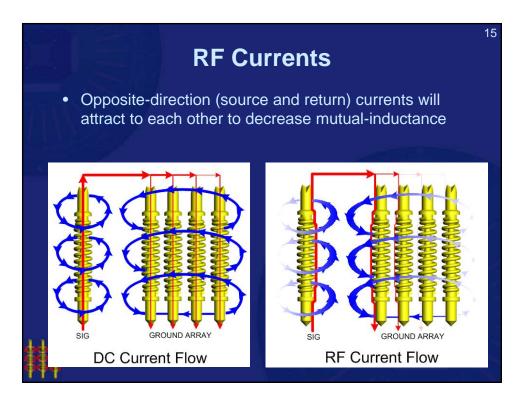

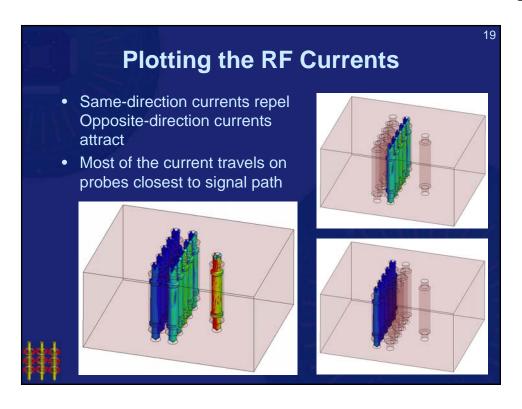

#### **Inductance in Contactors**

- Current does not flow in helical direction

- Size of loop is defined by both signal and return paths

- Individual probe does not create loop

- Increasing number of parallel probes in path will decrease inductance

- However, must understand how currents travel to understand which probes will impact inductance

- All signals and currents will travel in the path of least impedance

Designing For Socket Electrical Integrity

## Conclusion Inductance is a critical parameter that is often interpreted incorrectly. Loop inductance is best determined and optimized through 3D simulation. For Signal Integrity, path impedance can be optimized for the application through modifying loop inductance to match impedance It is important to increase our understanding in order to improve our models and better predict performance Inductance must be defined in a way that is consistent for all applications

Designing For Socket Electrical Integrity

### Evaluation of a new low inductance socket technology

- for high speed memory device testing

2007 Burn-in and Test Socket Workshop March 11 - 14, 2007

Joachim Moerbt Advantest (Europe) GmbH

#### **ADVANTEST**

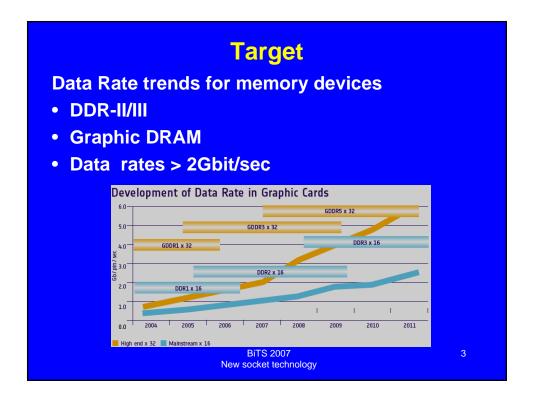

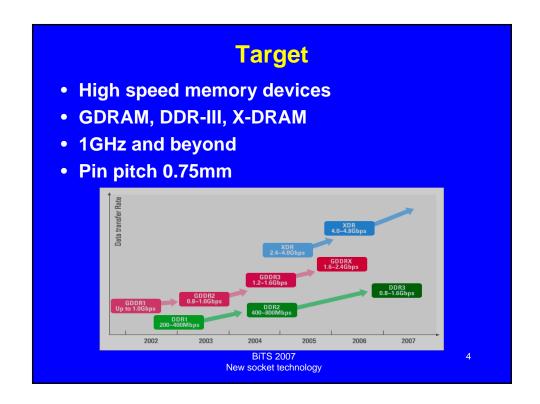

#### **Outline**

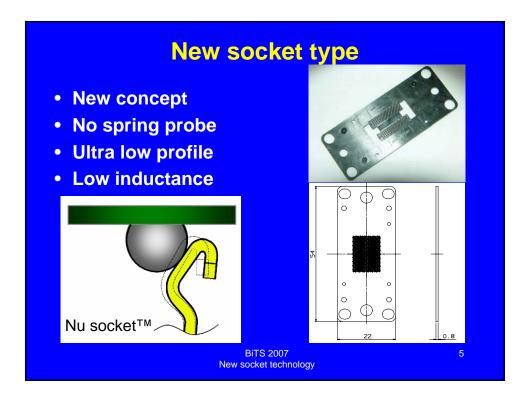

- Target of the new socket

- A new socket type

- Evaluation phases of the new socket

- Electrical parameters

- Mechanical reliability

- Device under test

- Yield evaluation

- Handling method

- Conclusion

BiTS 2007 New socket technology

Designing For Socket Electrical Integrity

#### **Evaluation Phases**

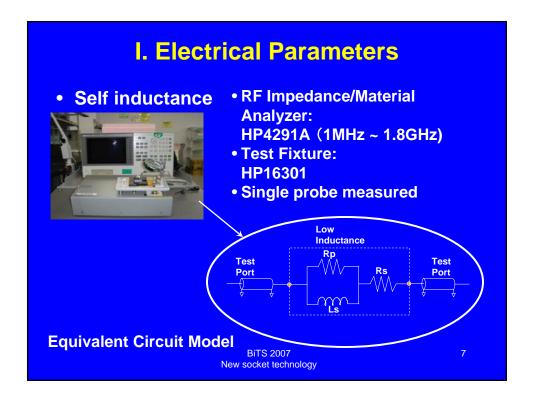

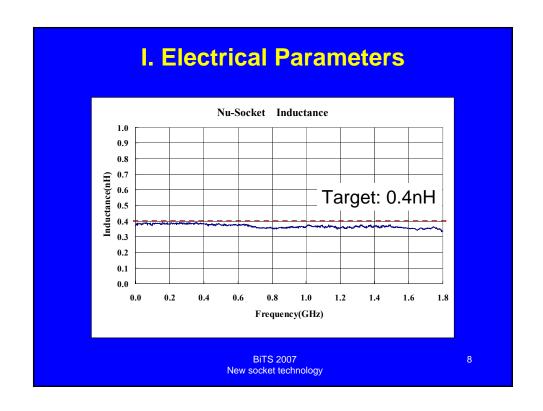

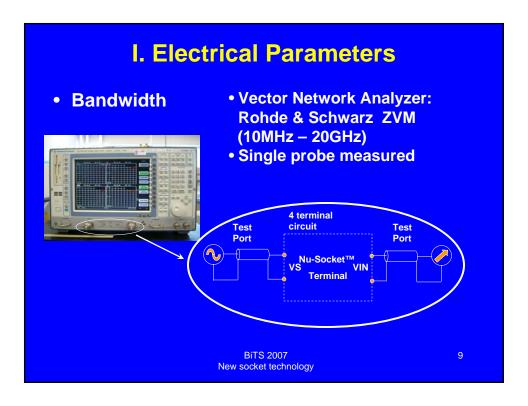

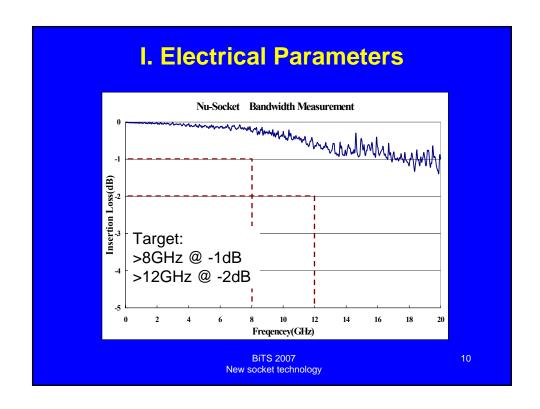

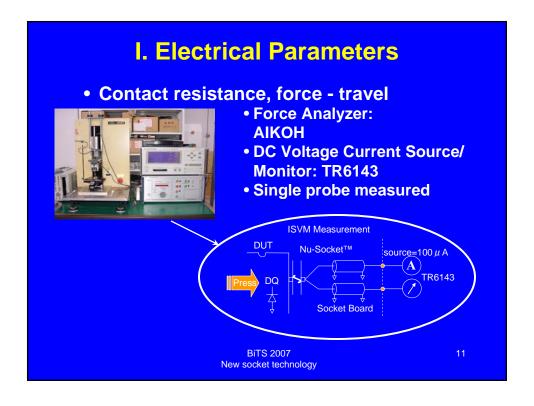

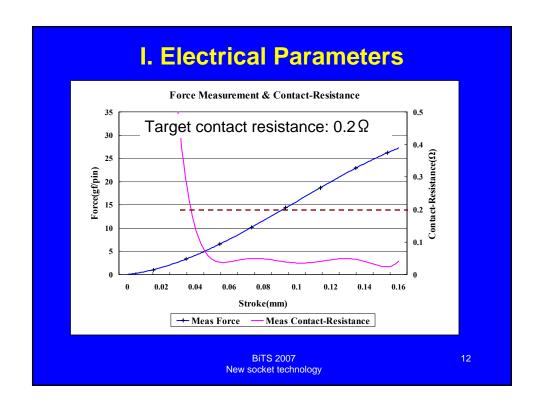

- I. Electrical parameters

- Self inductance

- Bandwidth

- Contact resistance, force travel

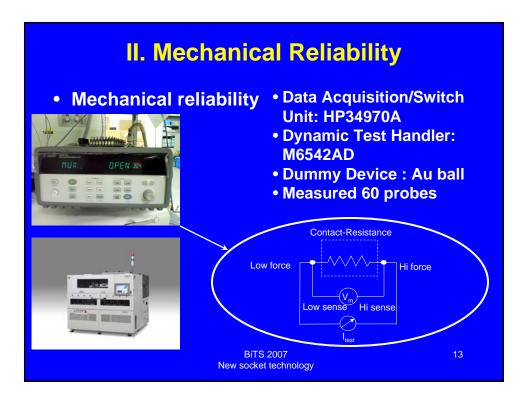

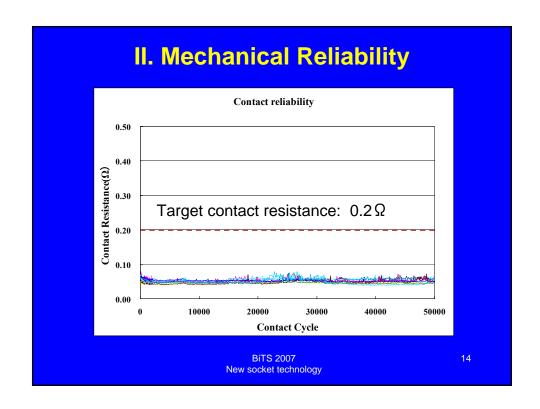

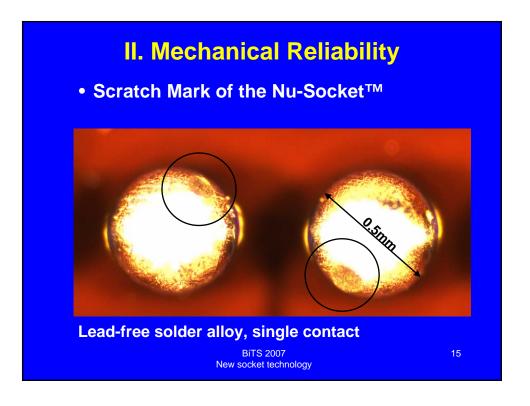

- II. Mechanical reliability

- Contact resistance versus contact cycles

- Scratch mark

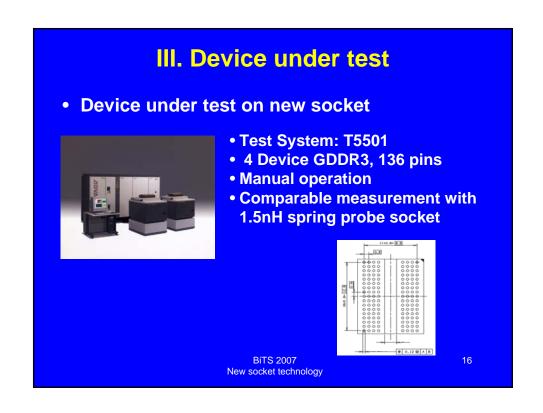

- III. Device under test on new socket

- IV. Yield evaluation under full production

- V. Handling Method

BiTS 2007 New socket technology

Designing For Socket Electrical Integrity

#### III. Device under test

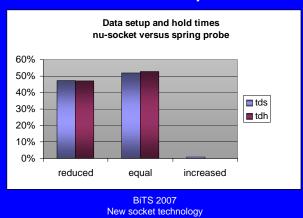

- Measurement result

- 32 data signals, cycled over the DUT position

- New socket: reduced setup and hold times

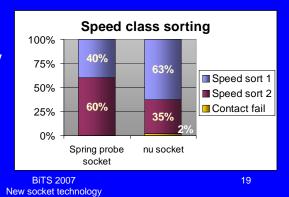

#### IV. Yield evaluation

Yield benefits under full production

- Test System: T5501

- More than 3000 devices productive GDDR3

- Parallelism: 8 DUT

- Handler operation: M6771

- Comparable measurement with 1.5nH spring probe socket

- Verification of speed sorting

BiTS 2007 New socket technology

Designing For Socket Electrical Integrity

#### IV. Yield evaluation

- Results of comparable measurement

- Higher speed class sorting increased

- Max. frequency for test increased

- Setup and hold times comparable

- Scratch marks acceptable

- Contact reliability to be improved

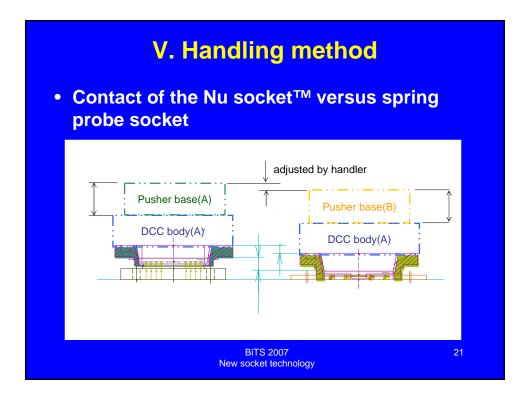

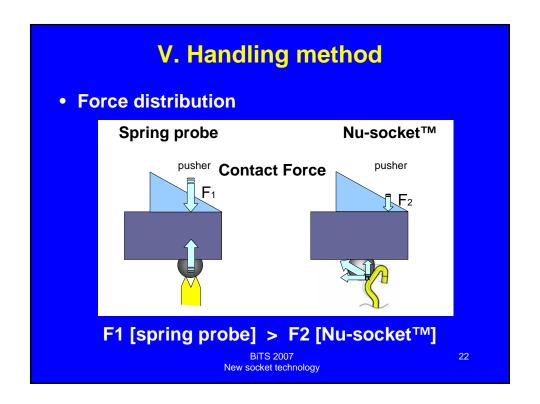

#### V. Handling method

- Changing the concept for handling

- Ultra low profile:

**Contact height reduced**

Reliable seating required for carrying:

**New carrier shape**

Compatibility for spring probe socket required

20

BiTS 2007 New socket technology

Designing For Socket Electrical Integrity

#### Conclusion

- Very good electrical parameters

- Long term reliability acceptable for production – to be improved after field experiences

- Long term production evaluation ongoing

- Contact reliability improved

- Reliable handling solution available

- Yield increase and improved speed sorting can be expected

BiTS 2007 New socket technology

#### **Session**

Designing For Socket Electrical Integrity

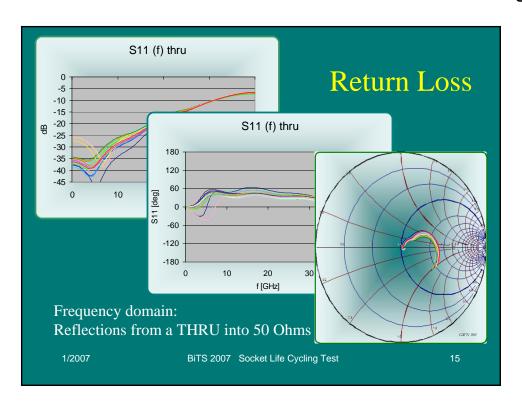

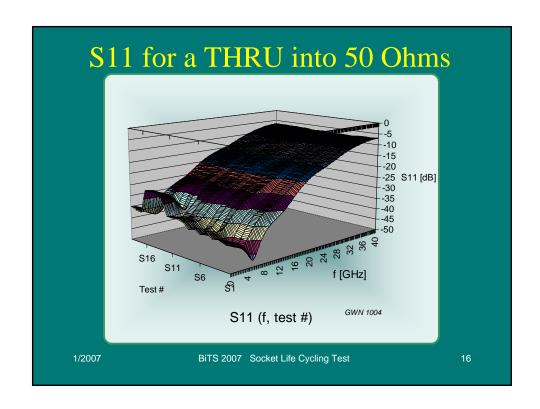

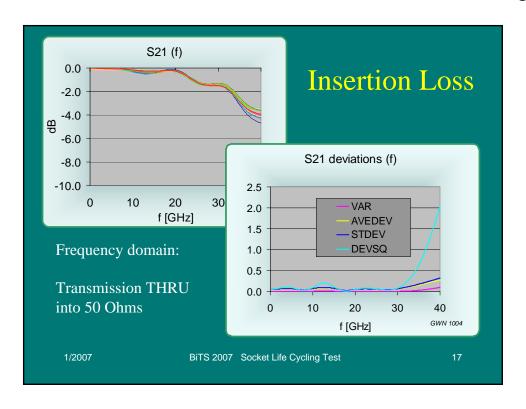

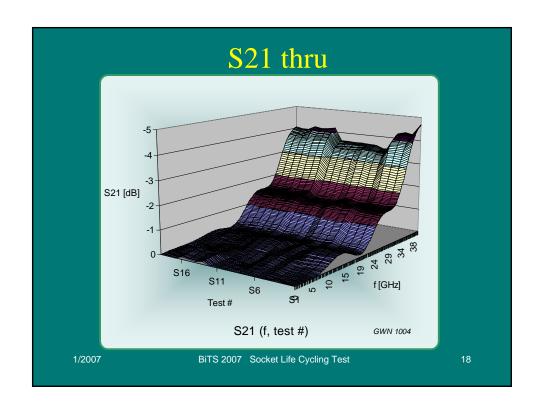

#### Socket Life Cycle RF Testing

2007 Burn-in and Test Socket Workshop

March 12 - 15, 2006

Gert Hohenwarter GateWave Northern, Inc. www.gatewave.com

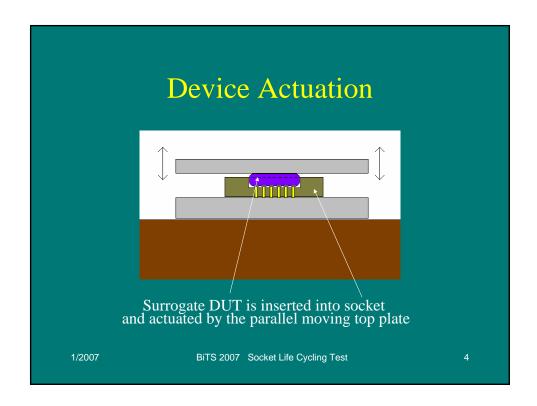

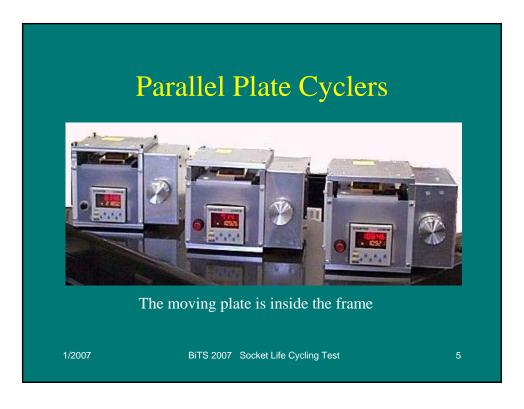

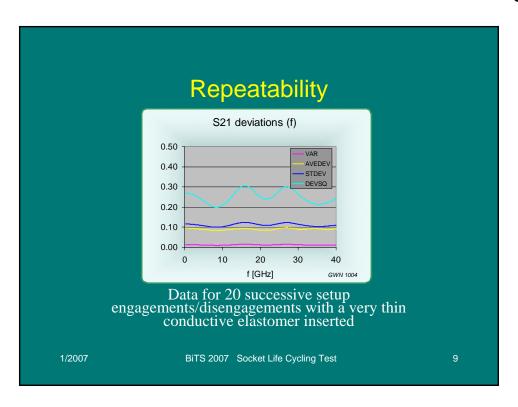

### A challenging test project was initiated by Analog Devices.....

- Determine variations in RF performance throughout a test regimen of 1 million cycles

- Test a significant number of sockets

- Sockets provided by manufacturers

- Data provided to manufacturers, then to AD

1/2007

BiTS 2007 Socket Life Cycling Test

| Test Protocol                                          | Test #   | Cycle #         |

|--------------------------------------------------------|----------|-----------------|

|                                                        | 1        | 0               |

|                                                        | 2        | 0               |

| <ul> <li>Perform initial characterization</li> </ul>   | 3        | 0               |

| • Feriorii ilillai GilaraGerizalion                    | 4        | 0               |

| Dorform A ougocopius magazuramanta                     | 5        | 8192            |

| <ul> <li>Perform 4 successive measurements</li> </ul>  | 6        | 8192            |

| (DUT probe engages/disengages)                         | /        | 8192            |

| <ul> <li>Run prescribed cycle number</li> </ul>        | 8        | 8192            |

| ,                                                      | 9        | 65536           |

| (exchange of surrogates as needed)                     | 10       | 65536           |

| <ul> <li>Perform next set of 4 measurements</li> </ul> | 11<br>12 | 65536           |

|                                                        | 12       | 65536<br>262144 |

|                                                        | 13       | 262144          |

| <ul> <li>Continue sequences until 1M cycles</li> </ul> | 15       | 262144          |

| is reached                                             | 16       | 262144          |

| is reached                                             | 17       | 1048576         |

|                                                        | 18       | 1048576         |

|                                                        | 19       | 1048576         |

|                                                        | 20       | 1048576         |

| 1/2007 BiTS 2007 Socket Life Cycling Test              |          | 3               |

Designing For Socket Electrical Integrity

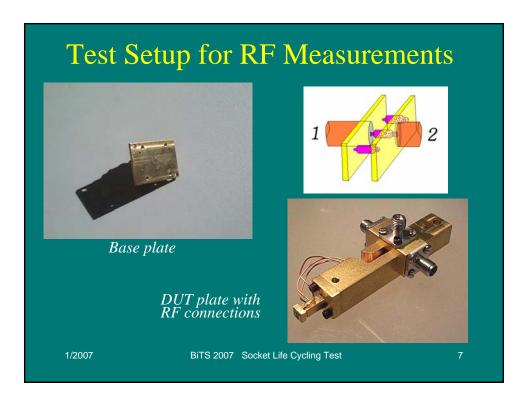

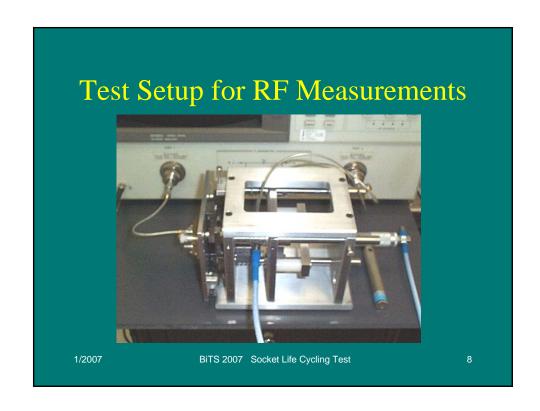

#### **Test Setup Requirements**

- Total number of RF tests expected >500

- Different types of sockets

- Robust

- Fast

- Repeatable

- Low cost / applicable to more than 1 DUT

1/2007

BiTS 2007 Socket Life Cycling Test

Designing For Socket Electrical Integrity

#### Conclusion

- A test environment for cycling tests was established

- A significant number of test sockets was evaluated

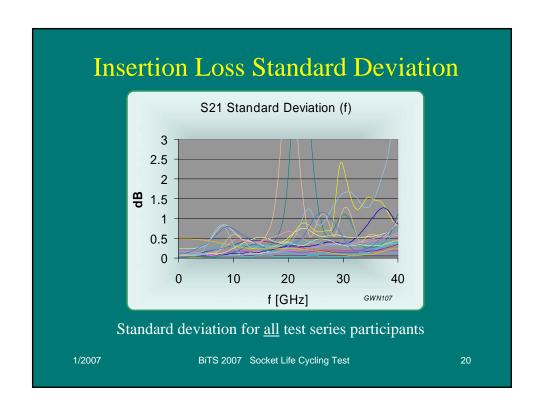

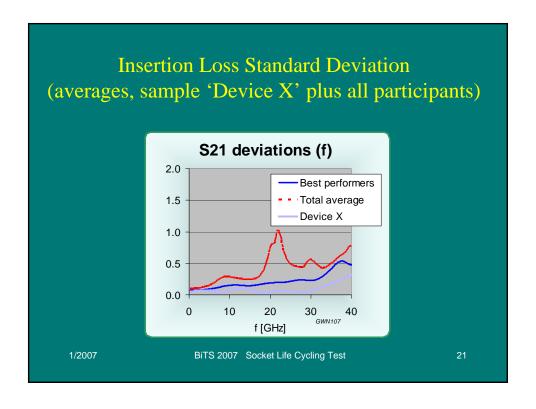

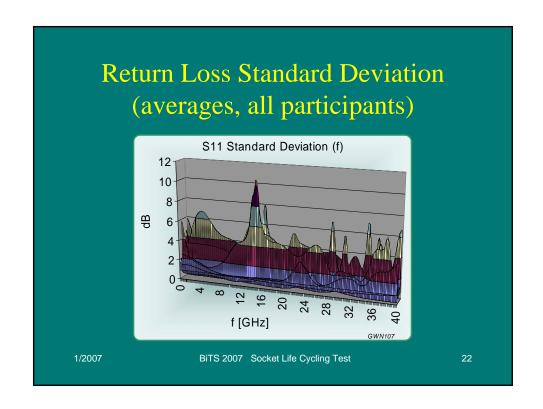

- Performance changes were highlighted via data presentation

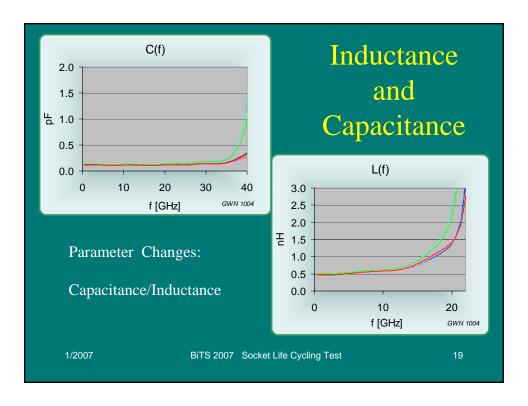

- Changes unique to RF testing were identified

- Tests are capable of pointing out weaknesses in the socket and contactor design

1/2007

BiTS 2007 Socket Life Cycling Test

Designing For Socket Electrical Integrity

#### Acknowledgements

Thank you to all customers who made this possible

Richard Liggiero Ericia Gertsch Prof. J.B.Beyer

1/2007

BiTS 2007 Socket Life Cycling Test