# A R C H I V E 2006 Session 8 Test And Burn-in Efficiency Initiatives

"Enabling High Volume Testing Of MCP Memory" Ken Karklin — Agilent Technologies

"An Alternative Test For Verifying Connectivity On High Pin Count Devices During Burn-in" Rick Larson, PE — Texas Instruments, Inc.

Bunny Gaab — Enplas Tesco, Inc.

"Minimizing Spring Probe Operational Cost Using Optimized Maintenance Techniques" Erik Orwoll — Nu Signal LLC

### **COPYRIGHT NOTICE**

• The papers in this publication comprise the proceedings of the 2006 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented , without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

• There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

• The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

Test & Burn-in Efficiency Initiatives

# Enabling High Volume Testing of MCP Memory

**Efficiency Initiatives Session**

### 2006 Burn-in and Test Socket Workshop March 12 - 15, 2006

Agilent Technologies Ken Karkli Test Cell Ir

Ken Karklin Test Cell Integration Manager, MTS

Test & Burn-in Efficiency Initiatives

# <section-header><section-header><list-item><list-item><list-item><list-item><list-item><list-item><list-item>

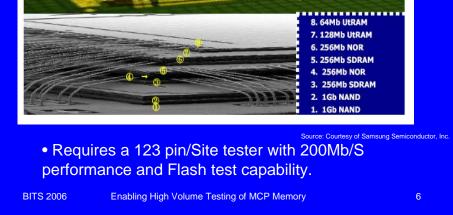

# Multiple Types of Memories in MCPs Multiplying the Complexity of the Test Problem

Test & Burn-in Efficiency Initiatives

# <section-header> One MCP focused Solution: V5500 = 4096 l/0. Matrix = x 6 resource multiplier. Effective 24,586 l/O at test plane

Enabling High Volume Testing of MCP Memory

**BITS 2006**

Paper #I

8

Test & Burn-in Efficiency Initiatives

9

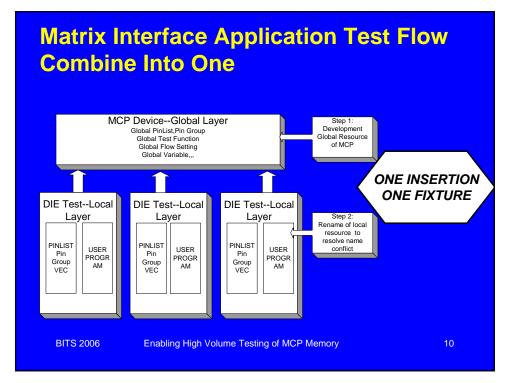

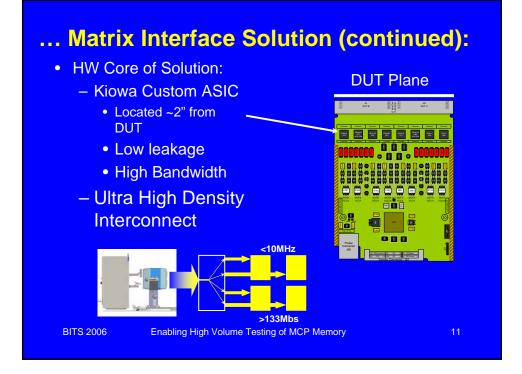

### ... Matrix Interface Solution (continued):

- Each I/O channel selectable switching to any/all of 6 DUT resource locations

- Alternatively, switch any DUT resource to one of 8 programmable voltage levels

- MCP tested in one insertion – Global test program execution

BITS 2006

Enabling High Volume Testing of MCP Memory

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

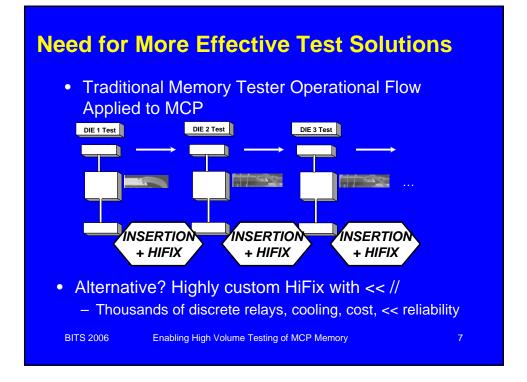

### Is This Really Different?

Haven't we been doing this with relays for years?

- How is this different than what has been done with relays?

- All channels can be switched: equivalent ~60k relays

- Universal: doesn't increase cost of each load board

- Relays don't provide high performance fan-out

- Provides ability to maintain state of switched pins

- Why not put this on the load board?

- Reliability becomes impossible

- Cost, Lead-Time

- Only manufacturable way to do in load-board/Hifix is to dramatically reduce parallelism

BITS 2006

Enabling High Volume Testing of MCP Memory

<section-header><section-header><image><list-item><list-item><list-item><list-item><list-item>

### Session 8 Test & Burn-in Efficiency

Initiatives

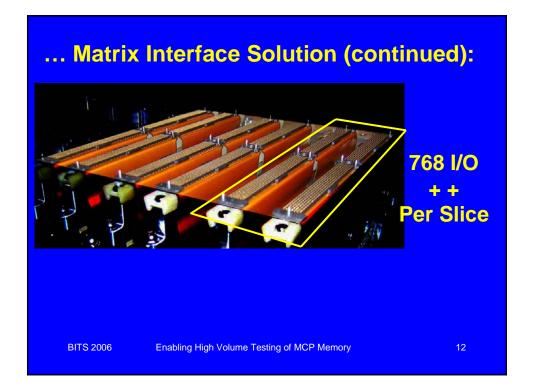

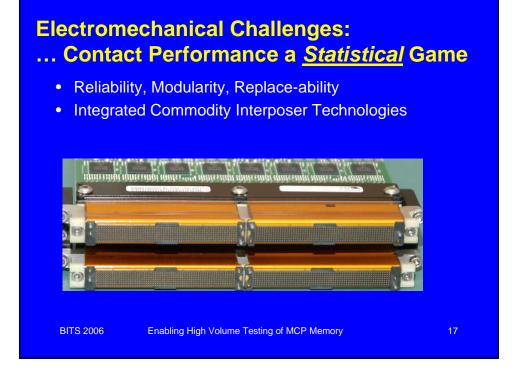

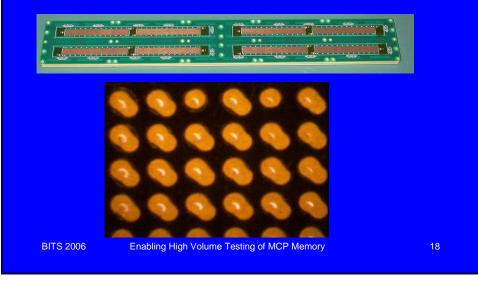

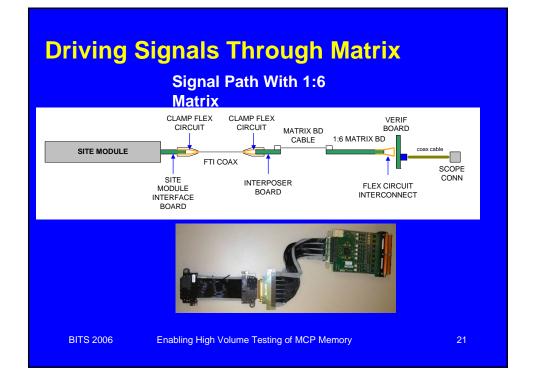

### Matrix = Massive Resources at DUT Plane ... and Big Electromechanical Challenges

- >55,552 total contacts

@ ~40gf

- 5 ton total force across minimal stroke

- Leverage 4-bar linkage w/ cam x 2 DUT attach planes

- Manually actuated simple and robust

BITS 2006

Enabling High Volume Testing of MCP Memory

<section-header><section-header><text><figure><figure><page-footer>

Test & Burn-in Efficiency Initiatives

# Matrix Socket Board Density

• Alignment challenges solved across temperatures

Test & Burn-in Efficiency Initiatives

Session 8

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

### Summary

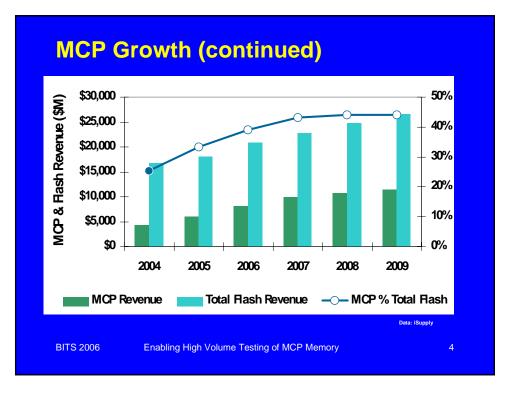

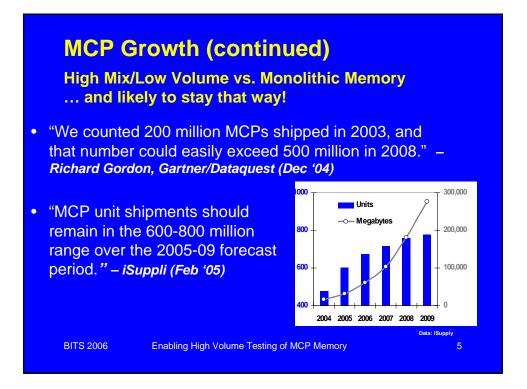

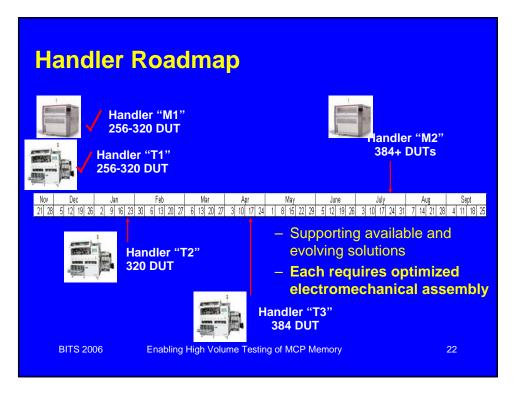

- MCP growth is substantial

- MCPs create test complexity

- The matrix MCP provides an efficient, low COT solution

- Extreme Parallelism challenges solved:

- Novel ASIC design / placement

- Electromechanical innovation

- Breakthrough interconnect technology

- Integrate to multiple handlers

- Enabling the mobile-device MCP memory explosion !

**BITS 2006**

Enabling High Volume Testing of MCP Memory

23

Test & Burn-in Efficiency Initiatives

# AN ALTERNATIVE TEST FOR VERIFYING CONNECTIVITY ON HIGH PIN COUNT DEVICES DURING BURN-IN

### 2006 Burn-in and Test Socket Workshop

Rick Larson Texas Instruments, Inc. Bunny Gaab Enplas Tesco, Inc.

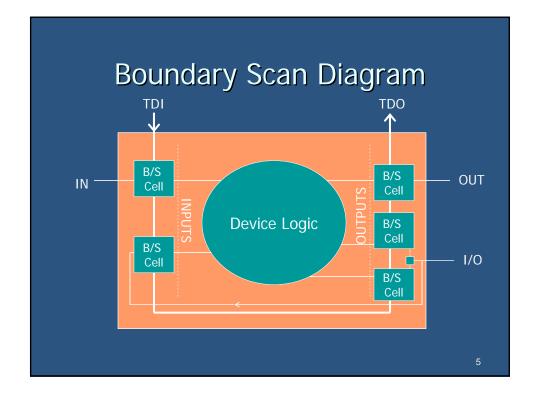

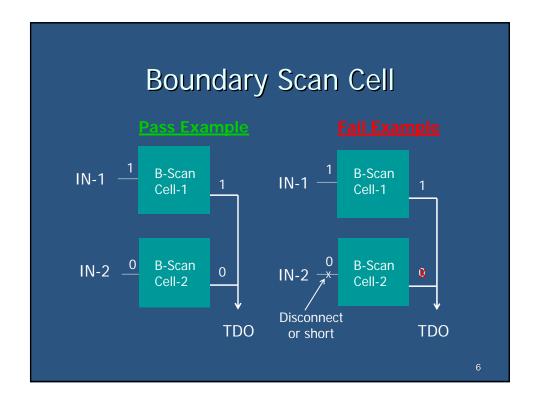

# Objective

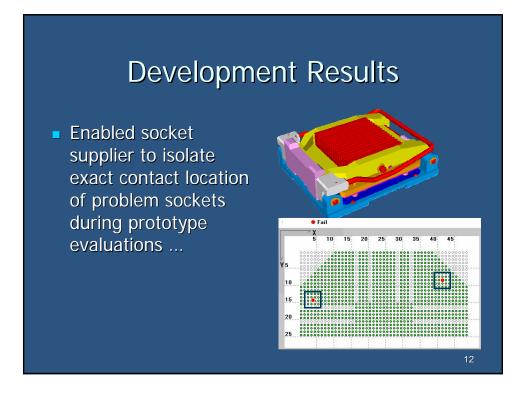

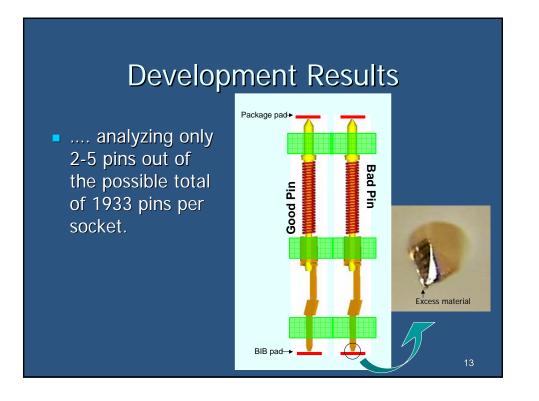

- To find a method for quickly isolating a contact related failure at a burn-in socket position for a minimal amount of cost

- To be able to verify connectivity of a highpin count DUT at burn-in temperatures

Initiatives

Test & Burn-in Efficiency Initiatives

Burn-in Efficiency

Session 8 Test & Burn-in Efficiency Initiatives

Session 8 Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

| Repair Time Savings                                                                          |                                                                  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------|--|

| <u>Old Flow</u>                                                                              | <u>New Flow (w/ b-scan test)</u>                                 |  |

| Test technician marks                                                                        | Test technician marks                                            |  |

| failing socket w/                                                                            | failing socket w/                                                |  |

| disposition tag                                                                              | disposition tag                                                  |  |

| Repair technician                                                                            | Repair technician looks                                          |  |

| narrows fail to a                                                                            | up failing pin                                                   |  |

| group of potential pins                                                                      | location(s) on database                                          |  |

| Repair technician diagnosis<br>fail with meter and/or<br>oscilliscope and<br>performs repair | Repair technician<br>confirms failing pin<br>and performs repair |  |

| Total Repair Time ~                                                                          | Total Repair Time ~                                              |  |

| 0.5hr to > 3hr                                                                               | 0.2hr to 0.5hr <sub>15</sub>                                     |  |

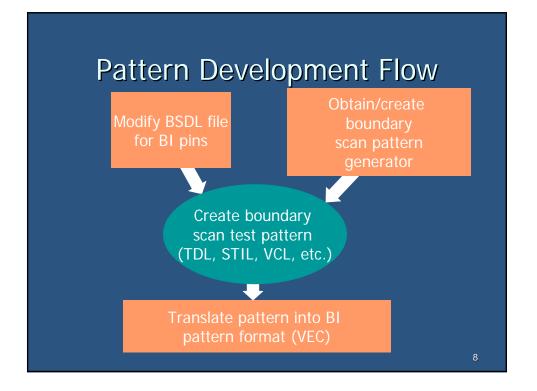

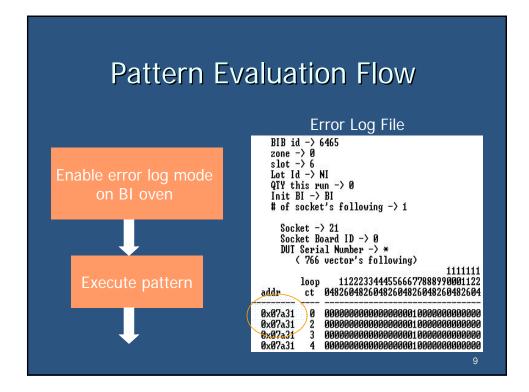

### **Boundary Scan Requirements**

- Designed into device

- Burn-in oven that can log failing output address locations to a pin channel

- Boundary Scan Description Language (BSDL) file

- Translators

- create JTAG pattern

- convert pattern to burn-in oven format

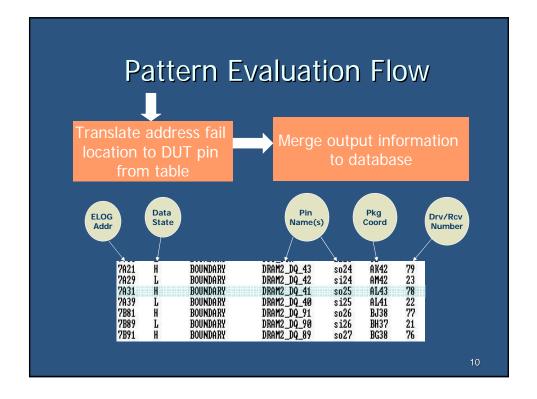

- modify error log output to device pin name & location

16

Initiatives

### Advantages

- Enables a fast method for identifying contact related problems

- Test can be performed at burn-in conditions with actual devices

- No additional equipment costs required

### Disadvantages

- Not able to verify connectivity on JTAG pins (TDO, TDI, TMS, TCK, TRST) or other pins not connected to boundary scan chain

- Initial development time to create custom pattern & translators

Session 8 Test & Burn-in Efficiency Initiatives

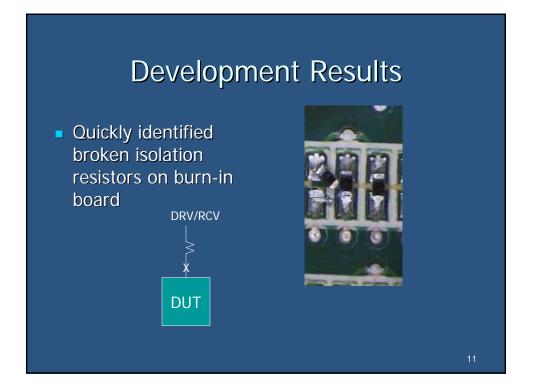

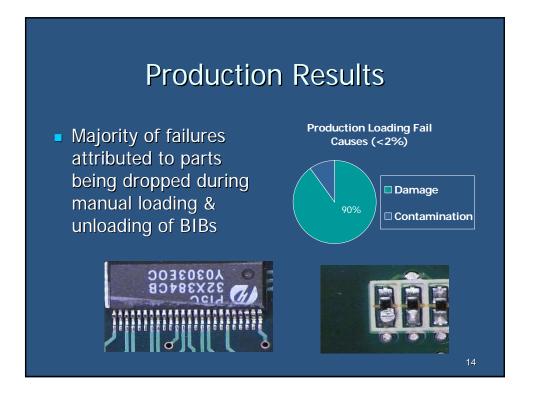

### Conclusions

- Using a boundary scan test during burn-in has been found to a valuable tool for quickly identifying contact problems during burn-in development

- Performing a boundary scan test during production checkout has enabled BIB repair times to decrease by as much as 6x

### Future Development

- Setup boundary scan test for nondriven IO pins

- Add in real-time translation and reporting of error log results during program executions

20

### Session 8 Test & Burn-in Efficiency Initiatives

# Acknowledgements

- Bunny Gaab Enplas Tesco (socket)

- Micro Control Company (burn-in oven)

- Robert Young TI (BI technician)

21

Test & Burn-in Efficiency Initiatives

# Minimizing Spring Probe Operational Cost Using Optimized Maintenance Techniques

2006 Burn-In and Test Socket Workshop March 12 - 15, 2006

Erik Orwoll - Nu Signal LLC

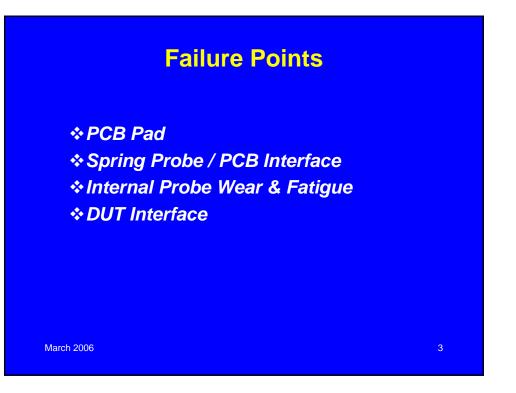

### **Discussion Points**

Where Do Probes Fail?

Failure Modes / Causes

Options To Address Failures

Production Yields

March 2006

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

9

### **Maintenance Methods Observed**

\* Mechanical Cleaning

- Abrasive Pads / Abrasive Media

- Brushing

- Adhesive (Sticky) Pads

- Chemical Contact Cleaners

(Oils result in device contamination)

- Ultrasonic

\* Air Hose / Air Blast

March 2006

Session 8 Test & Burn-in Efficiency

Initiatives

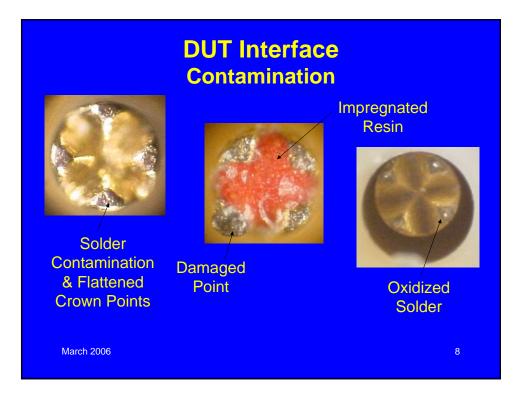

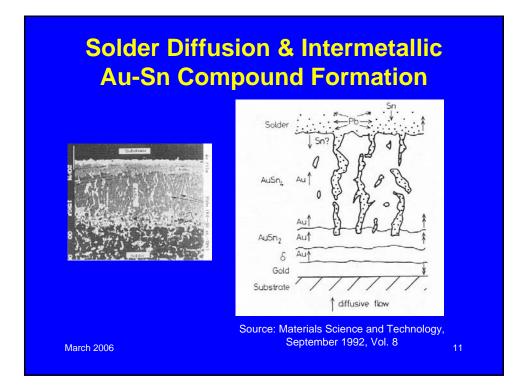

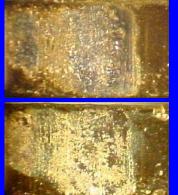

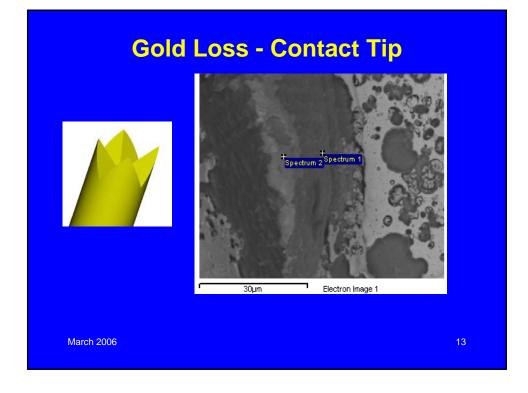

### Solder Diffusion & Intermetallic Compound Formation

Solder Contamination QFP Contact

Solder Extracted Intermetallic Compounds Exposed

Non-Conductive Crystalline Structure

March 2006

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

Test & Burn-in Efficiency Initiatives

| Maintenance Fixtures                                                                            |  |  |

|-------------------------------------------------------------------------------------------------|--|--|

|                                                                                                 |  |  |

|                                                                                                 |  |  |

| Fixture Allows Socket To Remain In Use<br>Probe Maintenance Performed Off-Line<br>March 2006 17 |  |  |