## ARCHIVE 2006 Keynote Address

### "Test And Burn-in: The World Beyond Scaling"

John Harris

Worldwide Test Engineering Manager IBM Systems & Technology Group

#### **COPYRIGHT NOTICE**

- The papers in this publication comprise the proceedings of the 2006 BiTS Workshop. They reflect the authors' opinions and are reproduced as presented, without change. Their inclusion in this publication does not constitute an endorsement by the BiTS Workshop, the sponsors, BiTS Workshop LLC, or the authors.

- There is NO copyright protection claimed by this publication or the authors. However, each presentation is the work of the authors and their respective companies: as such, it is strongly suggested that any use reflect proper acknowledgement to the appropriate source. Any questions regarding the use of any materials presented should be directed to the author/s or their companies.

- The BiTS logo and 'Burn-in & Test Socket Workshop' are trademarks of BiTS Workshop LLC.

John L. Harris

Manager, WW Test Engineering

IBM Systems and Technology Group

#### **Beyond Scaling....**

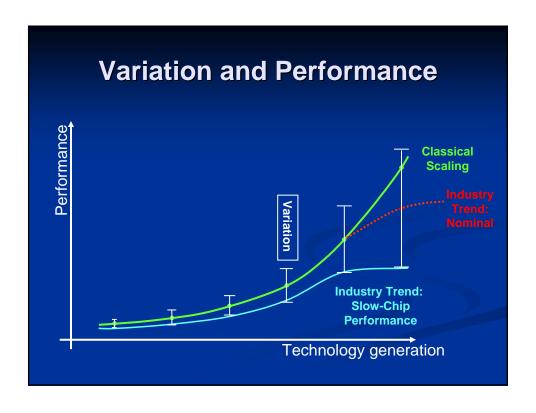

- Scaling has driven the industry for the past 40+ years

- Classical Scaling is dead....Now what?

- What does it mean to Test and Burn In?

#### Beyond Scaling does not mean...

- Chips are not going to keep getting faster

- The performance of chips is no longer going to increase dramatically

- Reducing photolithography groundrules doesn't matter

- Moore's Law is dead !!

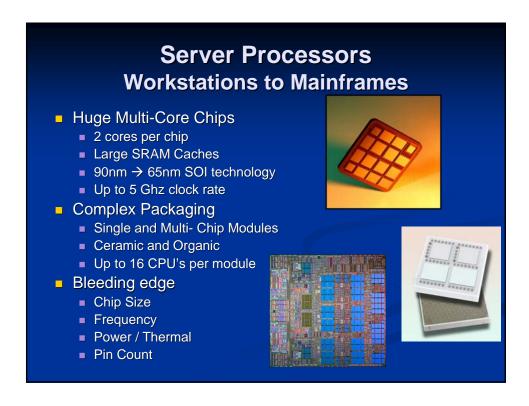

#### Beyond Scaling does mean....

Architecture and system design will be the primary forces driving performance increases...not just clock frequency

New materials and processes will drive chip performance as much or more than photolithography groundrules

- Design and process interaction is increasing and increasingly hard to model and control

- Test and packaging complexity is increasing

- Economic challenges will be greater than ever

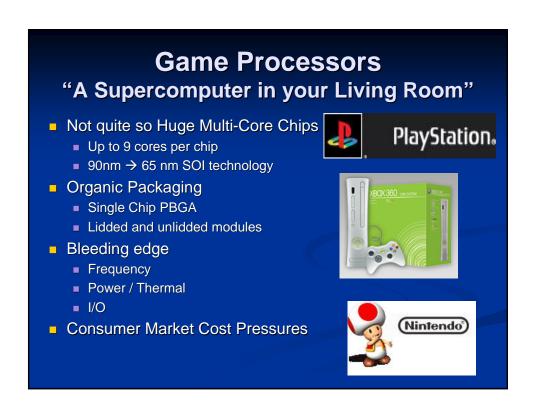

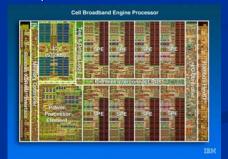

#### Cell Processor aka "Broadband Engine"

- Next Generation Power Processor for Gaming, Digital Home Entertainment, Defense, Medical Imaging and....

- 64 bit Supercomputer on a Chip

- 9 Processor Cores

- 235 mm<sup>2</sup> chip

- 42.5 mm Flip chip PBGA

- >1200 pins / 486 IO

- 3-4 Ghz Clock rate

- 512KB L2 memory

#### Meanwhile back in "Test World"...

- Test Leadership in the 21st century

- What does it mean?

- Does it matter?

- What does "Beyond Scaling" mean to Test?

- Some of the more "interesting" challenges

#### Test Leadership...what does it mean?

- Not getting in the way

- New technologies and products

- Test Cost

- Yield

- Quality

- Providing value add differentiation

- Time to Market

- Yield Learning rate

- Cost of Test

- Quality and Reliability

#### Test Leadership...does it matter?

- Can't be a technology leader without it

- Key competitive weapon

- Time to market

- Quality and reliability

- Key profitability lever

- Yield

- Yield Learning rate

- Test Cost

#### "Beyond Scaling"...some key Trends

- Yield Learning rate critical to business success

- Power / Thermal becoming a primary constraint

- Most of the Test function moving on die

- Design/process marginalities and systemic "defects" vs. random defects

- Many flavors of Good die...customization at Test

- SOC/SIP...integration of heterogeneous function

#### What does all this mean to Test?

- The Role of Test is changing

- The business criticality of Test is increasing

- The leverage points are moving away from our historical "core" of equipment and Test programs

- The complexity of Test is increasing

- Difficult to scale cost at the same rate as fab

#### **The Changing Role of Test**

- Job #1 = Sort Good from Bad

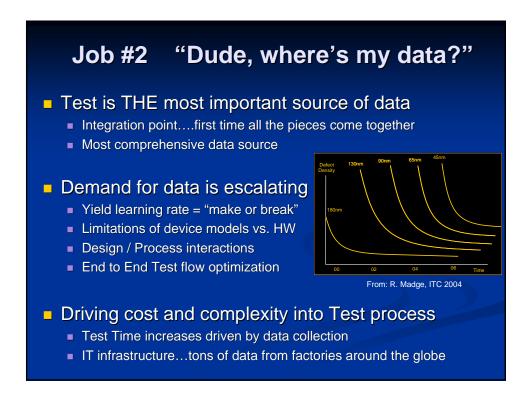

- Job #2 = Data Feedback to Design and Fab

Job #3 = Value Added ProductTransformation

#### A few other "interesting" challenges

- "Collateral damage"...the silent killer

- "The SOC Fallacy"

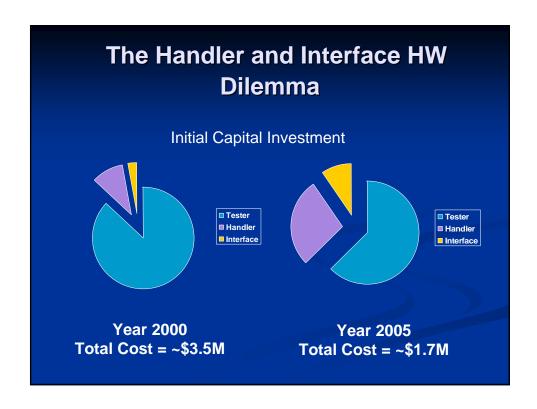

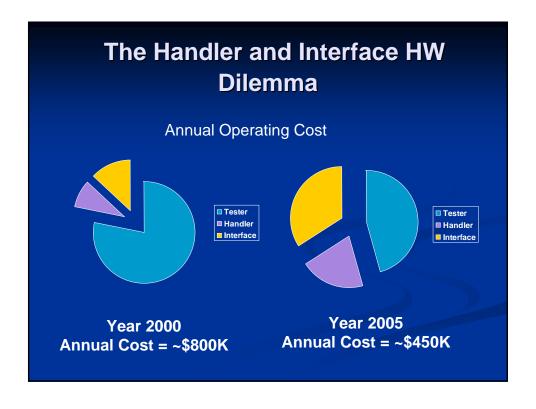

- The Handler and Interface HW Dilemma

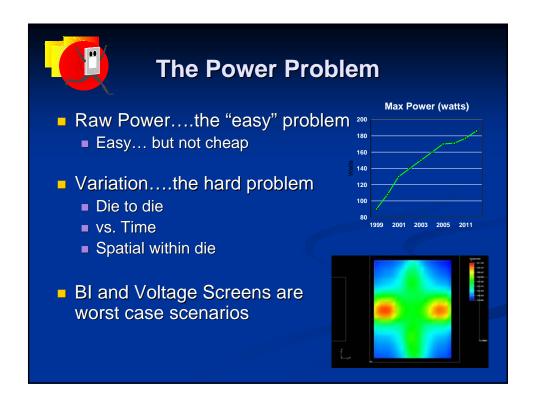

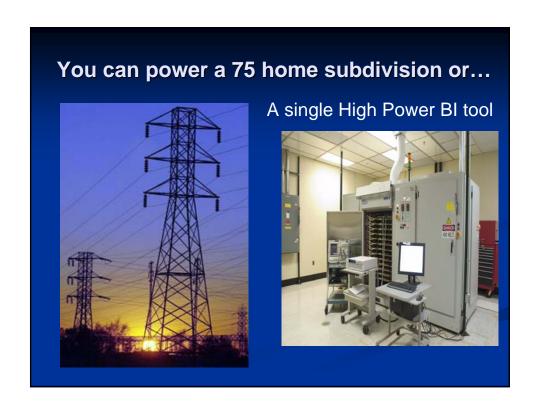

- The Power Problem

# "Collateral Damage" Test process yield loss Test equipment inaccuracies Electrical, mechanical, thermal Test process yield loss The quality vs. yield tradeoff Overtesting to guarantee DPM levels Overtesting at probe to protect package test yields Difficulty in discriminating goods from bads Differences between Test and Application conditions Reliability screens and Burn in

#### "The SOC Fallacy"

- Technically Feasible vs. Economically Rational

- The Challenge: Cost

- Heterogeneous function in a single die or package

- Divergent and often conflicting Test Methods

- SIP addresses the Die and Wafer Test cost problems

- SIP generally doesn't solve the package Test problem

- "SOC Testers" often suffer from the same fallacy as SOC die

- DFT and multiple insertions can mitigate the problem but don't solve it

- "Concurrent Test" sounds great but is very hard to implement

- KGD can help...but only if KGD and assembly are REALLY GOOD

#### In closing...

- There is a bright future ahead in Test

- There is life after Scaling...lots of it !!!

- Plenty of interesting technical and economic challenges

- We've become a "value added" process !!!!

- We all have our work cut out for us

#### Thanks for listening